国際特許分類[H03L7/081]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 付加的な制御移相器を有するもの (308)

国際特許分類[H03L7/081]に分類される特許

101 - 110 / 308

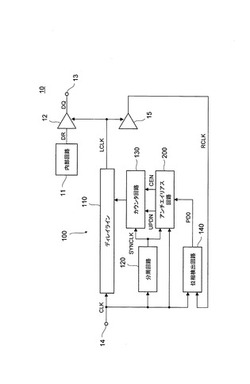

DLL回路及びこれを備える半導体装置

【課題】エイリアシングによるエイリアシングによる誤動作の発生が防止されたDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を設定するカウンタ回路130と、外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相検出回路140と、外部クロック信号CLKに含まれるジッタ成分が所定の周波数以上であることに応答して、位相判定信号PDに基づいたカウンタ回路130のカウント値の更新を禁止するアンチエイリアス回路200とを備える。これにより、エイリアシングによる誤動作によって内部クロック信号LCLKが誤った方向に連続制御されるという問題がなくなる。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

DLL回路、PLL回路

【課題】ロックイン時間を短縮しつつチャージポンプ回路の誤差電流に起因するジッタを低減する。

【解決手段】チャージポンプ回路30は、位相比較回路20による比較結果(充電信号UP0,放電信号DN0)に応答して正または負の出力電流Ioutを出力する。電流制御回路11は、遅延クロックCK(n)の遷移エッジを含む有効期間中に遅延クロックCK(1)の遷移エッジが発生することを検出し、その検出結果に応じてチャージポンプ回路30の出力電流Ioutの電流量を制御する。

(もっと読む)

DLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法

【課題】本発明は、アップデート条件を緩和させて効率的なアップデートを行い、位相比較感知結果値が不規則に変化しても内部クロックの位相をより正確に制御することができるDLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法を提供する。

【解決手段】本発明のDLL(Delay Locked Loop)回路は、基準クロックとフィードバッククロックの位相を比較感知して位相感知信号を生成する位相感知手段;前記基準クロックに応答して前記位相感知信号が有する第1論理値と第2論理値の個数の差を判別して有効区間信号とアップデート制御信号を生成するアップデート制御装置;及び前記有効区間信号のイネーブル時に前記アップデート制御信号に応答して遅延ラインに付与する遅延値をアップデートするシフトレジスタ;を備える。

(もっと読む)

遅延制御方法および遅延装置

【課題】遅延装置の回路規模を抑制する。

【解決手段】DLL回路120は、遅延素子122に入力された基準クロックが遅延素子122により1周期分遅延されるように遅延素子122を制御する第1の制御信号CTR1を生成する。遅延素子140は、遅延素子122と同一の構成を有し、外部からのストローブ信号S1を、第2の制御信号CTR2に応じた遅延量の分だけ遅延させる。ストローブ遅延制御回路130は、第1の制御信号CTR1と、遅延素子140による遅延量の期待値とから、遅延素子140に出力する第2の制御信号CTR2を生成する。クロック供給回路110は、遅延素子140に入力されるストローブ信号S1の周波数より高い周波数を有する基準クロックをDLL回路に供する。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

遅延クロック発生装置

【課題】多数段の遅延ステップで遅延時間を選択可能としながら、遅延ステップの直線性を確保し得る遅延クロック発生装置を提供する。

【解決手段】複数種類の遅延クロック信号を発生させる遅延クロック発生装置において、平行して配置された複数列の遅延素子列16a〜16dと、遅延素子列を構成する各遅延素子に設けられ、クロック信号CLKを往復方向に転送する往路側及び復路側転送線と、各遅延素子にそれぞれ設けられ、前後に連なる遅延素子の往路側転送線同士と復路側転送線同士を接続する第一の転送経路と、各遅延素子の往路側転送線と復路側転送線とを接続する第二の転送経路を選択する選択回路と、入力コードicodeに基づいて遅延素子列のいずれか一つの遅延素子でのみ選択回路で第二の転送経路を選択させるデコーダー12,13,14を備えた。

(もっと読む)

DLL回路とその制御方法

【課題】安定的にジッタを低減する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路12を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路12における遅延量を制御する。位相比較結果判定回路15は、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果を所定の期間に亘って積算し、積算結果の分布に基づいて遅延量を制御する。

(もっと読む)

位相補間制御装置

【課題】位相補間制御装置中のノイズフィルタ帯域幅を動的に調整し、位相補間制御装置を広く応用することができる上、CDRのロック時間を短縮させることができる位相補間制御装置を提供する。

【解決手段】位相補間制御装置400は、第1の信号と第2の信号との位相関係を表す指示を受信し、複数の双方向シフトレジスタを含む。複数の双方向シフトレジスタは、互いに直列接続され、位相補間制御装置が受信した指示が、第1の信号の位相が第2の信号の位相より進んでいることを表すとき、直列接続された複数の双方向シフトレジスタをそのうちの1方向でシフトさせる。位相補間制御装置400が受信した指示が、第1の信号の位相が第2の信号の位相より遅れていることを表すとき、直列接続された複数の双方向シフトレジスタを他の方向でシフトさせる。

(もっと読む)

高周波発振器

【課題】周囲の環境温度による光ファイバの熱伸縮に対してもPLL制御を正常に行うことができる高周波発振器を得る。

【解決手段】レーザ光源が発生したレーザ光を光変調器により変調し、光ファイバを介して伝送した変調後のレーザ光を光電変換器により高周波信号に変換し、変換後の高周波信号からバンドパスフィルタにより所定の通過帯域成分を取り出し、当該所定の通過帯域成分の高周波信号の周波数を変調信号として前記光変調器に帰還すると共に発振信号として出力する高周波発振器において、高周波信号の周波数が一定になるように制御するPLL制御手段と、当該高周波発振器の発振周波数の変動をPLL制御手段の予め設定した周波数引き込み範囲内に納めるように高周波信号の位相を調整する位相調整手段を備えた。

(もっと読む)

101 - 110 / 308

[ Back to top ]