国際特許分類[H03L7/081]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 付加的な制御移相器を有するもの (308)

国際特許分類[H03L7/081]に分類される特許

41 - 50 / 308

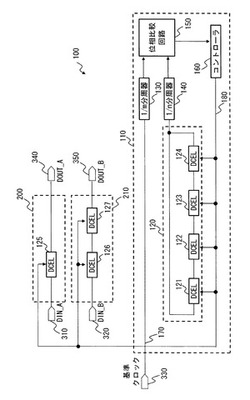

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

半導体回路

【課題】DCC回路を備えたDLL回路の消費電力を低減させる。

【解決手段】制御信号DCCENに基づいて活性化・非活性化が制御されるデューティ変更検出回路21であって、入力されたクロック信号に基づいて生成されたクロック信号のデューティとあらかじめ設定されたデューティとを比較しその結果を出力するデューティ変更検出回路21と、デューティ変更検出回路の出力が生成されたクロック信号のデューティがあらかじめ設定されたデューティである目標値近傍にあることを示すときにはデューティ変更検出回路21を非活性化する制御信号DCCENを出力すると共に目標値近傍に無いときにはデューティ変更検出回路21を活性化する制御信号DCCENを出力するデューティ判定回路23とを備える。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

DLL回路およびそれに使用されるレプリカ回路

【課題】 レイアウト的な制限がないDLL回路を提供すること。

【解決手段】 DLL回路に使用されるレプリカ回路は、第1の電源電圧が供給され、クロックバッファへの入力クロック信号が入力され、レプリカクロック信号を出力する遅延回路を含む。遅延回路は、第1乃至第MのCMOSインバータ回路および第(M+1)乃至第NのCMOSインバータ回路が縦続接続された回路である。複数のトランジスタは、遅延回路の後段側の第(M+1)乃至第NのCMOSインバータ回路のnチャネルMOSトランジスタのソースにそれぞれ接続されている。ローパスフィルタ回路は、第1の電源電圧と異なる第2の電源電圧を低域通過濾波して、その低域濾波した電源電圧を複数のトランジスタの制御端子へ供給する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

41 - 50 / 308

[ Back to top ]