国際特許分類[H03L7/095]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ロック検出器を用いるもの (172)

国際特許分類[H03L7/095]に分類される特許

91 - 100 / 172

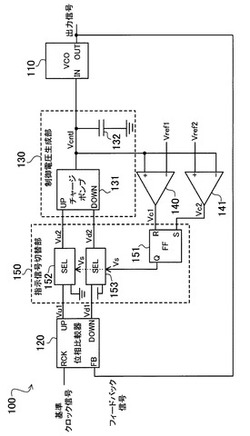

PLL回路

【課題】簡単に暴走状態から正常動作に復帰可能なPLL回路を提供する。

【解決手段】比較部140により制御電圧Vcntlが上限電圧値Vref1を超えたことが検出されると、指示信号切替部150は制御電圧Vcntlを強制的に下降させる他の指示信号(グランド電圧を指示信号Vu2、電源電圧を指示信号Vd2)を制御電圧生成部130に供給し、制御電圧生成部130は制御電圧Vcntlを下降させる。そして、比較部141により制御電圧Vcntlが下限電圧値Vref2を下回ったことが検出されると、指示信号切替部150は制御電圧生成部130への供給を他の指示信号から位相比較器からの指示信号(アップ信号Vu1、ダウン信号Vd1)に切り替え、制御電圧生成部130は指示信号に応じて制御電圧Vcntlを生成する。電圧制御発振回路110は、制御電圧Vcntlに応じて発振周波数を制御する。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報を元に得られるAGC回路における補正値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

データ駆動回路及び遅延固定ループ回路

【課題】アナログデータ信号のディスプレイパネルへの印加時に発生する誤りなどにも関わらず正常に動作可能なデータ駆動回路及び遅延固定ループ回路を提供する。

【解決手段】第1のデータ信号を第2のクロック信号に基づいてサンプリングし、アナログ変換することにより得られた第2のデータ信号を出力するデータ駆動部と、第2のデータ信号の変化開始時点から所定期間内であることを知らせるマスク信号を生成するマスク信号生成部と、第1のクロック信号から第2のクロック信号−第1のクロック信号と第2のクロック信号の間には遅延が存在し、該遅延は前記第1のクロック信号と第2のクロック信号の間の位相差に応じて変化し、位相差に応じる前記遅延の変化は前記マスク信号により遮断される−を生成する遅延固定ループと、を備える。

(もっと読む)

拡張されたトラッキング範囲を有する位相ロック・ループ(PLL)

PLLのトラッキング範囲を拡張するための方法は、それに関連する第1の幅を有する、PLLの初期トラッキング・ウィンドウを確立するステップと、PLLに供給された入力信号の周波数がトラッキング・ウィンドウ外にあるとき、第1の幅よりも大きい、それに関連する第2の幅を有する拡張されたトラッキング範囲内にPLLのトラッキング・ウィンドウを動的に調整するステップとを含む。  (もっと読む)

(もっと読む)

ジッタ検出回路及び半導体装置

【課題】サイクルトゥサイクルジッタの程度を検出する。

【解決手段】PLL回路(2)の発振クロック信号(vco)の遅延信信号を基準クロック信号(ref)の複数の遅延信号の変化に同期して複数のラッチ回路(23_1〜23_n)にラッチする。ラッチ回路毎にその出力又はその反転信号をセレクタ(24_1〜24_n)で選択する。セレクタ毎にその出力の変化回数をカウンタ(25_1〜25_n)で計数する。制御回路(28)は、発振クロック信号の2nサイクル毎に、前回のセレクタの選択が非反転出力であれば今回カウンタの計数値がn以上のときセレクタの選択状態を反転し、前回のセレクタの選択が反転出力であれば今回前記カウンタの計数値がn以上のときにセレクタの選択状態を反転する。前記第1カウンタの計数値が例えばジッタ検出情報として出力される。

(もっと読む)

高速シリアルインターフェース回路及び電子機器

【課題】トランジスタの経時変化による信頼性の劣化等を防止できる高速シリアルインターフェース回路及びこれを含む電子機器を提供すること。

【解決手段】高速シリアルインターフェース回路は、データレシーバ回路10、クロックレシーバ回路20、シリアル/パラレル変換回路40を少なくとも有するロジック回路ブロック30、自走クロック生成回路70、クロック検出回路80を含む。クロック検出回路80は、差動クロック信号線を介してクロックが転送されているか否かを検出する。クロックレシーバ回路20は、自走クロック生成回路70から自走クロックOSCKを受け、差動クロック信号線を介してクロックが転送されていないことが検出された場合には受信クロックCKINの代わりに自走クロックOSCKをロジック回路ブロック30に出力する。

(もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

クロック信号生成回路とクロック信号生成方法

【課題】複数系統の基準信号のいずれか、又は全てが断となってしまった場合でも、安定してクロック信号を生成することができるようにする。

【解決手段】断検出部2−A,2−Bで現用系の基準信号Aと予備系の基準信号Bの断を検出するようにし、断検出時には断検出信号を制御部8へ出力する。制御部8は、断検出部2−Aからの断検出信号を受け取ると、入力切替部1の導出を基準信号Bに切り替え、その後、断検出部2−Bからの断検出信号を通知されると、制御電圧保持部6の保持電圧の更新を停止させ、切替部7の導出を制御電圧生成部5で生成される制御電圧から制御電圧保持部6に保持される保持電圧に切り替える。

(もっと読む)

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

91 - 100 / 172

[ Back to top ]