国際特許分類[H03L7/095]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ロック検出器を用いるもの (172)

国際特許分類[H03L7/095]に分類される特許

121 - 130 / 172

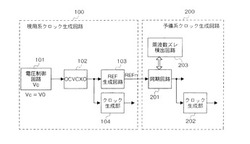

クロック生成回路

【課題】クロック源となる発振器の経年変化によって生じた周波数変動を定期的な保守時に周波数測定を行うことなく検出する。

【解決手段】制御電圧によって制御されるOCVCXO102の出力に応じたクロック信号を生成する現用系クロック生成回路100と、OCVCXO102の出力を用いて生成されたリファレンス信号REFnを用いて現用系クロック生成回路100と同期するように決定される制御電圧によって制御されるOCVCXOの出力に応じたクロック信号を生成する予備系クロック生成回路200とからなり、制御電圧の値を監視することにより、OCVCXO102における周波数変動を検出する。

(もっと読む)

アンロック検出回路及びクロック発生システム

【課題】アンロックを検出する位相差を制御し任意の感度でアンロックの検出を行う。

【解決手段】PLLのアンロック状態を検出するアンロック検出回路に、PLLへの基準信号、PLLからのフィードバック信号のデューティ比を調整する1対のデューティ調整回路111,112と、デューティ調整回路からデューティ調整後の基準信号、フィードバック信号をクロック信号として論理値を記憶する第1のフリップフロップ回路121,122と、第1のフリップフロップ回路の出力信号の論理積を取り記憶した論理値をリセットするAND回路123と、デューティ調整回路からデューティ調整後の基準信号、フィードバック信号を反転しクロック信号として第1のフリップフロップ回路の出力信号をサンプリングし論理値として記憶する第2のフリップフロップ回路124,125と、第2のフリップフロップ回路の出力信号の論理和をとりアンロック信号として出力するOR回路126とを備える。

(もっと読む)

周波数安定化回路

【課題】発振器の特性による周波数偏差によらず確実に周波数引き込みを行えるようにした周波数安定化回路を提供すること。

【解決手段】検出器11を設けて基準信号の有無を検出し、基準信号が無ければPLL回路がロックされていないとしてサーチ回路12に指示を与え、電圧制御型発振器8(VC−TCXO)のコントロール電圧を制御して周期的に変化させる。すなわち、電圧制御型発振器8の出力周波数を例えば数秒周期でサーチ(周波数を変化)させるようにする。これにより抽出されたパイロット信号の帯域も変化し、例えば数秒以内で抽出用の帯域フィルタ5,6の帯域内に入ってくるようになる。従って基準信号が確実に生成され、PLL回路がLOCKする。これにより高額なOCXOから安価なVC−TCXOに置き換えることができ、システムの低価格化を実現できる。

(もっと読む)

位相同期ループ回路及びこの位相同期ループ回路の制御方法

【課題】電圧制御水晶発振器の経年変化による異常が発生しても、この異常を確実に検出できるようにした位相同期ループ回路を提供する。

【解決手段】カウンタ111にて外部クロック信号から内部クロック信号に同期した矩形波信号を生成するとともに、カウンタ112−2にて内部クロック信号から外部クロック信号の異常を検出するために必要なウインドウ信号W1を生成し、カウンタ115にて内部クロック信号から電圧制御水晶発振器12の異常を検出するために必要なウインドウ信号W2を生成し、異常判定制御部114−2にて矩形波信号の立ち上がりがウインドウ信号W1,W2のハイレベル期間内に入っているか否かを判定し、ウインドウ信号W1のハイレベル期間に入っていて、ウインドウ信号W2のハイレベル期間内に入っていない場合に、電圧制御水晶発振器12の異常と判定するようにしている。

(もっと読む)

位相同期ループ回路及びこの位相同期ループ回路で使用される制御方法

【課題】基準クロックに異常が発生しても、この異常に対処し得る位相同期ループ回路を提供する。

【解決手段】カウンタ111にて外部クロック信号から内部クロック信号に同期した矩形波信号を生成するとともに、カウンタ112−2にて内部クロック信号から外部クロック信号の異常を検出するために必要なウインドウ信号を生成し、異常判定制御部114−2にて矩形波信号の立ち上がりがウインドウ信号のハイレベル期間内に入っているか否かを判定し、入っていない場合に、矩形波信号の立ち上がりがウインドウ信号のハイレベル期間内に入るようにカウンタ111を制御すると共に、スイッチ13のオン/オフを制御して、電圧制御水晶発振器12への制御電圧の供給を制御するようにしている。

(もっと読む)

位相同期回路

【課題】簡単な構成により高精度な発振位相(周波数)で同期発振と自走発振の切り替え制御を可能とし、正常な同期発振状態及び自走発振状態でアラームを発生しないアラーム回路を備える位相同期回路を提供する。

【解決手段】電圧制御発振器6の出力と同期クロックとの位相を比較する位相比較器2に供給電源をオンオフする電源制御回路10を設けるとともに、ループフィルタ4の出力に電圧制御発振器6の自走発振用の電圧を印加する電圧発生回路8を備える。電源制御回路10の電源のオンオフ制御により電圧制御発振器6の同期発振と自走発振の切り替えが可能である。また位相比較器2の出力に閾値により異常を検出するアラーム回路の3を備える。位相同期動作の異常時にアラーム回路3はアラームを出力するが、前記電源制御回路10で電源供給をオフ状態に切り替え、電圧制御発振器を自走発振の動作にするとアラームはノーマルに戻る。

(もっと読む)

半導体装置

【課題】スプリアス成分を低減させることが可能な半導体装置を提供することを目的とする。

【解決手段】位相周波数検出器PD、チャージポンプCP、ループフィルタLF、電圧制御発振器VCO、分周器PD1とを有する位相ロックループ回路と、位相比較を行うタイミングをマスクするマスク信号を生成するマスク信号発生器MG1と、ロック状態を検出してロック検出信号を出力するロック検出器LD1と、ロック状態においてマスク信号を通過させる論理回路ANと、ループフィルタの出力端子と電圧制御発振器の入力端子との間に設けられマスク信号に基づいてオン、オフが制御されるスイッチング素子SWとを備え、ロック状態でかつ位相比較時に制御電圧が電圧制御発振器に与えられないようにループフィルタと電圧制御発振器との間が分離されることを特徴とする半導体装置。

(もっと読む)

PLL回路

【課題】直列接続されたPLL回路について、特にリセット時や電源投入時における異常なクロック信号の発生を抑制する。

【解決手段】直列接続された二つのPLL回路(10A,20)からなるPLL回路において、前段のPLL回路(10A)は、出力クロック信号を生成する電圧制御発振器(104)、及び電圧制御発振器(104)に入力される制御電圧が所定の範囲にあるか否かを検出し、当該検出結果を示す検出信号を出力する制御電圧検出回路(106)を備えている。後段のPLL回路(20)は、前段のPLL回路(10A)から出力された検出信号が第1の論理レベルのとき、停止する一方、当該検出信号が第2の論理レベルのとき、動作する。

(もっと読む)

フェーズロックループ発振器

【課題】フェーズロックループ発振器のロック検出手段において、そのロック検出感度が小さいものであっても、あるいは周波数収束までの時間が大きくばらつくものにおいても、目的とする周波数偏差に収束した時点で、直ちにその状態を正確に検出することを可能とする。

【解決手段】電圧制御発振器1と、位相比較器2と、低域フィルタ3とをループ状に接続したフェーズロックループ発振器において、前記低域フィルタの出力を増幅する交流信号増幅器7と、その増幅した信号の振幅信号値を検出する検波器8と、該検波した信号の値と予め設定した閾値とを比較するコンパレータ9と、該コンパレータの出力信号に基づいてロック信号を発生するロック検出器10を備える。

(もっと読む)

遅延ロックループ回路、タイミング発生器、半導体試験装置、半導体集積回路及び遅延量校正方法

【課題】 遅延量の測定に代わる手法で、カウンタの初期設定値を決めて、遅延回路の校正にかかる時間を短縮可能とする。

【解決手段】 複数のカウンタ設定値の中から一つのカウンタ設定値がロードされ、遅延ロックループ回路10−1がロックモードに切り替えられ、サイクルスリップ検出回路20−1の順序回路22がリセットされ、その後、順序回路22から出力されるサイクルスリップ検出信号が読み込まれると、このサイクルスリップ検出信号にもとづき、遅延回路11の出力信号がサイクルスリップを起こしているか否かが判定され、起こしているときはカウンタ設定値が切り替えられ、一方起こしていないときは、ロックされて完了する。

(もっと読む)

121 - 130 / 172

[ Back to top ]