国際特許分類[H03L7/095]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ロック検出器を用いるもの (172)

国際特許分類[H03L7/095]に分類される特許

161 - 170 / 172

PLL回路、受信チューナ、通信機器、PLL回路のロック検出方法

【課題】本発明は、小型かつ低雑音でありながら、そのロック/アンロックを検出して高精度のフィードバックループ制御を行うことが可能なPLL回路の提供を目的とする。

【解決手段】本発明に係るPLL回路1は、基準信号発生器11と、分周器12と、位相比較器13と、チャージポンプ14と、ループフィルタ15と、VCO16と、PLLがロック状態であるか否かを検出するロック検出器17と、を有して成るPLL回路であって、チャージポンプ14は、入力される位相差信号に応じてその駆動電流が変動する構成とされており、ロック検出器17は、チャージポンプ14の駆動電流変動を検出してPLLがロック状態であるか否かを検出する構成とされている。

(もっと読む)

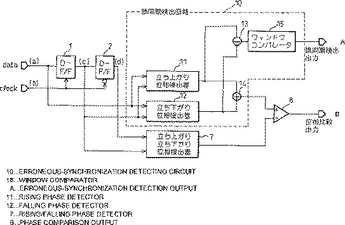

位相誤同期検出回路

位相比較回路に関し、特にデータとクロックとの位相差の比較において、データのデューティが100パーセントからずれたときに生じる位相の誤同期を検出する位相誤同期検出回路を提供する。データとクロックとの位相差を検出する位相比較器において、その位相誤同期検出回路は、データの立ち上がりとクロック位相との位相差を検出してその平均位相差を出力する第1の位相検出部と、データの立ち下がりとクロック位相との位相差を検出してその平均位相差を出力する第2の位相検出部と、前記第1の位相検出部からの平均位相差と前記第2の位相検出部からの平均位相差との差が所定の範囲を超えるときに位相誤同期と判定する位相誤同期判定部と、により構成する。  (もっと読む)

(もっと読む)

位相同期ループ回路

【課題】 ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】 PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

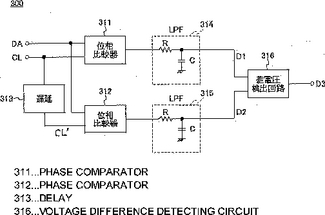

位相比較利得検出回路、誤同期検出回路及びPLL回路

PLLの位相比較利得検出回路において、データ信号DAとクロック信号CLとの間の位相を比較すると共に、データ信号DAとクロック信号CLを所定の遅延量だけ遅延したクロック信号CL’との間の位相を比較し、それぞれの位相比較結果どうしの差と上記所定の遅延量とに基づいて位相比較利得を検出する位相比較利得検出回路。  (もっと読む)

(もっと読む)

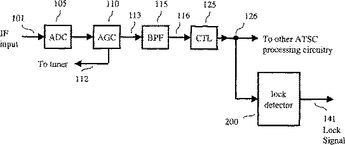

搬送波トラッキング・ループ・ロック検出器

ATSC(次世代TVシステム委員会)VSB(残留側波帯)受信機(15)は、受信したATSC‐VSB信号を処理する搬送波トラッキング・ループ(CTL)115と、CTLロック検出器(200)を具える。CTLロック検出器は、受信されダウンコンバートされたATSC‐VSB信号を平均化してDCオフセットを発生する平均化フィルタ(135)、DCオフセットを推定する推定器(130)、およびDCオフセットの推定値とDCオフセットとの比較の関数としてロック信号を発生する比較器(140)を具える。ロック信号は、CTLのロックされた状態またはアンロックされた状態の何れかを表す。  (もっと読む)

(もっと読む)

PLLクロック出力安定化回路

【課題】源振クロックで所定サイクル毎に周波数を測定することで、PLL回路が安定したことをLSI内部等で検査可能にする。

【解決手段】PLLクロック出力安定化回路は、基準クロックclkを固定又は可変の逓倍数Nで逓倍してPLLクロックpll_clkを出力するPLL回路10と、一定期間の間、前記PLLクロックpll_clkでカウントアップするカウンタ17と、カウンタ17のカウント値と固定又は可変の逓倍数Nとを比較する比較回路18と、一定期間の間、比較回路18の比較値の等しい状態が続いた回数だけカウントアップするカウンタ20と、カウンタ20のカウント値が安定待ち回数kに達したときに出力イネーブル信号enableを生成し、出力イネーブル信号enableにより、PLLクロックpll_clkを遮断していたゲート回路25を開いてPLLクロックpll_clkを通過させる出力手段とを備えている。

(もっと読む)

PLL回路、PLL回路の位相調整方法

【課題】 Transient Wander成分(入力位相跳躍成分)のみを自動検出し、出力位相を入力位相変動前の位相に立て直す。

【解決手段】 Phase build-out Detector部300は、PLL部100の入力位相を監視し、Transient Wander成分(入力位相跳躍成分)とCycle Wander成分(周期的な位相雑音成分)を同時に検出し、Transient Wander成分のみが検出された場合に、Phase build-out Actuator部200でPLL部のPhase Detector部101、Digital Amp1部102及びDigital Filter部103をリセットし、出力位相を入力位相変動前の位相に立て直す。このとき、同時に検出されるCycle Wander成分に対しては位相の立て直しを行わない。

(もっと読む)

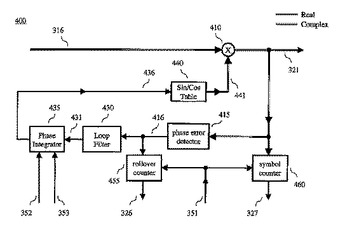

通信システムにおける搬送波再生で使われる方法および装置

受信機が搬送波再生を実行するためのデジタル式位相ロックループ(PLL)を含む。デジタル式PLLさらに硬判定によって駆動される位相誤差推定器と、該位相誤差推定器によって提供される位相誤差信号を累積する積分器とを含んでいる。引き込み時間を減らすため、デジタル式PLLは、搬送波周波数オフセットの推定が位相誤差信号の関数として決定される開ループモードで走らされる。搬送波周波数オフセットの推定値が決定されたあとは、決定された推定値が積分器に事前にロードされて、デジタル式PLLは閉ループモードで走らされる。

(もっと読む)

(もっと読む)

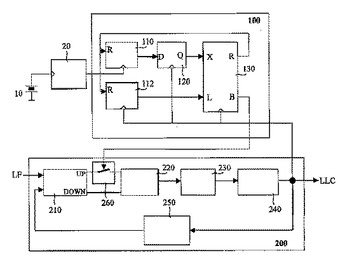

PLL回路

本発明は、位相又は周波数検出回路(210)の出力信号に応じて制御される発振回路(240)を有する位相同期ループ装置に関し、切替制御手段(130)は、所定の閾値周波数が供給される第1のタイマ手段(110)及び発振回路(240)の出力周波数が供給される第2のタイマ手段(112)の出力に応答して遮断信号を発生するように設けられる。遮断信号に基づいて、遮断手段(260)は、発振回路(240)への出力信号の供給を抑制する。これにより、PLL装置の出力周波数は、周波数閾値を超えて変化することが回避可能となるとともに、唯1つのPLL回路だけで済むことになる。

(もっと読む)

(もっと読む)

テスト回路

【課題】オシロスコープ等の外部測定機器に頼らなければ求められなかったPLLのロック判定及びロック所要時間を容易に算出できるテスト回路をマイクロプロセッサに付加することにより、高性能/低電力情報機器の設計時の設計品質向上を図る半導体集積回路の提供。

【解決手段】PLLに入力する基準クロック、PLLの出力クロックにそれぞれ同期してカウント値を更新する第1、第2のカウンタ、第1、第2のカウンタが出力するカウント値の差を演算する減算器、減算器の減算結果出力を基準クロックに同期し過去複数クロック分記憶し、記憶されている複数の減算結果の値が全て同一であるか否かを判定し、同一であればカウント値一致信号(MATCH信号)を出力する減算結果格納メモリ、を有する。ロックと判定された際のカウント値を出力することにより、PLLがロックするまでに心要なサイクル数を算出できる。

(もっと読む)

161 - 170 / 172

[ Back to top ]