国際特許分類[H03L7/183]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528) | ループの中に分周器または計数器を用いるもの (427) | ループをロックするために時間差を用いるもの,一定数値間計数器または一定数値で分周する分周器 (173)

国際特許分類[H03L7/183]の下位に属する分類

ループ中にミキサーを用いるもの

ループ中の電圧制御発振器を粗同調するための手段を用いるもの (39)

時間差を決定するために分周器または計数器から少なくとも2つの異なる信号を用いるもの

互換性のある前置分周器からなる分周器または計数器,例.2モジュール分周器

ループ中の計数器が2つの異なった非零数値間を計数するもの,例.オフセット周波数を発生するためのもの

国際特許分類[H03L7/183]に分類される特許

1 - 10 / 134

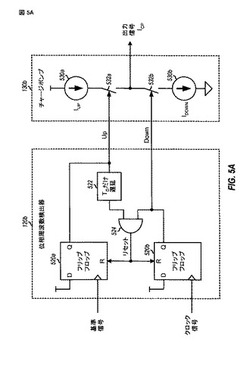

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

周波数シンセサイザ

【課題】少数点逓倍の精度を向上させ、累積ジッタを低減した周波数シンセサイザを提供する。

【解決手段】位相比較器1と、チャージポンプ2と、ローパスフィルタ3と、電圧制御発振器4と、該電圧制御発振器の出力クロック信号を小数点分周して前記帰還クロック信号を生成する帰還回路とを備える。帰還回路は、電圧制御発振器4の出力クロック信号を分周する可変分周器5と、電圧制御発振器4の8相のクロック信号から1つの位相のクロック信号を選択するマルチプレクサ7と、マルチプレクサ7で選択した特定の位相のクロック信号により可変分周器5のクロック信号をリタイミングするリタイミング回路(DFF回路8,9とアンド回路10)とを備える。

(もっと読む)

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

半導体集積回路

【課題】単一の回路仕様で世界各国の衛星放送に簡便に対応できる、LNB用半導体集積回路を実現する。

【解決手段】半導体集積回路100の所定の端子電圧を設定することで、PLL回路108の可変分周器110の分周比を設定し、所望の局部発振周波数を得る。供給される直流電位に対応して可変分周器の分周比を制御する第1の分周比設定部と、供給されるパルス信号の有無に対応して可変分周器の分周比を制御する第2の分周比設定部とを備え、第1の分周比設定部または第2の分周比設定部による可変分周器の分周比制御により、局部発振器109の発振周波数を所望の周波数に設定する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

デルタシグマ変調型分数分周PLL周波数シンセサイザおよびそれを備えた無線通信装置

【課題】デルタシグマ変調型分数分周PLL周波数シンセサイザにおいて、スプリアスを抑制し、さらに、位相雑音特性を良好に保つ。

【解決手段】分周器(25)を変調することで分数分周を行うデルタシグマ変調型分数分周PLL周波数シンセサイザは、分数部データKに加算すべきシフト量Sを求め、シフト量Sと、シフト後分数部データK2とをそれぞれ出力する演算処理手段(27)と、シフト後分数部データK2を積分して量子化する第1のデルタシグマ変調器(28)と、シフト量Sを積分して量子化する第2のデルタシグマ変調器(29)と、第1のデルタシグマ変調器(28)の出力系列と第2のデルタシグマ変調器(29)の符号反転出力とを加算する第1の加算器(30)と、整数部データMと第1の加算器(30)の出力とを加算する第2の加算器(31)とを備え、第2の加算器(31)の出力により分周器(25)を変調させる。

(もっと読む)

1 - 10 / 134

[ Back to top ]