国際特許分類[H05K1/18]の内容

電気 (1,674,590) | 他に分類されない電気技術 (122,472) | 印刷回路;電気装置の箱体または構造的細部,電気部品の組立体の製造 (64,965) | 印刷回路 (15,851) | 印刷によらない電気部品と構造的に結合した印刷回路 (1,927)

国際特許分類[H05K1/18]に分類される特許

131 - 140 / 1,927

電子制御装置

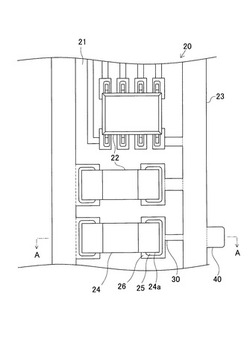

【課題】高密度化された基板面に設けられる遮断配線にて生じた熱による他の電子部品への影響を抑制し得る電子制御装置を提供する。

【解決手段】電源配線23には、遮断配線30に接続されるセラミックコンデンサ24を除く他の複数の電子部品22よりも当該遮断配線30に対して配線距離が短くなる位置に当該電源配線23と同一材料からなる放熱配線40が形成される。この放熱配線40は、電源配線23を介して伝わる熱を放熱するために、その放熱面積を大きくするように形成されている。

(もっと読む)

基板装置

【課題】固定用の穴を開けることなく部品を固定する。

【解決手段】基板装置Aは、プリント基板1にFFCガイド部品3が実装された基板装置であって、プリント基板1上に取り付けられたジャンパー線2と、爪部3fが設けられたFFCガイド部品3とを具備し、爪部3fがジャンパー線2に係合することでFFCガイド部品3がプリント基板1に固定される。

(もっと読む)

表面実装部品及び製造方法

【課題】実装時の基板の反りに対する受容性を高くし、コネクタのコプラナリティ管理を容易にし、半田付け不良の発生を抑制することができる表面実装部品を提供すること。

【解決手段】本発明による表面実装部品Cは、本体部2aと脚部2bを有する複数のリード2と、脚部2bの電気的な接続面2baに頂部を有して形成される半田溜まり部3と、半田溜まり部3を形成する半田のリードに沿う拡散を防止する拡散防止部2cを含む、ことを特徴とする。

(もっと読む)

表示装置

【課題】 回路基板とハウジングとの熱膨張率の違いにより、表示素子と回路基板との電気的な接続が断たれる虞を低減できる。

【解決手段】 表示素子10,20は、リード端子12,22,13を有する。回路基板30は、リード端子12,22,13と電気的に接続される。ハウジング40は、表示素子10,20を収容する。リード案内部50,60は、リード端子12,22,13を挿通する貫通孔52,62を有する。ハウジング40は、回路基板30に位置決めされる第一の位置決め部43を有する。リード案内部50,60は、回路基板30に位置決めされる第二の位置決め部51,61と、ハウジング40と連結される弾性支持部53,63と、を有する。

(もっと読む)

半導体装置および半導体装置実装体

【課題】複数の差動信号を伝送する半導体装置の信頼性低下を抑制する。

【解決手段】複数の差動信号を伝送する複数のランド(第1外部端子)LDp1を含む複数のランド(外部端子)LDpが、配線基板12の裏面12bに行列状の配列パターンで配置されたエリアアレイ型の半導体装置10を以下の構成とする。複数のランドLDp1の一部は、配列パターンの最外周に配置される。また、複数のランドLDp1の他の一部は、配線基板12の裏面12bにおいて、配列パターンの最外周よりも内側で、かつ、最外周の隣の列に配置される。ここで、最外周の隣の列に配置されるランドLDp1と、配線基板12の側面の間の第2領域R2では、複数のランドLDpの配置間隔が、最外周の第1領域R1よりも広くなっている。

(もっと読む)

電子装置

【課題】回路基板に電子部品をはんだ実装してなる電子装置において、回路基板とこの回路基板にはんだ接合された電子部品との両者の膨張・収縮度合の差をより小さくすることで、はんだへの応力を低減させる。

【解決手段】回路基板10の方が電子部品20よりも線膨張係数が大きいものであり、電子部品20は、第1の電極21、第2の電極22にてそれぞれ、回路基板10にはんだ30を介して固定されており、回路基板10のうち第1の電極21との固定部と、第2の電極22との固定部との間に位置する部位である固定部間部位13は、一面11に貫通穴14が設けられることにより、回路基板10のうち固定部間部位13以外の部位よりも熱膨張および熱収縮の度合が小さくなっている。

(もっと読む)

回路実装基板の製造方法およびプリント基板

【課題】電気部品を基板に実装する際に、電気部品に加えられる熱を低減するとともに、製造コストの増大を防ぐことが可能な回路実装基板の製造方法およびプリント基板を提供する。

【解決手段】回路実装基板201の製造方法は、対象部品11を半田付けするための第1のランド21,22と、対象部品11と比べて耐熱性の高い非対象部品12,71を半田付けするための第2のランド23,24,72,73とを備え、第1のランド21,22の面積が、各第2のランド23,24,72,73のうち、配線パターン74,75に覆われない第2のランド23,24の面積と比べて大きいプリント基板101を準備するステップと、第1のランド21,22を用いて対象部品11をプリント基板101に半田付けするステップとを含む。

(もっと読む)

実装方法

【課題】回路基板の実装面に設けられた実装用ランドの面積を大きくせずとも、十分な量のはんだペーストを供給して、電子部品と回路基板との間のはんだ不足による接続不良を低減することのできる技術を提供する。

【解決手段】電子部品の複数のバンプ接続用はんだボール電極にはんだペーストを転写により塗布すると共に、実装面1aの凹んでいる部分や、内部電極パターン5の積層方向における配線密度が小さく回路基板1の厚みが薄くなって窪みが生じるおそれのある部分、回路基板1または電子部品の反りにより回路基板1および電子部品間の間隔が大きい位置に設けられた実装用ランド2に、はんだペーストを塗布することにより、回路基板1の実装用ランド2の面積を大きくせずとも十分な量のはんだペーストを供給して、電子部品と回路基板1との間のはんだ不足による接続不良を低減することができる。

(もっと読む)

電子部品及び基板モジュール

【課題】低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【解決手段】積層体11は、コンデンサを形成している容量導体18,19及び内部導体32を内蔵している。外部電極12a,12bはそれぞれ、容量導体18,19に引き出し導体20,21を介して接続されている。内部導体32は、容量導体18,19に対向している。外部電極13,14は、引き出し導体22,23を介して容量導体18に接続されている。外部電極15,16は、引き出し導体24,25を介して容量導体19に接続されている。

(もっと読む)

電力用半導体装置、プリント配線板およびそれらの接続機構

【課題】電力用半導体装置とプリント配線板との接続において、接続信頼性の向上、電力損失の低減、製造コストの削減、接続工程の簡略化および接続構造の小型化を図る。

【解決手段】パワー半導体装置1は、プリント配線板3との対向面に突出した外部端子である導電性の嵌入部材2を備える。プリント配線板3は、パッド部31上に実装され、パワー半導体装置1が当該プリント配線板3に接続されるときに嵌入部材2が挿入される導電性の嵌合部材4を備える。嵌入部材2は、側面に凹部21を有し、嵌合部材4は、内側面に弾性を有する凸部41を有する。嵌入部材2が嵌合部材4に挿入されたとき、嵌入部材2の凸部41が弾性により嵌合部材4の凹部21に圧接する。

(もっと読む)

131 - 140 / 1,927

[ Back to top ]