太陽誘電株式会社により出願された特許

121 - 130 / 964

電気化学デバイス

【課題】ケースのリングに対してリッドが位置ずれ無く結合された電気化学デバイスを提供する。

【解決手段】電気化学デバイス10において、リッド12は該リッド12に一体形成された環状部12aの内周面12a1がリング18の外周面18bに密着するように焼き嵌めされており、環状部12aが位置決め手段として機能していることも相俟って該リッド12がケース11のリング18に対して位置ずれ無く結合されている。

(もっと読む)

印刷用マスクの製造方法

【課題】印刷パターンに対応した金属膜パターンをメッシュに接合するときに該金属膜パターンに生じる変形を防止できる印刷用マスクの製造方法を提供する。

【解決手段】印刷パターンに対応した金属膜パターン13をメッシュ22に接合して構成された印刷用マスクの製造方法において、金属膜パターン13とメッシュ22との接合を、台板11の上面に形成された金属膜パターン13上にメッシュ22を載置するステップと、メッシュ22に透液性弾性体から成る押圧部材32を圧縮しながら押し付けて該メッシュ22を金属膜パターン13に密着させるステップと、金属膜パターン13とメッシュ22とをメッキ膜41を介して接合するステップと、押圧部材32をメッシュ22から引き離すと共に、台板11をメッシュ22から引き離して該台板11から金属膜パターン13を剥離するステップと、を経て行う。

(もっと読む)

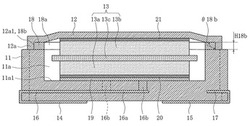

電気化学デバイス

【課題】集電膜の上面と蓄電素子の一方極側の面との間の接続抵抗(導通抵抗)の増加を回避できる電気化学デバイスを提供する。

【解決手段】電気化学デバイス10は、ケース11の第1凹部11aの底面11a1に蓄電素子13の第1電極シート13aの下面の輪郭よりも小さな開口輪郭を有し、且つ、所定の深さD11bを有する第2凹部11bが形成され、集電膜19が第2凹部11bの深さよりも小さな厚さT19を有していて該第2凹部11bの底面11b1に設けられ、第1凹部11aの底面11a1と集電膜19の上面との間に第2凹部11bの深さD11bから集電膜19の厚さT19を減じた寸法(=D11b−T19)に相当する深さを有する接着剤貯留部ARが形成され、第1導電性接着層20が該接着剤貯留部ARに充填されるようにして設けられている。

(もっと読む)

配線基板、半導体装置及び配線基板の製造方法

【課題】貫通孔内の絶縁信頼性を向上させることのできる配線基板、半導体装置及び配線基板の製造方法を提供する。

【解決手段】配線基板1は、第1主面R1と第2主面R2との間を貫通する貫通孔10Xを有する基板本体10と、貫通孔10X内に形成された貫通電極12と、上記第1主面R1を覆う絶縁膜11上に、第1電極22と誘電体層23と第2電極24とが順に積層されて形成されたキャパシタ部21を有するキャパシタ20とを備えている。また、貫通孔10Xの内壁面は、少なくとも貫通孔10Xの内壁面を覆う絶縁膜11と、第1電極22と同一の材料からなる第1金属層32と、誘電体層23と同一の材料からなる誘電体層33と、第2電極24と同一の材料からなる第2金属層34とで順に覆われている。

(もっと読む)

チップ状電子部品

【課題】 実装不良が起こることを効果的に防止した積層セラミックコンデンサ、積層セラミックインダクタ、積層バリスタなどのチップ状電子部品を提供する。

【解決手段】 チップ状電子部品2は、一対の端面とその両端面の間の4つの側面を有する略直方体の素体と、素体に内蔵されかつ一対の端面に引き出されている内部導体と、内部導体と電気的に接続するように、一対の端面にそれぞれ形成された一対の外部電極とを有し、4つの側面のうち、少なくとも一面が残りの面よりも表面粗さが大きくされている。

(もっと読む)

積層セラミックコンデンサ

【課題】積層体においてクラック等の内部破壊が生じにくく大容量且つ小型化に適した積層セラミックコンデンサを提供する。

【解決手段】複数の誘電体層120と複数の内部電極層110とを交互に積層した積層体10と該積層体10の外面に形成され前記内部電極層110に電気的に接続した外部電極20とを備えた積層セラミックコンデンサ1において、積層体10の外層側部分における隣り合う内部電極層111,112間に形成される電界強度が積層体10の中央部分における隣り合う内部電極層110間に形成される電界強度よりも小さいことを特徴とする。

(もっと読む)

積層型コンデンサ

【課題】高さ寸法の増加を抑制しつつ抗折強度を向上できる積層型コンデンサを提供する。

【解決手段】積層型コンデンサ10における5つの第1内部電極層15の1つには、該第1内部電極層15と同じくその端縁が第1外部電極12に接続されると共に、第1誘電体層DL1の厚さtd1よりも厚さtd2が薄く、且つ、容量形成に寄与しない第2誘電体層DL2を介して向き合うように追加の第1内部電極層15が1つ配置され、また、5つの第2内部電極層16の1つには、該第2内部電極層16と同じくその端縁が第2外部電極13に接続されると共に、第1誘電体層DL1の厚さtd1よりも厚さtd3が薄く、且つ、容量形成に寄与しない第3誘電体層DL3を介して向き合うように追加の第2内部電極層16が1つ配置されている。

(もっと読む)

複合多層基板およびそれを用いたモジュール

【課題】 基板の補強材にガラスクロスを用いた場合、マイグレーションの発生に伴う電気的特性の悪化を招き、また、キャビティ形成時にガラスクロスの切断加工が必要で製造コストのアップを招く。

【解決手段】 複合多層基板20は、金属製材料からなる平板状のコア部材21と、コア部材21の表面と裏面を覆う表面側樹脂層22および裏面側樹脂層23と、表面側樹脂層22および裏面側樹脂層23のいずれか一方又は双方に形成された電極(第1及び第2の電極)と、コア部材21の表裏を貫通して形成された無底穴24または有底穴と、無底穴24または有底穴に実装する電子部品25とを備え、電子部品25に対する電気的接続を第1の電極を介して行うようにし、コア部材に対する電気的接続を第2の電極を介して行うようにしたことを特徴とする。

(もっと読む)

アンテナを含む共振回路

【課題】

本発明の実施態様によって、配線パターンに機械的な変更を加えずに共振周波数を調整可能な共振回路を提供する。

【解決手段】

本発明の一実施態様に係る共振回路は、搬送波を受信するコイル状のアンテナ素子を含むアンテナ回路と、当該アンテナ回路に電気的に接続された可変リアクタンス回路とが並列共振する共振回路であって、可変リアクタンス回路は、印加されるバイアス電圧に応じて容量値が変化する第1の可変容量コンデンサを含むように構成される。第1の可変容量コンデンサは、例えば、積層セラミックコンデンサから成る。

(もっと読む)

積層型共振器及び積層型共振器の製造方法

【課題】小型で低損失の改良された積層型共振器を提供する。

【解決手段】積層型共振器10は、上面に複数の凹部が形成された基板20と、前記凹部に設けられ、入力端子電極12と電気的に接続された第1インダクタ下部電極32と、一部が前記凹部に設けられ、接地電極16と電気的に接続された第1、第2コンデンサ下部電極35、36と、前記凹部に設けられ、出力端子電極14と電気的に接続された第2インダクタ下部電極38と、前記基板上に形成された誘電体層24と、前記誘電体層上に、前記第1インダクタ下部電極に電気的に接続されるとともに、一部分が前記第1コンデンサ下部電極と対向するように形成された第1上部電極48と、前記誘電体層上に、前記第2インダクタ下部電極に電気的に接続されるとともに、一部分が前記第2コンデンサ下部電極と対向するように形成された第2上部電極50と、を備える。

(もっと読む)

121 - 130 / 964

[ Back to top ]