旭化成エレクトロニクス株式会社により出願された特許

171 - 180 / 840

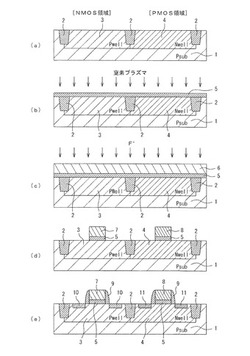

半導体装置及びその製造方法

【課題】CMOSトランジスタにおいて、ボロンの染み出しを抑制して閾値電圧を安定させると共に、ノイズを低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】CMOSトランジスタをシリコン基板1上に備える半導体装置であって、

シリコン基板1上に設けられ、窒素とフッ素とを含有するシリコン酸化膜からなるゲート酸化膜5と、ゲート酸化膜5上に設けられ、ポリシリコンからなるゲート電極7、8と、を有し、ゲート酸化膜5中のゲート電極7、8近傍の位置に窒素濃度のピークがあり、ゲート酸化膜5とシリコン基板1との界面付近の窒素濃度は0.5atom%以下であり、ゲート酸化膜5中におけるフッ素濃度は1atom%以上であり、当該フッ素によりゲート酸化膜5とシリコン基板1との界面のダングリングボンドが終端化されている。

(もっと読む)

電圧検出回路

【課題】バンドギャップ電圧を利用した回路や拡散抵抗等の温度特性や絶対値のバラツキや入力電圧依存性が大きい素子を用いずに、正の温度係数が調整可能な電圧検出回路を提供する。

【解決手段】電流コンパレータ部100の第1及び第2のp型MOSFET(MP1,MP2)及び第1のn型MOSFET(MN1)のゲートバイアスを設定するゲートバイアス設定部150の設定によって、第2のn型MOSFET(MN2)に入力電圧が印加されたときに第1のp型MOSFETに流れる電流(IPTAT1)と第1のn型MOSFETに流れる電流との差分が一定となり及び該差分が検出部200に流れる電流と等しくなる。環境温度に関らずに一定の検出精度を得ることができる。

(もっと読む)

受光素子及び受光素子の製造方法、半導体装置

【課題】寄生容量を抑制しつつ、電磁波に対する遮蔽効果を十分に発揮することができるようにした受光素子及び受光素子の製造方法、半導体装置を提供する。

【解決手段】P−領域1と、P−領域1に接合されたN−領域3と、N−領域3の一方の面3b上に形成された光透過性を有する誘電体5と、誘電体5上に形成された光透過性を有する電磁シールド7と、を備え、電磁シールド7は、ポリシリコンからなる。受光素子10に入射してくる光は、電磁シールド7及び誘電体5を通ってPN接合面3aに到達する。このため、PN接合面3aでは、受光量の低下を抑えつつ、電磁波の到達を抑えることができる。また、電磁シールド7とN−領域3との間には誘電体5が介在するため、当該間の寄生容量を低減することができる。

(もっと読む)

回転検出器

【課題】高分解能、高耐久性、高信頼性を備えた磁性体歯車と磁気センサとバイアス磁石を用いたアブソリュートエンコーダである回転検出器を提供すること。

【解決手段】回転体の回転軸5に同軸に取り付けられた2個の磁性体歯車1,2と、この磁性体歯車1,2の各々に対向するように配置された2個の磁気センサ7,8と、磁性体歯車1,2の回転に応じて磁気センサ7,8に印加される磁束密度が変化するように配置されたバイアス磁石6とを備えている。磁気センサ7,8の各々は、磁性体歯車1,2の回転に応じて1歯あたり90度位相差を有するA/B相の正弦波出力を1位相だけ出力するアブソリュートエンコーダであり、磁性体歯車1,2の歯数が1歯だけ異なるように構成されている。

(もっと読む)

スイッチトキャパシタ回路

【課題】エスティメートフェーズとレベルシフトフェーズとで、レベルシフト用コンデンサCca、Ccbを、全差動演算増幅器AMP2の出力のサンプルと全差動演算増幅器のAMP2位相補償とに兼用する方式のCLS技術を適用したスイッチトキャパシタ回路100において、入出力コモン電圧の変動を抑止するこれにより、同相入力レンジの大きさに関する要求水準を低減させて、十分な低電圧化が図られて消費電力が低減されたスイッチトキャパシタ回路を実現する。

【解決手段】エスティメートフェーズからレベルシフトフェーズへの移行に際して、複数の全差動演算増幅器AMP1、AMP2のうちの初段の全差動演算増幅器および最後段の全差動演算増幅器の各出力コモン電圧が等しくなるように保持する出力コモン電圧保持回路110を備えた。

(もっと読む)

平面コイル、平面コイルの製造方法及びアクチュエータ用複合平面コイル

【課題】電気絶縁性を損なうことなく、自在に変形可能な平面コイルを提供する。

【解決手段】銅めっきされた第1導体13を埋め込んでいるフレキシブルな第1樹脂層14と、銅めっきされた第2導体16を埋め込んでいるフレキシブルな第2樹脂層17と、これら第1樹脂層及び第2樹脂層の間に積層された内側絶縁層12と、第1樹脂層の外側に積層された第1外側絶縁層15と、第2樹脂層の外側に積層された第2外側絶縁層18とを備え、前記内側絶縁層、前記第1樹脂層及び第2外側絶縁層を、絶縁性を有する可撓性フィルムで構成した。

(もっと読む)

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

位置検出装置及びそれを備えた電子機器

【課題】構成部品を汎用品や入手が容易な部品などにより構成した場合においても、簡易な構成で、かつ小型で広範囲な距離を高精度にかつ絶対位置を即座に検出すること。

【解決手段】感磁方向が、配置された基板103に対して垂直な2個のホールセンサ102a,102bを1組とし、この2個のホールセンサの中心を結ぶ直線及び基板に平行に可動可能に支持し、基板上の2個のホールセンサからの出力値が減衰振動波状もしくは増幅振動波状となるようにN極とS極が所定の間隔で所定の組数着磁された磁石101を配置した状態において、磁石の移動方向への移動距離に対する、基板上の2個のホールセンサからの出力値を所定の相関関係を用いて位置検出を行う。

(もっと読む)

電源装置

【課題】効率的に起動を行うことが可能な電源装置を提供すること。

【解決手段】電源装置の構成要素である昇圧回路の起動動作時において、昇圧回路の起動用PWM信号のデューティを1次電圧又は2次電圧等の電源電圧に依存して変化させる。電源電圧が低電圧のときにはデューティ比を高くして起動時間の高速化を行い、電源電圧が高電圧のときにはデューティ比を低くして消費電流を低廉にする。

(もっと読む)

トランスコンダクタンスアンプ及びそれを用いたGm−Cフィルタ

【課題】線形性能が優れたGmアンプ、このGmアンプを用いて高速動作が可能で、入力電圧範囲が広く、かつ線形性能の優れたGm−Cフィルタを提供する。

【解決手段】入力信号が端子17、18から供給され、ソース端子が電源端子に接続されるMOSトランジスタ11、12、同相制御信号がゲート端子から供給されるMOSトランジスタ13、14、出力信号を出力する出力端子対の平均電圧を一定にするためMOSトランジスタ13、14のゲート端子に同相制御信号を出力する同相制御アンプ15、入力信号を入力して、MOSトランジスタ11、12に入力される入力信号の大小に応じて基板電圧を制御する基板制御信号をMOSトランジスタ11、12の基板端子に供給する基板電圧制御回路21、22によってGmアンプを構成する。

(もっと読む)

171 - 180 / 840

[ Back to top ]