富士通セミコンダクター株式会社により出願された特許

2,481 - 2,490 / 2,507

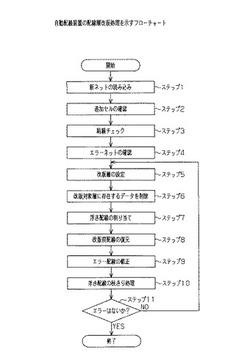

配線層レイアウトデータの改版方法

【課題】配線層レイアウトデータの改版を行なうとき、改版層数を削減して改版コストを低減し、かつ改版による回路特性の劣化を防止し得るレイアウトデータの改版方法を提供する。

【解決手段】修正された新ネットリストを読み込む工程と、レイアウトデータと新ネットリストを比較する工程と、比較結果に基づいてエラーネットを確認する工程と、エラーネットの配線要素に基づいて改版対象層と非改版対象層を設定する工程と、エラーネットの配線要素を浮き配線として設定する工程と、浮き配線を改版ネットの配線要素として割り当てる工程と、改版前ネットと浮き配線に基づいて改版ネットを生成する工程と、改版ネットの枝きり処理を行う工程とを備えた。

(もっと読む)

半導体装置の製造方法、パターン形成方法及びパターン補正装置

【課題】リソグラフィープロセスを工夫することにより、フォトマスクにおけるマスクパターンの寸法誤差を容易且つ確実に補正し、所望のレジストパターンを正確に形成する。

【解決手段】先ず、レジストパターンの厚肉化により変化する寸法と、厚肉化の工程における熱処理の温度との関係を予め求めておく。続いて、マスクパターンの寸法を計測し、その計測結果を上記の関係に適用して、レジストパターンを所望の寸法に厚肉化するための最適な熱処理温度を決定する。

(もっと読む)

半導体集積回路の設計方法および設計用プログラム

【課題】電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサの抵抗素子の最適抵抗値を自動算出できる半導体集積回路の設計方法を提供する。

【解決手段】電源配線の抵抗成分32A、32Bの合成抵抗値とインダクタ成分33A、33Bの合成インダクタンスと電源配線間の容量34の容量値C1とで決まる第1の共振周波数faと、電源配線の抵抗成分32A、32Bの合成抵抗値とインダクタ成分33A、33Bの合成インダクタンスと電源配線間の容量34の容量値C1と抵抗付きデカップリングコンデンサ35の容量値C2とで決まる第2の共振周波数fbを算出し、第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35のコンデンサ36のインピーダンスに等しい値を抵抗付きデカップリングコンデンサ35の抵抗素子37の最適抵抗値として算出する。

(もっと読む)

トリガ発生回路

【課題】 マイクロコントローラにおいて通信機能のデバッグに外部で使用されるトリガ信号を所望のタイミングで正確に発生させる。

【解決手段】 トリガ発生回路は、カウンタ、複数のカウント回数保持回路および制御回路を備えて構成される。カウンタは、カウント要因信号によるカウント動作をカウント指定回数実施する。複数のカウント回数保持回路の各々は、カウント回数情報を保持する。制御回路は、通信機能に関する複数の割り込み要因信号を順次選択してカウント要因信号として供給するとともに、複数のカウント回数保持回路により保持される複数のカウント回数情報を順次選択してカウント指定回数として供給し、複数の割り込み要因信号の全てに関してカウンタのカウント動作が完了した時点でトリガ信号を発生させる。

(もっと読む)

MONOS型フラッシュメモリ

【課題】MONOS型フラッシュメモリに関し、MONOS型フラッシュメモリの構造に簡単な改変を加えるのみで、トラップ膜の電荷蓄積領域に蓄積される電荷がマイグレーションすることを抑止し、メモリの読み出しマージン縮小の問題を解消しようとする。

【解決手段】基板1上に形成されたトンネル膜2、トラップ膜3、トップ膜4の三層構造をもつゲート絶縁膜11及びチャネルを介して対向するソース5、ドレイン6と、ゲート絶縁膜11上に形成されソース5及びドレイン6上がp型、且つ、チャネル上がn型であってチャネル長方向にpnp構造を成すゲート電極21Gと、ゲート電極21G上に形成された電極28とを備えることが基本になっている。

(もっと読む)

DC−DCコンバータ、電源電圧供給方法および電源電圧供給システム

【課題】事前に回路定数等を調整することなく、入力される制御信号のチャタリングの影響を排除することができるDC−DCコンバータ等を提供すること。

【解決手段】ソフトスタート制御回路10Gには外部から動作制御信号CNTが入力される。またソフトスタート制御回路10Gには、充放電制御回路30Gから出力される出力電圧制御信号VCSか、またはパワー部50Gから出力される出力電圧Voutが入力される。ソフトスタート制御回路10Gは、DC−DCコンバータ1Gのソフトスタート動作の開始からソフトスタート動作が完了するまでの期間中に停止指令を無視する第1の動作か、または、前記DC−DCコンバータの停止開始から出力電圧Voutがゼロ近傍まで下降して前記DC−DCコンバータの停止が完了するまでの期間中に前記動作指令を無視する第2の動作を行う。

(もっと読む)

データマイニング方法及び工程管理方法

【課題】 データマイニング方法及び工程管理方法に関し、機械的作業によって、時間依存性のある事象のマイニングを短時間で且つ高精度で行う。

【解決手段】 各工程における待ち時間を含む処理時間を時間分類手法を用いて機械的に分類し、分類した時間群を説明変数としてデータマイニングを行う。

(もっと読む)

配線の評価方法及び半導体装置の製造方法

【課題】比較的簡易な構成の試料を用いて、実際の配線構造に近似する状況で配線導電材料の不純物濃度を精度良く測定し、実際の配線構造に極めて近い不純物濃度の知見を得ることを可能とし、当該知見を実際の配線形成に反映させる。

【解決手段】シリコン基板1に配線溝1aを形成し、配線溝1aを配線導電材料3で埋めんで配線様構造4を形成し、試料11を作製する。この試料11を用いて、SIMS法により配線様構造4の配線導電材料3をSIMS分析する。

(もっと読む)

塗布液の塗布方法及び半導体装置の製造方法

【課題】半導体基板、フォトマスク、LCD基板等の基板上にレジスト、SOG、ポリイミド等の塗布液を塗布するための塗布液の塗布方法について、塗布膜をより平坦に形成すること。

【解決手段】第1の時間T1において回転速度に上下の変化を有する第1の回転速度R11〜R12で基板10を回転させつつ、基板10上に塗布液を供給する工程と、塗布液の供給後に、基板の回転速度を前記第1の回転速度R11〜R12から減速する工程とを有することを特徴とする塗布液の塗布方法。

(もっと読む)

インタフェース回路

【課題】データストローブ信号によりデータを取り込み、ノイズによる誤動作を防止することができるメモリインタフェース回路を提供すること。

【解決手段】遅延回路35はデータストローブ信号DQSを遅延させて遅延信号D1を出力する。アンド回路36は、その遅延信号とデータストローブ信号DQSとを論理積演算し、その演算結果を第1のストローブ信号DQSdとして出力する。インバータ回路37は、第1のストローブ信号DQSdを入力し、その第1のストローブ信号DQSdと相補な第2のストローブ信号Ddxを出力する。第1FF32は、第1のストローブ信号DQSdに基づいてデータDQをラッチし、第2FF33は、第2のストローブ信号Ddxに基づいてデータDQをラッチする。

(もっと読む)

2,481 - 2,490 / 2,507

[ Back to top ]