フリースケール セミコンダクター インコーポレイテッドにより出願された特許

111 - 120 / 806

SiGeチャネルを有するデュアル高K酸化物

PMOSデバイス領域112、113内にシリコンゲルマニウムチャネル層21を有する単一基板15にデュアルゲート酸化物(DGO)トランジスタデバイス50、52およびコアトランジスタデバイス51、53を集積するための方法および装置を記載する。各DGOトランジスタデバイス50、52は、金属ゲート25と、第2の相対的により高い高K金属酸化物層24から形成された上部ゲート酸化物領域60、86と、第1の相対的により低い高K誘電体層22から形成された下部ゲート酸化領域58、84とを含む。また、各コアトランジスタデバイス51、53は、金属ゲートと、第2の相対的により高い高K金属酸化物層24から形成されたコアゲート誘電層72、98とを含む。  (もっと読む)

(もっと読む)

負電圧書き込み支援回路を有するメモリ及びその方法

メモリ10の選択された列にデータを書き込む方法は、第1列を選択するステップを含む。データ書き込みは、論理ハイを第1列の第1ビット線(BL0)に印加し、並びに論理ハイより低い第1電位を第1列の第2ビット線(BLB0)に印加することによって開始される。第1電位が除去され、第2電位は第2ビット線に印加される。第2電位は第1電位より小さい。第1電位は接地(VSS)であってもよく、第2電位は負電圧(VNEG)であってもよい。論理ローを受け取るビット線に対する書き込み電圧を減少することが、ビット線への書き込み能力を改善する。初めに論理ローを(接地であり得る)第1電位とし、次に印加された電圧を更に減少することによって、第2電位の電源に対する要求が低減される。  (もっと読む)

(もっと読む)

容量−電圧インタフェース回路及び関連する動作方法

容量式感知セル402の動作に関連し得る検出される差の容量に相当する電圧を取得するために容量−電圧インタフェース回路400が用いられる。インタフェース回路400は、容量式感知セル402、容量式感知セル402に選択的に接続するように適合されている演算増幅器408、演算増幅器408用のフィードバックキャパシタ412,414、演算増幅器408用の負荷キャパシタ416,418、及び容量式感知セル402、演算増幅器408、フィードバックキャパシタ412,414、及び負荷キャパシタ416,418に関連する、スイッチングアーキテクチャ108を含む。使用中、スイッチングアーキテクチャ108は、容量−電圧インタフェース回路400を複数の様々なフェーズにおける動作のために再構成する。様々な動作フェーズによって、単一の演算増幅器408が容量−電圧変換及び電圧増幅の両方のために使用されることが可能となる。  (もっと読む)

(もっと読む)

分離した微細構造を有する微小電気機械システムデバイス及びその製造方法

微細構造を有する微小電気機械システム(MEMS)デバイス20は、ポリシリコン構造層に形成され、基板22上に担持され、可動の微細構造を有するポリシリコン構造層46を含む。微細構造28が分離トレンチ56に横方向に固定されるように、分離トレンチ56は層46を貫通して延びる。犠牲層22は基板上に形成され、構造層46は犠牲層22上に形成される。ポリシリコン構造層46を貫通してエッチングし、シリコンリッチ窒化物なような窒化物72をトレンチ56に堆積することによって、分離トレンチ56が形成される。そして、微細構造28は構造層46に形成され、分離トレンチ56の上方に電気接続部30が形成される。基板22から相隔たった分離した微細構造28を有するMEMSデバイス20を形成するために、犠牲層22をその後除去する。  (もっと読む)

(もっと読む)

ゲート・スタックを形成する方法

【課題】 電界効果トランジスタのためのゲート・スタックを形成する方法を提供すること。

【解決手段】 方法は、第1及び第2の型の電界効果トランジスタに対して指定された半導体基板の領域を覆う第1の窒化チタン(TiN)層の上に直接、金属含有層を形成することと、金属含有層の上に第2のTiN層のキャッピング層を形成することと、第1の型の電界効果トランジスタに対して指定された領域を覆う第1のTiN層の第1の部分のみを覆うように、第2のTiN層及び金属含有層をパターン形成してすることと、第1のTiN層の第1の部分をパターン形成された金属含有層の厚さの少なくとも一部で覆うことによりエッチングから保護する一方で、パターン形成によって露出された第1のTiN層の第2の部分をエッチング除去することと、第2の型の電界効果トランジスタに対して指定された半導体基板の領域を覆う第3のTiN層を形成することとを含む。

(もっと読む)

発振回路

発振回路10は、プッシュ−プッシュ型発振器12と、差動出力部14,15と、第1、第2の出力回路16,18とを備える。プッシュ−プッシュ型発振器12は第1、第2の分岐回路20,22を有する。第1、第2の分岐回路20,22の各々は共通のブリッジ回路28にそれぞれの分圧分岐回路24,26を備える。第1、第2の分圧分岐回路24,26の各々は、直列に接続された一対のマイクロストリップライン30,32;34,36をそれぞれ備える。第1、第2の分圧分岐回路24,26の各々は、それぞれのタップC,Dを有する。両方のタップC,Dは、第1の容量性部材42およびマイクロストリップラインのうちの少なくとも一方によって互いに接続されている。差動出力部は、第1、第2の出力端子14,15を備える。第1の出力端子14は第1の出力回路16を介して第1のノードAに接続されている。第2の出力端子15は第2の出力回路18を介して第2のノードBに接続されている。プッシュ−プッシュ型発振器12の第1、第2のノードA,Bの各々は、第1、第2の分岐回路20,22の両方の共通のノードA,Bである。  (もっと読む)

(もっと読む)

ボンディングパッドを有する半導体装置及びその形成方法

【課題】信頼性の高い集積回路を提供する。

【解決手段】集積回路20は、基板26を覆うパッシベーション層18及び前記基板26を覆うボンディングパッド200を備え、該ボンディングパッド200は、第1ボンディングワイヤを当該集積回路20に接続するための第1ワイヤボンディング領域202と第2ボンディングワイヤを当該集積回路に接続するための第2ワイヤボンディング領域204とを含み、前記第1ワイヤボンディング領域202の少なくとも非周辺部分が前記パッシベーションの上に位置し、前記ボンディングパッド200の下方にあるパッシベーション層が複数の開口を有し、前記基板26は配線領域を有し、該配線領域の少なくとも一部は前記パッシベーションの上に位置する前記ボンディングパッド200の一部の下に存在し、かつ前記配線領域の部分が前記複数の開口を介して前記ボンディングパッド200に結合する。

(もっと読む)

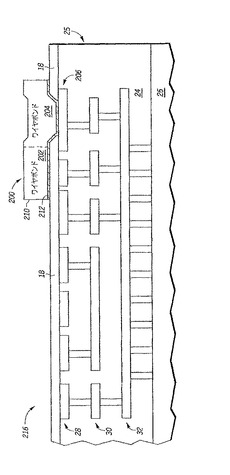

無線アプリケーション用高出力半導体素子および高出力半導体素子の製造方法

無線アプリケーション用の5Wを超える電力で動作する高出力半導体素子(400)は、高出力半導体素子の活性領域(404)を含む半導体基板(402)と、高出力半導体素子の活性領域にコンタクトを提供する、半導体基板上に形成された接触領域(408)と、半導体基板の一部を覆うように形成された誘電体層(412)と、高出力半導体素子に外部接続部を提供するリード線(500、502)と、高出力半導体素子の活性領域とリード線との間の半導体基板上に形成されたインピーダンス整合回路網(510、512)であって、インピーダンス整合回路網は、誘電体層上に形成された複数の導体線(414)であって、活性領域の接触領域に高出力接続部を提供する、接触領域に結合された複数の導体線を含み、該複数の導体線はインピーダンス整合のための所定のインダクタンスを有する、インピーダンス整合回路網とを備える。  (もっと読む)

(もっと読む)

ボンドパッド下の溝を特徴とするRF装置及び方法

共通する基板(45)上のアクティブデバイス領域46及びボンドパッド(BP)領域60を有する電子素子44、44’、44”において、電子素子(44、44’、44”)をより高い電力あるいは動作周波数、またはその両者にスケール化するように、BP(35)とその相互接続部(41)の寄生インピーダンスを減少するために、BP(35)の下にある誘電体領域を有する。通常(例えば、酸化のみ)の誘電体領域36’による機械的応力は、性能、製造歩留、パッド対装置の近接及び占有面積において不利な点を及ぼす可能がある。埋め込まれた、あるいは近くに配置された、もしくはその両者である誘電性材料78、78’、78”より低い熱膨張係数の、電気的に分離された介在物65、65’、65”を有する複合材料製の誘電体領域62、62’、62”を備えることによって、不利な点を回避できる。シリコン基板(45)において、ポリシリコンあるいは非晶質シリコンは、介在物(65、65’、65”)に適しており、酸化シリコンは誘電体材料(78、78’、78”) に適している。介在物(65、65’、65”)は、誘電体材料(78、78’、78”)によって分離され、その内部に封入される刀身のような形状を有することは望ましい。  (もっと読む)

(もっと読む)

電気機械トランスデューサデバイスおよびその製造方法

MEMSまたはNEMSデバイス(200)の可動構造(203)は、第1熱応答特性と第1機械応力応答特性とを有する機械層(204)を備えた機械構造と;第2熱応答特性と第2機械応力応答特性とを有する作動構造(202)と;第3熱応答特性と第3機械応力応答特性とを有する第1補償層(206)と;第4熱応答特性と第4機械応力応答特性とを有する第2補償層(207)とを有する。第1補償層(206)と第2補償層(207)とは、可動構造(203)の運動が温度変動に依存しないように、機械構造(204)と作動構造(202)とによる熱効果を補償するように構成される。かつ第1補償層(206)と第2補償層(207)とは、MEMSまたはNEMSデバイスが非アクティブ状態のとき可動構造が所定量だけ歪むように、機械構造(204)と作動構造(202)とによる応力効果を調整するように構成される。  (もっと読む)

(もっと読む)

111 - 120 / 806

[ Back to top ]