フリースケール セミコンダクター インコーポレイテッドにより出願された特許

121 - 130 / 806

無線通信システムにおける無線リンクの問題及び回復を検知するための技術

無線通信システムにおいて無線リンクを検知するための技術(300)は、インジケータチャネルの第1のエラーレートを推定する(304)ことを含む。この場合、インジケータチャネルは制御チャネルのシンボル数を示す指標を含む。制御チャネルの第2のエラーレートも推定する(306)。そして、性能メトリックを提供するために、第1のエラーレートと第2のエラーレートとを結合する。(308)。性能メトリック308に基づき、無線リンクの問題が存在するか否かの判定を行う(310)。  (もっと読む)

(もっと読む)

電気機械トランスデューサデバイスおよびその製造方法

半導体基板(210)上に形成されたマイクロまたはナノ電気機械トランスデューサデバイス(200)は、作動構造の作動に応答して運動可能に構成された可動構造(203)を有する。可動構造(203)は、第1熱応答特性を有する少なくとも1層の機械層を備えた機械構造(204)と、第1熱応答特性とは異なる第2熱応答特性を有する作動構造(202)の少なくとも1層と、少なくとも1層の熱補償層を備えた熱補償構造(206)とを含んでいる。熱補償構造(206)は、少なくとも1層の作動構造(202)とは異なり、可動構造(203)の運動が実質的に温度変化には依存しないように、機械層(204)と作動構造(202)とによって生み出される熱効果を補償するように構成されている。  (もっと読む)

(もっと読む)

データ処理システム及び方法

データ処理システム(10)及び動作方法はキャッシュ(26)に結合されたプロセッサ(30)を使用する。キャッシュ制御回路(38)は、キャッシュに結合され、誤り検出を行う。ユーザプログラマブルエラー処理制御レジスタ(48)は、キャッシュエラーが検出された際に行われるエラー処理のタイプを選択するための制御値を保存している。第1の値の制御値は、プロセッサにとって透明な(トランスペアレントな)キャッシュエラーの処理を可能にし、第2の値の制御値は、プロセッサにとって可視的である例外処理を可能にする。誤り訂正やキャッシュラインの無効化等を含む検出されたエラーに対する様々な代替処理が、他の値の制御値に応じて行われてもよい。  (もっと読む)

(もっと読む)

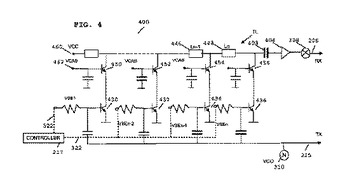

位相補償のための集積回路、通信ユニット、および方法

通信ユニット(200)は、コントローラ(217)と、一連の増幅段(330,332,334)の各々と動作可能に接続された複数の遅延要素を有する無線周波数信号経路と、を備え、コントローラ(217)は、増幅段(330,332,334)の各々をそれぞれ活性化するように構成される。活性化させることに応じて、複数の遅延要素のうちのいくつかの遅延要素が選択的に無線周波数信号経路に挿入され又は無線周波数信号経路からバイパスされて、無線周波数信号経路を介して供給される信号に適用される位相シフトを調整する。  (もっと読む)

(もっと読む)

電子機器、電子機器の制御方法、電子機器の制御プログラム及び電子機器のコントロール装置

【課題】エリアを管理する管理者が望まない電子機器の動作をより確実に排除することができる電子機器、電子機器の制御方法、電子機器の制御プログラム及び電子機器のコントロール装置を提供する。

【解決手段】コントロール装置10の制御部11は、トリガー信号を受信すると、機能制御信号の送信を実行する。制御対象エリア内にある電子機器20は、この機能制御信号を受信する。電子機器20の制御部21は、この機能制御信号に含まれる制御メッセージの設定条件に、現在の設定条件が一致しているか否かを判定し、一致していなかった場合には、現在の設定条件を利用者設定値として記録し、制御メッセージの設定条件に変更する。電子機器20の制御部21は、手動により設定条件が変更されると、機能制御信号を受信している場合には、制御メッセージの設定条件を維持する。制御部21は、機能制御信号の受信が終了すると、利用者設定値に設定条件を戻す。

(もっと読む)

相互直交方向で分離的検知を有するトランスデューサ

微小電子機械システム(MEMS)トランスデューサ90が、相互直交方向92,94,96の加速を検知するようになっている。MEMSトランスデューサ90は、アンカーシステム116によって基板98の上方につるして保持された試験質量100を含む。アンカーシステム116は、方向96の加速に応答して試験質量100が回転軸132に関して回転することを可能とすべく、回転軸線132に関して試験質量100を基板98に枢動的に接続する。試験質量100は、試験質量100を通って延びる開口112を有する。開口112内には別の試験質量148が存在し、別のアンカーシステム152が基板98の表面104の上方に試験質量148を保持する。アンカーシステム152が、少なくとも一つの方向92または方向94の加速に応答して、試験質量148が基板98の表面104と実質的に平行に移動することを可能にする。  (もっと読む)

(もっと読む)

メモリ回路におけるリーケージ電流を制限する回路および方法

【課題】スタンバイモードにおける集積回路のリーケージ電流を制限する小型かつ容易に集積できる電流制限回路を実現する。

【解決手段】電流制限回路70はスタンバイモードで動作する間に携帯用無線装置10のメモリ回路24のリーケージ電流を制御する。第1の半導体ウエル64が第2の半導体ウエル66に配置されたメモリ回路24を隔離する。スタンバイモードにおいて、電流制限回路は非導通モードに切り替えられ第2の半導体ウエル64と第1の半導体ウエル66で形成されるダイオードおよび基板62と第2の半導体ウエル64で形成されるダイオードのリーケージ電流を制限する。

(もっと読む)

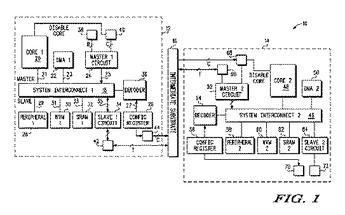

集積回路を相互接続するための技術

処理コア(20,48)及びオンボードメモリ(30,32,60,62)をそれぞれ有する2つの集積回路ダイ(12,14)は、相互接続されて一体にパッケージ化されて、多チップモジュール(10)を形成する。第1のダイ(12)はプライマリであると考えられ、第2のダイ(14)はセカンダリであると考えられ、インターポーザー(16)を介して接続されている。第1及び第2のダイは同じ設計であってよいため、周辺装置(28,56)及びメモリなど同じリソースを有してよく、好適には共通のシステム相互接続プロトコルを有する。第2のダイのコアは使用不能とされるか、少なくとも低電力モードとされる。第1のダイは、第2のダイに対し相互接続を行うための最小の回路(34,26)を備える。第2のダイはいくつかの必要なインタフェース回路(52)と、1つのアドレス変換器(50)とを有する。その結果、第1のダイのコアは、第2の集積回路のメモリ及び他のリソースを用いるトランザクションを、そのメモリ及びリソースが第1のダイ上に存在する場合のように、実行することができる。  (もっと読む)

(もっと読む)

スプリットゲート・メモリセルの形成方法

方法は、半導体基板(12)上にゲート材料の第一層(18)を形成すること、第一層上にハードマスク層(20)を形成すること、開口(22)を形成すること、ハードマスク層上と開口内とに電荷蓄積層(24)を形成すること、電荷蓄積層上にゲート材料の第二層(26)を形成すること、ハードマスク層を被覆している、第二層の一部と電荷蓄積層の一部とを除去することであって、第二層の第二部分が開口内に残存している、除去すること、ハードマスク層上と第二部分上とに、第一ビットセル及び第二ビットセルの両方を画定するパターン化されたマスク層(28、30、32)を形成すること、パターン化されたマスク層を用いて第一ビットセル及び第二ビットセルを形成することを含み、第一ビットセル及び第二ビットセルはそれぞれ、第一層から形成された選択ゲート(38、40)と、第二層から形成された制御ゲート(34、36)とを含む。  (もっと読む)

(もっと読む)

データ処理システムにおける割込承認

データ処理システム(10)は、対応する割込識別子(31)と対応する割込ベクトル(32)とにしたがってプロセッサ(20)に割込要求(30)を提供する割込コントローラ(14)を備える。プロセッサ(20)が割込を承認すると、プロセッサ(20)は、割込承認(33)にしたがって、割込識別子(34)経由で割込コントローラ(14)に、割込識別子(31)と同じ値を返す。割込取得/非取得識別子(35)もまた提供される。割込コントローラ(14)とプロセッサ(20)間の割込プロセスを調整するために使用される通信インターフェース(60,40,70)は、非同期である。  (もっと読む)

(もっと読む)

121 - 130 / 806

[ Back to top ]