フリースケール セミコンダクター インコーポレイテッドにより出願された特許

21 - 30 / 806

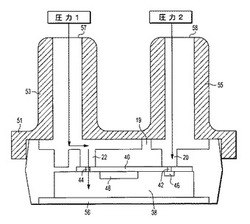

デュアルポート圧力センサ

【課題】デュアルポート圧力センサを提供する。

【解決手段】デュアルポート圧力センサは、フラグと、リードと、フィンガとを有するリードフレームを備える。第1、第2の開口部はフラグを通じて延びている。フラグと、リードと、フィンガとの一部分の周りには封止材がある。センサは、封止材の底側においてフラグの底面を露出する底部キャビティと、封止材の上側における第1、第2の上部キャビティとを備える。第1の上部キャビティ内の第1の開口部は、フラグの第1の開口部に整合されており、フラグにおける第1の開口部より大きい。第2の上部キャビティ内の第2の開口部は、フラグの第2の開口部に整合されており、フラグにおける第2の開口部より大きい。デュアルポート圧力センサの上側におけるデュアルポートは、第1のキャビティおよび第2のキャビティに取り付けられている。

(もっと読む)

ルーティングのための方法及び装置

【課題】データプロセッサコアのサイズ及び遅延を小さくすること。

【解決手段】データプロセッサが開示され、該データプロセッサが、該データプロセッサ外部のデータ経路を通して要求をルーティングすることによって該データプロセッサのローカルメモリをアクセスする。予約/修飾コントローラが、ローカルメモリをアクセスするための受信される要求に関連される特定動作を実行される。特定動作に加えて、データプロセッサコアのローカルメモリをアクセスするために予約/修飾コントローラに関連するメモリコントローラが相当するアクセス要求をデータプロセッサコアにルーティングする。

(もっと読む)

改良された帯域幅を備える電圧制御発振器を有する位相同期ループ回路

【課題】改良された電圧制御発振器を提供する。

【解決手段】電圧制御発振器(16)は複数の直列に接続された合成利得段(42、44、46)を含む。合成利得段はトランスコンダクタンス段(48)及びトランスインピーダンス段(50)を含む。トランスコンダクタンス段は第1電源電圧端子から第2電源電圧端子への第1電流経路(52、56、64)及び第2電流経路(54、58、66)を有する。第1可変抵抗(62)は第1電流経路と第2電流経路との間に接続される。トランスインピーダンス段は、第1電流経路の出力に接続された入力端子と、出力端子とを有する第1インバータ(68、72)及び第2電流経路の出力に接続された入力端子と、出力端子とを有する第2インバータ(70、74)を有する。第2可変抵抗(76)は第1インバータの入力端子と出力端子との間に、第3可変抵抗(78)は第2インバータの入力端子と出力端子との間に接続される。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

負荷制御および保護システム、並びにその動作および使用方法

【課題】開接地故障等による過電流から負荷を保護するための負荷制御及び保護システム等を提供する。

【解決手段】システム(51)は、DCバス(23)に接続されるDC端子(27)と、負荷(24)に接続される負荷端子(29)と、外部接地バス(25)に接続される接地端子(28)と、オン/オフ命令を受信する入力端子(26)とを有する。システムの内部接地バス(60)は、通常、接地端子を介して外部接地バスに接続されるが、接地故障により外部接地バスから接地端子が切断される場合、自動的に負荷端子に接続され、システムおよびDCバスと接地端子との間に接続されるあらゆる周辺回路の継続的動作を助ける合成接地が提供される。システムを通って外部接地バスへ流れるいかなる周辺回路電流も、負荷および外部接地端子に到達する前に接地端子と負荷端子との間の直列インピーダンスを自動調整することによって、負荷の不適切な動作を引き起こさないよう妨げられる。

(もっと読む)

封止構造を有するセンサデバイス

【課題】 センサデバイスに関する装置及び関連する作成方法が提供される。

【解決手段】 センサデバイスは、第1部分に形成された検出装置を有する第1部分及び第2構造を含むセンサ構造を含む。封止構造は、前記センサ構造と前記第2構造との間に挿入され、ここで、封止構造は、センサ構造の第1部分を囲む。封止構造は、第1部分の第1側に固定基準圧力を設け、第1部分の対向側は周囲圧力にさらされる。

(もっと読む)

ナノ結晶を有する半導体デバイスを形成する方法

【課題】

ナノ結晶を有する半導体デバイスを形成する方法を提供する。

【解決手段】

ナノ結晶を有する半導体デバイス10を形成する方法は、基板12を設けるステップと、基板の表面の上方に第1絶縁層14を形成するステップと、第1絶縁層上に第1の複数のナノ結晶26(21、22)を形成するステップと、第1の複数のナノ結晶上に第2絶縁層28を形成するステップと、第2絶縁層に第1材料を注入するステップと、第1材料をアニールして第2絶縁層内に第2の複数のナノ結晶34(36、37)を形成するステップとを含む。この方法は、より高いナノ結晶密度を有する不揮発性メモリの電荷格納層を提供するために使用され得る。

(もっと読む)

キャパシタの形成とともに不揮発性メモリのゲートスタックをパターニングするための方法

【課題】キャパシタのエッチングはNVMセルのエッチングの終点検出に有用になるようにキャパシタおよびNVMセルを集積するように形成する。

【解決手段】NVM領域およびキャパシタ領域上に2つの導電体層を用いるように達成される。第1導電体層は後のパターニングステップの準備にパターニングされ、これが、NVM領域およびキャパシタ領域の両方に第1導電体層および第2導電体層の両方をパターニングするステップを含む。後のエッチングが、同一マスクを用いて両方の導電体層をエッチングされることによって制御ゲート上に浮遊ゲートの重要な配列を提供する。この後のエッチングの間、キャパシタ領域に第1導電体材料をエッチングされることが、NVM領域における第1導電体層のエッチングの終点検出を補助する。

(もっと読む)

選択可能閾値リセット回路

【課題】低電圧試験のためのリセット回路及び方法を提供する。

【解決手段】低電圧試験回路125と、システム100および200と、集積回路パッケージ104および204における回路127の低電圧試験を実行する方法が、電源電圧の一部分である電圧を生成する電圧分割ラダー320、一部分を基準電圧と比較する比較器310、電圧分割ラダーのトポロジーを制御し、それによって一部分の値を変更するスイッチ350を含む、選択可能閾値リセット回路125を含み、スイッチは製品試験装置102および202からの信号によって制御され、信号は、選択可能閾値リセット回路のリセット閾値を標準リセット閾値未満に低減されるようにして、標準リセット閾値未満の電源電圧で回路を試験することを可能にする。

(もっと読む)

同期データ処理システムおよび方法

【課題】伝搬遅延およびPVT条件の変化時に高信頼性のデータ転送を可能とするデータ処理システムを提供する。

【解決手段】同期データ処理システムはデータを格納するメモリモジュールと、メモリモジュールに接続されたメモリコントローラとを備える。メモリコントローラのクロックインバータは入力クロック信号を受信し反転クロック信号をメモリモジュールに提供する。反転クロック信号によってメモリモジュール到達前の第1の伝搬遅延がメモリクロック信号として与えられる。メモリモジュールに接続された書込データバッファは入力クロック信号に応答してメモリモジュールにデータを提供する。メモリモジュールに接続された非同期先入れ先出しバッファはメモリクロック信号をバッファにフィードバックすることによって生成されるフィードバック信号に応答してメモリモジュールからデータを読み取る。

(もっと読む)

21 - 30 / 806

[ Back to top ]