Fターム[2C162AH74]の内容

電磁気プリンタ及び光プリンタ (19,948) | 共通の構成(電極、駆動素子関係) (948) | 駆動素子 (416) | 種類 (189) | トランジスタ (172)

Fターム[2C162AH74]の下位に属するFターム

FET(電界効果トランジスタ) (44)

TFT(薄膜トランジスタ) (96)

Fターム[2C162AH74]に分類される特許

1 - 20 / 32

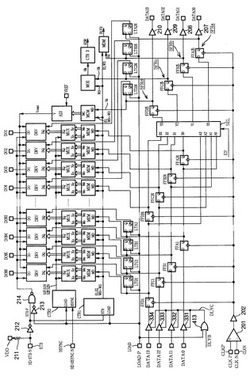

ドライバICチップ、駆動装置、プリントヘッド、画像形成装置、及び表示装置

【課題】ドライバICチップにおける、駆動データ信号の転送に要する時間を短くする。

【解決手段】アレイを構成する被駆動素子(101〜104、105〜108)を、駆動データ信号(DOT1〜DOT192)に基づいて駆動する駆動部(DRV)と、駆動データ信号を転送するためのシフトレジスタ(SFRa〜SFRd)の前段に設けられ、遅延時間を選択可能な遅延回路(331〜334)を備える。シフトレジスタ(SFRa〜SFRd)はまた,遅延時間を選択するためのデータ(Hd)を転送し、メモリ(MDM)に記憶させる。

(もっと読む)

自己走査型発光素子アレイ

【課題】転送速度を改善しながら正常な転送を実現できる自己走査型発光素子アレイを提供する。

【解決手段】シフト部/発光部の島とゲート負荷抵抗の島とを分離せずに一体化する。ゲート負荷抵抗用の電極が無くなるので、ゲート負荷抵抗の電極23とp型ゲート層13との間に存在した接触抵抗が無くなる。その結果、ゲート抵抗が小さくなり、転送速度が増大する。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】クロック駆動回路の出力端子数の削減により、回路規模を削減する。

【解決手段】発光サイリスタ210のカソードがLレベルにされると、アノード・カソード間には電圧が印加される。一方、走査回路部100における各走査サイリスタ111のゲートと、発光サイリスタ210の各ゲートとがそれぞれ接続されているため、走査サイリスタ111のゲート・カソード間にも電圧が印加される。この時、走査回路部100により発光指令されている発光サイリスタ210のゲートのみを選択的にHレベルとすることで、発光指令されている発光サイリスタ210がターンオンする。特に、クロック駆動回路69の3つの出力クロックパルスCK1R,CK2R,CKCを波形整形回路80で波形整形した2相のクロックCK1,CK2により、走査回路部100を駆動しているので、クロック駆動回路69の出力端子数を削減できる。

(もっと読む)

露光ヘッド、画像形成装置

【課題】リーク電流により発光する発光素子の光量を、光検出部(センサー)の検出値(オフセット値)に適切に反映させる。

【解決手段】第1の発光素子と、第2の発光素子と、第1の発光素子を駆動する第1の駆動素子と、第2の発光素子を駆動する第2の駆動素子と、第1の駆動素子に電気的に接続される第1の配線と、第2の駆動素子に電気的に接続される第2の配線と、第1の位置で第1の配線に接続されて第1の配線に電源を供給する第1の電源供給部と、第1の位置の第1の方向で第1の位置と第1の間隔を空ける第2の位置で第2の配線に接続されて第2の配線に電源を供給する第2の電源供給部と、光を検出する第1の光検出部と、第1の光検出部の第1の方向で第1の光検出部と第1の間隔の半分以下の第2の間隔を空けて基板に配されて光を検出する第2の光検出部と、を備える。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】同時点灯する複数の発光サイリスタのゲート間に流れる回り込み電流を略ゼロにして、発光出力の変動を防止する。

【解決手段】多数の発光サイリスタが配列され、これらが複数の組(例えば、偶数と奇数の組)に分けられ、各組の発光サイリスタ列が、複数のドライバ181により、各組毎に時分割に駆動されるプリントヘッドにおいて、同一組に属する発光サイリスタ列における各発光サイリスタのゲートを、複数の発光サイリスタのゲート間を電気的に分離するための分離回路としての個別のバッファ(例えば、163)を介して、共通配線GLにそれぞれ接続して共通に駆動する構成になっている。そのため、同時点灯する発光サイリスタのゲート間に流れる回り込み電流を略ゼロにすることができる。これにより、回り込み電流が流れることで生じる発光出力の変動を防止できる。

(もっと読む)

駆動回路、駆動装置及び画像形成装置

【課題】サイリスタを確実にオフ状態に維持できるのに十分な電位を印加することができ、かつ、そのような電位の印加が長時間続かないようにすることで、サイリスタの劣化を防ぐ。

【解決手段】複数のゲート駆動部(401、402)の各々は、対応する組に属する複数のサイリスタのゲートを駆動する期間(S1N=Low)には第1の電位(2V)を出力し、対応する組に属する複数のサイリスタのゲートを駆動しない期間(S1N=High)のうち、アノード駆動の立ち上がり部分には、第1の電位よりも高い第2の電位(5V)を出力し、対応する組に属する複数のサイリスタのゲートを駆動しない期間(S1N=High)のうち、アノード駆動の立ち上がり部分以外の期間には、第2の電位よりも低い第3の電位(3V)を出力する。

(もっと読む)

発光装置とその駆動方法と画像形成装置

【課題】発光装置において、画像形成性能を低下させずに高解像度化を容易とする。

【解決手段】複数の単位回路Uとデータ線2と制御回路50とを備える発光装置100を提供する。単位回路Uは、発光素子Pを含み、その発光輝度を指定する指定データを入力して保持し、この指定データに基づいて発光素子Pを駆動する。データ線2は、複数の単位回路Uのうち、感光面302の進行方向に沿って第1ピッチで並ぶ一定数の単位回路Uへの指定データの転送に共用される。制御回路50は、感光面302の進行方向において隣接するドットを構成するスポット像に係る指定データをデータ線2経由で一定数の単位回路Uに転送させる。一定数の単位回路Uのうちの隣り合う単位回路U間では、発光期間が一定時間ずつずれている。そして、一定時間および第1ピッチは、スポット像の各々が他のスポット像に重ならない部分を含むように定められている。

(もっと読む)

発光装置とその製造方法と画像形成装置

【課題】多重露光の発光装置において、高解像度化を容易とするとともに、常時非発光の発光素子による階調異常を抑制する。

【解決手段】複数の単位回路Uとデータ線2と制御回路50と記憶部80とを備える発光装置100を提供する。単位回路Uは、発光素子Pを含み、その発光輝度を指定する指定データを入力し、このデータに基づいて発光素子Pを駆動する。制御回路50は、一定数のスポット像に係る指定データをデータ線2へ供給し、感光面302の進行方向に沿って第1ピッチで並ぶ一定数の単位回路Uの各々に転送させる。一定数の単位回路Uのうちの隣り合う単位回路U間では、発光期間が一定時間ずつずれている。一定時間および第1ピッチは、一定数のスポット像が互いに重なるように定められており、常時非発光の単位回路Uは、発光素子Pを非発光とする指定データを入力する。

(もっと読む)

露光装置およびそれを備える画像形成装置

【課題】発光素子202aと駆動回路素子201aとを別基板に実装すると、第1電流路303と第2電流路304とが離れて配置されることになり、両電流路から生じる放射ノイズが相殺され難くなる。

【解決手段】露光装置は、発光素子202aが実装される第1基板210とそれらを発光させる駆動IC201aを実装する第2基板200とを有する。第2電流路304を第2基板200に実装される駆動IC201aから第1基板210に伸ばす。そして、第2電流路304は、第1電流路に隣接するように配される。

(もっと読む)

発光装置、画像形成装置、及び発光装置の駆動方法

【課題】 各有機EL素子のバラツキを抑制する。また、その寿命の長期化を図る。

【解決手段】電流値及びパルス幅によって規定される駆動信号によって駆動される複数の有機EL素子(8)と、これら各々について流れる各電流値を測定する電流測定手段(14)と、その測定結果に基づき判明する、第1原因に起因した前記各電流値のバラツキに基づいて、前記各電流値を一定とするような電流補正値を設定する電流値設定手段と、前記有機EL素子の各々が発する光の各パワー値を測定するパワーセンサ(23)と、その測定結果に基づき判明する、第2原因に起因した前記各パワー値のバラツキに基づいて、当該各パワー値を一定とするようなパルス幅補正値を設定するパルス幅設定手段と、を備える。本発明は、電流補正値・パルス幅補正値が、概念上区別された第1原因・第2原因に応じて定められることに特徴がある。

(もっと読む)

発光装置とその駆動方法と画像形成装置

【課題】発光素子の劣化を抑制しつつ、回路規模の大幅な増大を招くことなく、発光素子

間での発光パワーのバラツキの補正のみならず、印刷条件に応じたラインヘッド全体の発

光パワーの調整をも行う。

【解決手段】発光装置1を提供する。発光装置1は、駆動されると、指定された階調値に

応じた光量で発光する複数の発光素子EL1〜ELnと、複数のパワーレンジPR1〜P

R3にそれぞれ対応した複数の補正テーブルTBL1〜TBL3を備え、複数の補正テー

ブルTBL1〜RBL3から、指定された所要発光パワーが属するパワーレンジPRに対

応する補正テーブルTBLを選択し、複数の発光素子EL1〜ELnの各々に対して、選

択された補正テーブルTBLに格納された対応する補正データDで示される階調値を指定

する。

(もっと読む)

発光装置および電子機器

【課題】素子群の両側に配置された駆動回路の特性がばらつくことを抑制する。

【解決手段】X方向に沿って配列する複数の発光素子14からなる素子群Gと、素子群Gから見てX方向の負側に配置されて素子群Gに属する2以上の第1発光素子14aの各々を駆動する複数の第1駆動回路20aと、素子群Gから見てX方向の正側に配置されて素子群Gに属する2以上の第2発光素子14bの各々を駆動する複数の第2駆動回路20bと、を備え、各第1駆動回路20aに含まれるトランジスタの半導体層のX方向における位置は、各第2駆動回路20bに含まれるトランジスタの半導体層のX方向における位置と同じである。

(もっと読む)

発光装置、露光装置

【課題】第1の主走査方向解像度で動作が可能であるとともに、第1の主走査方向解像度の半分の第2の主走査方向解像度で動作する際にジグザグ状の文様の発生を抑制する。

【解決手段】主走査方向の出力解像度が1200dpiのフル解像度モードにおいて、発光チップC1には、奇数番目、偶数番目の点灯信号φ1、φ2が供給される。これに伴い、発光チップC1の全発光サイリスタL1〜L256は点灯可能な状態となる。一方、主走査方向の出力解像度がフル解像度モードの半分となるハーフ解像度モードにおいて、発光チップC1には、奇数番目の点灯信号φI1のみが供給される。これに伴い、発光チップC1に設けられた奇数番目の発光サイリスタL1、L3、…、L255は点灯可能な状態となるが、偶数番目の発光サイリスタL2、L4、…、L256は実質的に点灯不可能な状態となる。

(もっと読む)

発光素子アレイ、駆動制御装置、記録ヘッドおよび画像形成装置

【課題】駆動回路と発光素子とが長い接続ケーブルで接続されている場合でも、発光素子を駆動する駆動電流の立ち上がり時間を短縮し、発光素子を高速にスイッチングすることを可能にする。

【解決手段】印刷制御部1は駆動出力回路71を有し、光プリントヘッド19には複数の発光サイリスタd1〜d8が配設されている。印刷制御部1と光プリントヘッド19は接続ケーブル60で接続されており、駆動出力回路71からの駆動電流が接続ケーブル60を介して発光サイリスタd1〜d8に流れるが、接続ケーブル60と発光サイリスタd1〜d8の間に抵抗81を配する。これによりリップル波形を生じず、立ち上がり時間を短くする。

(もっと読む)

駆動回路、LEDヘッドおよび画像形成装置

【課題】LED素子が駆動される際の駆動電流のオーバシュートの発生を防止することにより、LED素子の劣化を防止する。

【解決手段】ドライバIC41にはLEDアレイ42を駆動するPMOSトランジスタ52、53とPMOSトランジスタ52に制御電圧を出力する制御電圧発生回路34が設けられる。制御電圧発生回路34には演算増幅器61が設けられ、その非反転入力端子にはアナログスイッチ回路66を介して基準電圧VREFが入力される。アナログスイッチ回路66にはLEDヘッドのストローブ信号STB−Nが入力され、LED駆動オフ状態では演算増幅器61の出力電位は電源VDDと略同電位とされる。

(もっと読む)

電気光学装置および電子機器。

【課題】入力データに対してD/A変換器から出力される電流値の精度が低下することを抑制しつつ回路規模の増大を抑制する。

【解決手段】電気光学装置10は複数の単位回路Uを備える。複数の単位回路Uの各々は、駆動電流に応じた輝度で発光する電気光学素子30と、駆動能力が異なる複数の電流源トランジスタTgを含み、複数の電流源トランジスタTgの各々が生成する単位電流Iを複数ビットの入力データに応じて合成することで入力データに応じた駆動電流Idsを生成する電流生成部44と、を具備し、複数の電流源トランジスタTgのうち駆動能力が最大の電流源トランジスタTgは、電気光学素子30に最も近接して配置される。

(もっと読む)

発光装置および電子機器

【課題】発光素子を利用した発光装置の露光品質を向上させる。

【解決手段】X方向に配列する複数の発光素子Eを各々が含む素子群G1およびの素子群G2がX方向とは異なるY方向に並列に配置され、素子群G1および素子群G2のうち何れかを発光させる駆動部40を備え、X方向に沿って配置されて各発光素子Eからの出射光を集光する複数のレンズ14を各々が含む第1のレンズ群L1および第2のレンズ群L2がY方向に並列に配置され、基準線Lcから見てY方向における一方側に素子群G1が配置され、基準線Lcから見てY方向における他方側に素子群G2が配置され、基準線Lcと素子群G1の発光素子Eとの間のY方向における距離D1は、基準線Lcと素子群G2の発光素子Eとの間のY方向における距離D2と等しい。

(もっと読む)

光ヘッド、その駆動方法、発光装置および電子機器

【課題】各発光ラインにおける不良素子について対策を講じる。

【解決手段】駆動電流Idsを供給すべき発光素子104を指定可能な素子指定手段によって発光素子104が指定されない場合は、選択部108は選択信号SELに応じて発光素子104を選択し、その選択された発光素子104に駆動電流Idsが供給される。素子指定手段によって発光素子104が指定された場合は、選択部108は素子指定手段によって指定された発光素子104を選択信号SELとは無関係に選択する。

(もっと読む)

発光装置及び電子機器

【課題】発光素子に対する温度の影響を極力排除し、かつ、構成の簡易な発光装置を提供する。また、無駄な電力消費量の低減を図る。

【解決手段】発光装置は、基板上に形成される複数の有機EL素子(8S)と、これらの各々を駆動し、かつ、電流が流されることによって有機EL素子の発熱量に応じた熱を発する発熱素子を少なくとも含む駆動回路(11S)と、少なくとも、前記発熱素子に電流が流れるかどうかについて、前記駆動回路を制御する制御手段(CU)と、を備え、前記制御手段は、通常モードの場合、前記発光素子が非発光の際に前記発熱素子に電流を流し、かつ、省エネ運転モードの場合、前記発光素子が非発光の際にも前記発熱素子に電流を流さないように、前記駆動回路を制御する。

(もっと読む)

発光装置および電子機器

【課題】消費電力を低減すると共に、信頼性を向上させた発光装置を提供する。

【解決手段】発光装置10は、n個の発光素子P1〜Pnと、駆動回路Ua1〜Uanと、電圧V1〜Vnのうち最大電圧Vmaxを検出する最大電圧検出回路30と、最大電圧Vmaxの時間的な変化の最大をピーク電圧Vpeakとして検出して保持する最大電圧保持回路40と、ピーク電圧Vpeakに基づいて制御電圧Vctlを生成する電源制御回路50と、制御電圧Vctlに基づいて電源電圧Vddを生成する電源回路60とを備える。この発光装置10は、空間的に配置されたn個の発光素子P1〜Pnの最大電圧Vmaxを検出し、さらに、時間的な最大電圧であるピーク電圧Vpeakを検出する。

(もっと読む)

1 - 20 / 32

[ Back to top ]