Fターム[2G132AA01]の内容

Fターム[2G132AA01]の下位に属するFターム

PLA、PLD、ゲートアレイ (59)

CPU、順序回路 (151)

カウンター、レジスター、フリップフロップ (33)

トライステート、双方向素子

多値(3値以上)論理回路 (1)

メモリ回路 (731)

Fターム[2G132AA01]に分類される特許

201 - 220 / 1,025

フーリエ変換回路、逆フーリエ変換回路及びフーリエ変換回路検証方法

【課題】フーリエ変換回路の検証工数を削減すること。

【解決手段】回転因子記憶部2が、フーリエ変換処理に用いられる回転因子を記憶し、符号反転部3が、回転因子記憶部2に記憶された回転因子のQ成分の符号を反転させる。そして、フーリエ変換処理部4が、所定の入力部を介して入力されたデータに対して、回転因子記憶部2に記憶された回転因子を用いてフーリエ変換処理を実行する。さらに、フーリエ変換処理部4が、フーリエ変換処理の結果に対して、回転因子記憶部2に記憶された回転因子のI成分と符号反転部3によって符号が反転された回転因子のQ成分とを用いて逆フーリエ変換処理を実行する。そして、判定部5が、フーリエ変換処理部4による逆フーリエ変換処理の結果と図示しない入力部を介して入力されたデータとが一致するか否かを判定する。

(もっと読む)

ユニバーサルチャネルインタフェース試験回路及びシステム

【課題】電子回路等の被試験装置に試験信号を印加して被試験装置を監視することにより、被試験装置の1つ又は複数の電気特性を試験する試験回路及びシステムを提供する。

【解決手段】試験回路は、単一の自動試験システム内の複数のユニバーサルインタフェースチャネル回路210を用いて、電子回路又は装置を試験を行う。単一のデータ収集回路120を、1つ又は複数のユニバーサルインタフェースチャネル回路210に結合する。各ユニバーサルインタフェースチャネル回路210は、様々な試験信号のうちの1つをDUTに供給することを、データ収集回路120から個別に命令する。

(もっと読む)

誤り率測定装置及び方法

【課題】被試験デバイスのビット誤り率や波形測定・表示を行う際に必要なパラメータ値設定を簡便に行える誤り率測定装置及び方法を提供する。

【解決手段】操作入力部16からの所定操作により誤り率測定部11又は波形測定部13の何れか一方の測定部のトラッキング設定がONされると、制御部18が他方の測定部のパラメータ値の問い合わせをしてトラッキングON設定された側の測定部に出力する。そして、トラッキングON設定された側の測定部は、問い合わせをしたパラメータ値をトラッキング設定がON状態の測定部に反映してパラメータ値の同期を図っている。

(もっと読む)

集積回路及び故障診断回路

【課題】故障診断動作から通常動作への動作遷移を容易に行うことを目的とする。

【解決手段】開示の装置は、第1記憶回路及び複数の第2記憶回路を備える。第1記憶回路は、第1制御信号に応じて、入力選択回路から出力された入力データ又はスキャンデータを保持する。複数の第2記憶回路は、それぞれ、第1制御信号又は第1制御信号に依らずに強制的にデータを保持させるための第2制御信号に応じて、第1記憶回路から出力されたデータを保持する。制御信号出力回路は、複数の第2記憶回路のそれぞれに対して、第1制御信号及び第2制御信号のうちの一方を出力する。そして、出力選択回路は、複数の第2記憶回路のうちの1つの第2記憶回路を選択し、選択した第2記憶回路から出力されたデータを出力する。

(もっと読む)

半導体試験装置

【課題】システムバスのコマンドの通信量を軽減することでオーバーヘッド時間を短縮し、試験時間を短縮することが可能な半導体試験装置を実現する。

【解決手段】記憶部を有するハードウェアを複数備え、コマンドにより記憶部から設定対象部へ設定データを転送する半導体試験装置において、コマンドを送信するシステム制御部と、システム制御部から送信された設定データと転送時に必要なアドレス情報を記憶部に書き込み、コマンドを受信して記憶部に記憶されているアドレス情報に基づいて設定データを転送する設定制御部とを備える。

(もっと読む)

マルチチップ半導体装置のテストパターン作成方法、作成装置、及び、作成プログラム

【課題】複数の半導体チップを内蔵するマルチチップ半導体装置において、外部端子に接続されるパッドより内部で他の半導体チッブに接続され外部端子には接続されないパッドが多い場合にも効率的にテストパターン作成を行うことができるテストパターン作成方法、作成装置、及び、作成プログラムを提供する。

【解決手段】他の半導体チップのバウンダリスキャンを用いて機能テストの対象とする半導体チップのチップ間接続パッドから入出力されるテストパターンを生成し、外部端子に接続されるパッドから入出力されるテストパターンと合成する。

(もっと読む)

半導体試験装置

【課題】アクティブロードの低消費電力化が図れ、より少ない消費電力でDUTの同時測定個数を大幅に増加させることができる半導体試験装置を実現すること。

【解決手段】測定対象デバイスの出力信号を検出するコンパレータと並列に、バッファアンプを介して入力される設定電圧に応じて負荷電流を制御するアクティブロードが接続された半導体試験装置において、

前記バッファアンプはD級アンプで構成されていることを特徴とするもの。

(もっと読む)

半導体装置

【課題】開発の早期において、様々な条件におけるクロストーク耐性を確認することができる半導体装置を提供する。

【解決手段】信号発生回路3と、遅延回路40、41、42、43、…、4mと、遅延回路50、51、52、53、…、5mと、出力バッファ70、71、72、73、…、7mそれぞれに対応して設けられ、遅延回路40、41、42、43、…、4mから出力された信号または遅延回路50、51、52、53、…、5mから出力された信号のいずれかを選択して対応する出力バッファ70、71、72、73、…、7mに出力する選択回路60、61、62、63、…、6mと、を備える。

(もっと読む)

テスタ用テストパタン生成方法、テスタ用テストパタン生成プログラム、及びテスタ用テストパタン生成装置

【課題】テスタによる機能テストのテスト精度を低下させずに、テスタ用テストパタンにおけるタイミングセット数を削減する。

【解決手段】本発明によるテスタ用テストパタンの生成方法は、論理設計時に生成された第1テストパタン201を、半導体集積回路で用いられる最高周波数のクロック信号20に応じたサイクルでサイクライズするステップと、第1テストパタン201におけるタイミングエッジを、タイミングエッジ直前のピリオド境界に変更して第2テストパタン301を生成するステップとを具備する。

(もっと読む)

論理回路用テストポイント挿入方法、論理回路試験装置

【課題】テスト対象の論理回路に対してテストポイントを効果的に挿入すること

【解決手段】論理回路試験装置10は、論理回路の設計データから得た配線条件により信号線の故障推定度を推定する故障推定部110を備える。また、論理回路試験装置10は故障推定度に基づいてテストポイントを挿入する挿入部130を備える。論理回路試験装置10は、挿入部130によってテストポイントの挿入された論理回路に対してテストの実行を行う。

(もっと読む)

電気回路および試験装置

【課題】複数の動作回路を制御する制御回路全体の規模を低減する。

【解決手段】それぞれが制御信号を出力する複数の制御回路と、入力される制御信号に応じて動作する複数の動作回路と、複数の動作回路と一対一に対応して設けられ、それぞれが複数の制御回路からの制御信号を受け取り、複数の動作回路のうちの対応する動作回路に、いずれの制御信号を入力するかを選択する複数の中間回路とを備え、複数の制御回路の個数は、複数の動作回路の個数より少ない電気回路を提供する。

(もっと読む)

半導体集積回路、半導体集積回路設計方法及び半導体集積回路設計プログラム

【課題】同一の周波数で動作するデータパス依存関係を有する内部クロックドメインを含む半導体集積回路に対して、テストパターン数を削減することができる半導体集積回路、半導体集積回路設計方法及び半導体集積回路設計プログラムを提供すること

【解決手段】本発明にかかる半導体集積回路は、第1のクロックドメインと、前記第1のクロックドメインと同一の周波数で動作し、前記第1のクロックドメインとデータパスによって接続される第2のクロックドメインと、前記データパスにおけるデータ転送の導通及び遮断を切り替えるパス遮断回路とを備える。

(もっと読む)

ドライバ回路および試験装置

【課題】ドライバ回路が出力する波形の歪みを低減する。

【解決手段】出力端子に高レベル電圧を出力するか、または、低レベル電圧のいずれを出力するかを切り替える、高レベルトランジスタおよび低レベルトランジスタと、与えられる高レベル制御信号に応じて、高レベルトランジスタに高レベル電圧を出力させるか否かを制御する高レベルインバータと、与えられる低レベル制御信号に応じて、低レベルトランジスタに低レベル電圧を出力させるか否かを制御する低レベルインバータと、高レベルインバータのスレショルド電圧に応じた電圧の高レベル制御信号と、低レベルインバータのスレショルド電圧に応じた電圧の低レベル制御信号とを生成する制御信号生成部とを備え、制御信号生成部は、正論理電圧または負論理電圧の少なくとも一方の電圧が異なる高レベル制御信号および低レベル制御信号を生成するドライバ回路を提供する。

(もっと読む)

スキャンテスト回路及びスキャンテスト方法

【課題】メモリ周辺回路に対する遅延故障テストの時間を削減すること。

【解決手段】第1のメモリセル列と、故障したメモリセル列を置き換えるための第2のメモリセル列と、両メモリセル列のうちのいずれのメモリセル列を入力側に設けられた第1の周辺回路に接続するかを切り替える第1の切替回路と、両メモリセル列のうちのいずれのメモリセル列を出力側に設けられた第2の周辺回路に接続するかを切り替える第2の切替回路とを有するメモリに対するスキャンテスト回路であって、両メモリセル列及び両周辺回路の間で少なくとも2通りの接続方法を実現するように両切替回路を制御するテスト優先制御回路を備え、両周辺回路の遅延故障に対するスキャンテストに用いられるスキャンフリップフロップを有するテストポイント回路を両メモリセル列と第1の切替回路との間に備えている。

(もっと読む)

半導体試験装置

【課題】半導体試験装置におけるドライバのタイミング調整をより高精度に行うことを目的とする。

【解決手段】DUTに試験信号Sを印加するために設けた1または複数のドライバ31とドライバ31から出力される試験信号Sを入力してドライバ31のタイミング調整を行う調整用コンパレータ32とタイミング調整のための基準信号SSを発生する基準信号発生部16とを有するテストユニット1を備えた半導体試験装置であって、被試験デバイスが接続される接続ピン21に着脱可能に接続され、ドライバ31から出力される試験信号Sの伝播時間と基準信号発生部16から出力される基準信号SSの伝播時間との差分を計測する伝播時間計測ユニット2と、テストユニット1に備えられ、前記差分に基づいてドライバ31の出力タイミングの補正を行うタイミング補正部23と、を備えている。

(もっと読む)

半導体集積回路、半導体集積回路設計方法、スキャンテストパタン生成方法及びそのプログラム

【課題】スキャンテストにおけるコストを低減することができる半導体集積回路、半導体集積回路設計方法、スキャンテストパタン生成方法及びそのプログラムを提供すること

【解決手段】本発明にかかる半導体集積回路1は、テスト値がスキャンインされ、当該テスト値を組み合わせ回路203に出力する制御用スキャンテスト構成回路と、制御用スキャンテスト構成回路にスキャンインされるテスト値が並列的にスキャンインされるとともに、組み合わせ回路203が制御用スキャンテスト構成回路から出力されたテスト値に基づいて出力する出力値が入力され、当該出力値をスキャンアウトする観測用スキャンテスト構成回路とを備えたものである。

(もっと読む)

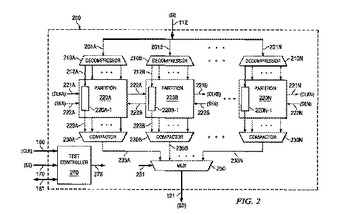

パーティションを設けたスキャン・チェーンを備えた集積回路のスキャンテストにおける向上した制御

パーティションを設けたスキャン・チェーンを備えた集積回路(IC)に実装されたテスト・コントローラが、スキャンテストを実行する際に向上した制御を提供する。一つの側面に従って、テスト・コントローラは、独立しているべき、ICの異なるスキャン・チェーンに対するスキャンテストのスキャンイン、スキャンアウト、及びキャプチャ位相を選択的に制御できる。外部テスターとインタフェースするためにテスト・コントローラに必要なピンの数は、そのテスト・コントローラがサポートし得るパーティションの数より少ない。別の側面に従って、ICは、遷移故障(又はLOS)テストをサポートするため各パーティションに対応するレジスタを含む。別の側面に従って、パーティションを設けたスキャン・チェーンを備えたICが、シリアル−パラレル及びパラレル−シリアル変換器を含み、それにより、スキャンテストをサポートするために必要とされる外部ピンを最小限にする。  (もっと読む)

(もっと読む)

誤り率測定システム

【課題】オーバヘッドを最小限にして誤り率測定の時間短縮を図る。

【解決手段】外部処理装置10は、送信する試験用のコマンドを一つにパッケージ化したパッケージコマンドを一電文で送信し、誤り率測定装置20は、外部処理装置10から送信されたパッケージコマンドを受信した状態のまま出力するとともに、被試験デバイス30の測定結果データを外部処理装置10に対して一電文で送信する主制御部21と、主制御部21からのパッケージコマンドを解析し、予め設定された設定手順に従って試験用コマンドのコマンド内容に基づくコマンド設定を行う副制御部22と、副制御部22によって設定されたコマンド内容に従って被試験デバイス30の誤り率を測定する誤り率測定部23とを備えた。

(もっと読む)

半導体装置解析システム

【課題】初期の故障解析において、機能不具合を内在する半導体装置に対して確実な不具合の再現を可能とし、半導体装置に内蔵された回路のどの部分に問題があるかを解析する手段を提供する。

【解決手段】良品の半導体装置2と、故障品半導体装置3と、良品の半導体装置2と故障品半導体装置3と実機の基板(ボード)4とが配線16で接続され、クロック制御6と比較回路7とを備えた信号共有分割部を備えた解析装置本体の動作により、実機の基板(ボード)4を良品の半導体装置2で動作させつつ、同じタイミングで、故障品半導体装置3を動作させ、その挙動の差異を検知して故障解析を行う。

(もっと読む)

半導体集積回路

【課題】回路規模の小さい自己テスト回路を備えた半導体集積回路を提供する。

【解決手段】

入力データを処理し、入力データよりランダム性の高い出力データを出力する被テスト回路100と、被テスト回路100の自己テスト動作時に、被テスト回路100に入力する初期の入力データを保持する記憶部210と、被テスト回路100が入力データを処理し、出力する出力データを被テスト回路100の入力データとしてフィードバックするフィードバック部220と、フィードバック部220が被テスト回路100の出力データを被テスト回路100の入力データとしてフィードバックする回数を制御する制御部230と、被テスト回路100が出力する出力データと期待値とを比較する比較部240と、を有する自己テスト回路。

(もっと読む)

201 - 220 / 1,025

[ Back to top ]