Fターム[2G132AA01]の内容

Fターム[2G132AA01]の下位に属するFターム

PLA、PLD、ゲートアレイ (59)

CPU、順序回路 (151)

カウンター、レジスター、フリップフロップ (33)

トライステート、双方向素子

多値(3値以上)論理回路 (1)

メモリ回路 (731)

Fターム[2G132AA01]に分類される特許

141 - 160 / 1,025

回路シミュレーション方法および回路シミュレーション装置

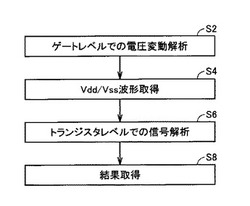

【課題】精度の高い回路シミュレーションを実行する回路シミュレーション方法を提供する。

【解決手段】ゲートレベルでの電圧変動解析ステップを実行する(ステップS2)。ゲートレベルでの電圧変動解析ステップは、チップTP全体に対して実行する。そして、次に、電圧変動解析ステップに従う電源電圧および接地電圧(Vss)の電圧波形を取得するステップを実行する(ステップS4)。次に、トランジスタレベルでの信号解析ステップを実行する(ステップS6)。トランジスタレベルでの信号解析解析ステップは、チップTP全体よりも範囲の狭い例えば、すべてではない、1つ又はそれ以上の機能モジュールに対して実行する。そして、信号解析ステップに従う信号解析結果を取得するステップを実行する(ステップS8)。

(もっと読む)

テスト回路およびテスト回路の制御方法

【課題】テスト専用端子の増加を防ぎ、テストの長時間化を防止する。

【解決手段】テストアクセスポートに入力されるテスト信号に応じて、回路ブロックの試験を行うテスト回路であって、第1のTAP制御部及びその制御下にある第2のTAP制御部と、第1のTAP制御部のテスト動作の無効と、記憶情報の書き換えを不可に制御する第1の情報を記憶する第1のレジスタと、第1の情報に応じて記憶情報の書き換えを不可に制御され、第2のTAP制御部のテスト動作の有効・無効の制御する第2の情報を記憶する第2のレジスタと、外部から入力されるTDI信号に応じて前記第1、2のレジスタが書き換え不可状態を解除する制御回路と、を有するテスト回路。

(もっと読む)

半導体集積回路装置

【課題】ユーザ回路における消費電流をより低減する。

【解決手段】ユーザ回路13と、ユーザ回路13のスキャンテストに係るデータを保持するスキャンフリップフロップ回路FF11〜FF1nと、スキャンフリップフロップ回路FF11〜FF1nの出力値および一定の論理値のいずれか一方をユーザ回路13に出力するゲート回路(AND10、AND11〜AND1n)と、を備え、スキャンテストに係るシーケンスにおいて、一定の論理値をユーザ回路13に出力するようにゲート回路(AND10、AND11〜AND1n)を制御する。

(もっと読む)

テスタシミュレーション装置、テスタシミュレーションプログラムおよびテスタシミュレーション方法

【課題】論理検証およびテストデバッグに要する総時間の短縮化を図ることを目的とする。

【解決手段】テスタによるDUTの試験を仮想的にシミュレーションするテスタシミュレーション装置1は、DUTの動作をシミュレータ上でモデル化した仮想デバイス11と、仮想デバイス11の論理検証を行うための検証シナリオの入力パターンを仮想デバイス11に印加し、仮想デバイス11から出力される応答パターンを入力して期待値パターンと比較して良否判定を行う仮想テスタ12と、入力パターンおよび期待値パターンを仮想テスタ12から取得し、入力パターンおよび応答パターンが正常なものであるときに、取得した入力パターンおよび期待値パターンをDUTの実試験を行うためのテストパターンとして生成するテストパターン生成部14と、を備えている。

(もっと読む)

スキャンテスト装置及びスキャンテスト方法

【課題】回路規模が増大することなく、テストデータを入力する入力端子の個数を削減できるスキャンテスト装置及びスキャンテスト方法を提供すること。

【解決手段】本発明にかかるスキャンテスト装置1は、テストデータ入力端子、OR素子17、スキャンフリップフロップ12を備える。テストデータ入力端子には、第1のスキャンチェーンに対する第1のテストデータと第2のスキャンチェーンに対する第2のテストデータとを少なくとも含むテストデータが入力される。OR素子17は、テストデータが入力され、クロック信号とは非同期であるマスク信号に基づいて、第2のテストデータをマスクして、第1のテストデータを出力する。スキャンフリップフロップ12は、前記第1のスキャンチェーンの先頭に配置され、OR素子17が出力した第1のテストデータに対応する非同期テストデータを保持する。

(もっと読む)

データラッチ回路およびそれを用いた試験装置

【課題】多様な信号形式のDUTからのデータを取り込み可能なデータラッチ回路を提供する。

【解決手段】データ入力端子INは、シリアル形式のデータ信号DINが入力される。n個(nは2以上の整数)のクロック入力端子CLK1〜CLKnは、それぞれにクロック信号CLK1〜CLKnが入力される。ある入力フリップフロップFFiは、データ信号DINを対応するクロック信号CLKiに応じたタイミングでラッチする。シリアルパラレル変換器SPiは、シリアル形式のデータ信号DINを対応するクロック信号CLKiを用いてパラレル形式の中間データ信号DINTiに変換する。データセレクタMUX1は、n個の中間データ信号DINT1〜nのうち選択信号SELに応じたひとつを選択する。

(もっと読む)

スキャンモード信号生成回路および半導体集積回路

【課題】半導体集積回路の端子数の増加を抑制することができるスキャンモード信号生成回路および半導体集積回路の提供を図る。

【解決手段】スキャンモード制御信号SMCを受け取るスキャンモードフリップフロップ41と、該スキャンモードフリップフロップの出力信号を遅延してタイミング調整を行うタイミング調整用回路42と、前記スキャンモード制御信号および前記タイミング調整回路の出力信号を受け取ってスキャンモード信号SMを生成するスキャンモード用論理回路43と、を有するように構成する。

(もっと読む)

スキャンテスト回路、半導体集積回路

【課題】縮退故障テストだけでなく遅延故障テストまでも視野に入れた、制御性向上の為のテストポイントを挿入するスキャンテスト回路を提供すること。

【解決手段】本発明に係るスキャンテスト回路は、論理回路から出力された信号が入力される、スキャンチェーンを構成するスキャンレジスタ11と、スキャンレジスタ11の後段に設けられ、スキャンレジスタ11からの出力信号を反転するインバータ12と、スキャンレジスタ11の前段に設けられ、外部から入力される入力信号又はインバータ12から出力される信号のいずれかを選択する第1セレクタ13と、インバータ12の後段に設けられ、入力信号又はインバータから出力される信号のいずれかを選択する第2セレクタ14とを備える。

(もっと読む)

半導体試験装置

【課題】高速側判定結果データおよびDUT判定結果データを同期して表示することが可能な半導体試験装置を実現する。

【解決手段】異なる速度のパターンデータである低速側パターンデータおよび高速側パターンデータを用いて被試験対象デバイスの試験を行い、被試験対象デバイスからの出力信号に応じて低速側判定結果データと高速側判定結果データを取得し、低速側判定結果データと高速側判定結果データの論理和であるDUT判定結果データと高速側判定結果データを表示部に表示する半導体試験装置において、低速側パターンデータの区切りを示す低速区切り信号の周期毎に高速側判定結果データに含まれるフェイル数をカウントし、カウント値を記憶するフェイル制御部と、カウント値に従って高速側判定結果データをDUT判定結果データに同期させて表示部に表示させる演算制御部とを備える。

(もっと読む)

試験測定機器及び方法

【課題】ディスパリティ・エラーから独立してシンボル・エラー・レート及びビット・エラー・レートを測定する。

【解決手段】被試験信号を受け(505)、被試験信号内の開始シーケンスを検出し(510)、開始シーケンスに応答して同期信号を発生する(515)。同期信号に応答して基準試験パターンをメモリから出力する(520)。メモリからの基準試験パターンの8bコード化シンボルを被試験信号の8bコード化シンボルと比較して、シンボル・エラー・レート値を発生する(525)。基準試験パターン及び被試験信号を8bコード化フォーマットから10bコード化フォーマットに変換し(530)、10bコード化基準試験パターンを10bコード化被試験信号とビット毎に比較する(545)。

(もっと読む)

半導体装置および制御回路

【課題】実動作時における内部クロック信号のジッタ量を検出し、検出したジッタ量を外部で利用可能に出力できる半導体装置を得ること。

【解決手段】クロック生成回路が出力しているクロック信号と、該クロック信号を少なくとも1周期遅延した遅延クロック信号との位相差に基づき前記クロック信号に含まれるジッタ成分を検出するジッタ検出部と、前記検出されたジッタ成分を電圧信号に変換する増幅回路を有する増幅部と、前記変換された電圧信号を外部へ出力するためのジッタ出力端子とを備えたことを特徴とする。

(もっと読む)

スキャンシフト動作中の瞬時電圧ドループを低減するためのシステム及び装置

【課題】スキャンシフト動作中の瞬時電圧ドループ(IVD)を低減する。

【解決手段】入力クロック信号は、第1及び第2グループのクロックゲーティングセル102A、102Bの第1及び第2遅延素子116、132によって第1及び第2遅延時間だけ遅延されて、第1及び第2グループのフリップフロップ104A、104Bに入力される。第1及び第2遅延時間は変更可能であり、これら時間が相違するように設定することにより、第1及び第2遅延時間のFFを異なるタイミングで切り替えて、IVDを低減する。

(もっと読む)

試験装置およびデバイスボード

【課題】簡易な構成で、多様な品種の被試験デバイスに対応する基準レベルを生成する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスに入力する電圧を出力する出力部と、出力部に対して交換可能に接続されるデバイスボードと、デバイスボードに設けられ、デバイスボード毎に異なる特性を有する品種対応素子と、出力部に接続されたデバイスボードに設けられた品種対応素子の特性に応じて、出力部が出力する電圧の基準レベルを生成する基準レベル生成部とを備え、デバイスボードは、予め定められた品種の被試験デバイスを載置し、且つ、被試験デバイスの品種毎に出力部に対して交換可能に接続され、品種対応素子は、対応する被試験デバイスの品種に応じた特性を有する試験装置を提供する。

(もっと読む)

半導体集積回路のテスト回路およびテスト方法

【課題】テスト時に必要となるテスト用の外部接続ピンを追加することなく、テスト対象のマクロ等をテストすることができる半導体集積回路のテスト回路およびテスト方法を提供する。

【解決手段】テスト回路は、複数のフリップフロップを直列に接続して構成され、クロック信号が入力される毎に、テスト用のシリアルデータを順次シフトするシフトレジスタと、あらかじめ決定された所定パターンのシリアルデータが、シフトレジスタの、あらかじめ決定された少なくとも1つのフリップフロップに設定されたことを検出すると、アクティブ状態の出力制御信号を出力する設定検出回路と、設定検出回路から入力された出力制御信号を用いて、シフトレジスタの複数のフリップフロップの出力信号の出力制御を行う出力制御回路とを備える。

(もっと読む)

半導体装置の故障検出方法、試験装置、及びプログラム

【課題】ブリッジ故障検出用の追加的なテストパタンを用いることなくブリッジ故障の検出を可能とし、また、ブリッジ故障の検出漏れを減らす。

【解決手段】スキャンチェインのシフト操作によってスキャンチェインに入力論理値を伝播させる。次に、クロック線にクロックパルスを入力することによって、入力論理値をスキャンチェインから組合せ回路に供給する。続いて、クロック線の電位を所定の電位に固定した状態で半導体装置の電源電流を測定することによって、クロック線と組合せ回路内の信号線との間のブリッジ故障を検出する。さらに続いて、クロック線にクロックパルスを入力することによって、スキャンチェインに出力論理値を伝播させる。最後に、出力論理値を観測することによって、組合せ回路内における縮退故障又はブリッジ故障の発生を検出する。

(もっと読む)

半導体集積回路用テスト回路

【課題】トランジスタの特性と配線系における配線負荷の特性とを高精度で分離でき、配線負荷に大きな影響を及ぼす層間絶縁膜等の特性を評価できる技術を提供することである。

【解決手段】(2k+1:kは1以上の整数)個のインバータを具備したリング発振回路を有してなり、隣接するインバータの間に、各々、同一インピーダンス値の負荷回路が設けられてなる半導体集積回路用テスト回路。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

半導体装置並びにデータ保持回路の故障検出システム及び故障検出方法

【課題】半導体装置に搭載される複数のデータ保持回路の故障を検出するためのテスト時間を短縮すること。

【解決手段】本発明の第1の態様にかかる半導体装置は、同一の入力値を入力するN個(Nは、3以上の奇数)のフリップフロップ回路FF1〜FF3からの出力値の内、過半数を占める多数値信号Maを出力する多数決論理回路MJRと、N個のフリップフロップ回路FF1〜FF3からの出力値の内、過半数未満である少数値信号Miを出力する少数値判定回路MIRと、を備える。

(もっと読む)

半導体集積回路のテスト回路、テスト方法、テストパタン作成方法、及びテストパタン作成プログラム

【課題】複数のクロックドメインを用いる半導体集積回路のテスト回路において、ダブルクロックを印加するタイミングを任意に設定することを可能にする。

【解決手段】複数のトリガクロックのうち、被テスト回路の複数のクロックドメインのクロックうちの選択クロックに対応する選択トリガクロックにおいてダブルクロックの抽出トリガを検出するとイネーブル信号を出力するダブルクロック抽出回路と、イネーブル信号をトリガとして選択クロックからダブルクロックを抽出するクロックマスク回路と、ダブルクロックを入力して被テスト回路に対してスキャンテストを実行するスキャンフリップフロップとを備える。ダブルクロック抽出回路と、クロックマスク回路と、スキャンフリップフロップとは、複数のクロックドメインに対応して設けられる。抽出トリガは、複数のクロックドメイン間においてダブルクロックを出力するべきタイミング関係に基づいて選択トリガクロックの各々に設定される。

(もっと読む)

被検査装置用インタフェース回路

【課題】 半導体装置の大型化を抑制できる被検査装置用インタフェース回路を提供する。

【解決手段】 検査装置4により検査される被検査装置5に設けられた端子回路7と接続されて、検査装置4と非接触で通信する第1の入出力回路6を備え、かつ、端子回路7が被検査装置5に信号を入力する回路の場合には、第1の入出力回路6は入力回路により形成され、端子回路7が被検査装置5から信号を出力する回路の場合には、第1の入出力回路6は出力回路により形成されている。

(もっと読む)

141 - 160 / 1,025

[ Back to top ]