Fターム[2G132AB04]の内容

Fターム[2G132AB04]の下位に属するFターム

Fターム[2G132AB04]に分類される特許

1 - 20 / 84

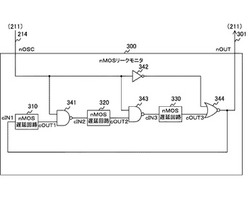

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

電子部品、測定方法および監視装置

【課題】接合部の損傷を事前に検知する。

【解決手段】電子部品は、第1部材と、第2部材と、接合部と、測定部とを備える。第1電極は、第1部材上に形成される。第2電極は、第1部材上の、第1電極が形成された領域の周囲の領域に形成される。第3電極は、第2部材に形成される。第2電極が第2部材に形成され、第3電極が第2部材の第2電極が形成された領域の周囲の領域に形成されてもよい。接合部は、第1電極と第2電極と第3電極と接合する。測定部は、第1電極および第2電極のうち少なくとも一方を含む接続経路の電気特性を測定する。

(もっと読む)

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

不揮発性半導体記憶装置及びその試験方法

【課題】電源投入により自走的にメモリセルアレイの動作テストを実行する。

【解決手段】一つの実施形態によれば、不揮発性半導体記憶装置は、不揮発性半導体記憶装置は、ロムヒューズブロックを有するメモリセルアレイ、自走テスト部を有するコントローラ、及びコマンドレジスタを有する。不揮発性半導体記憶装置は、電源投入によりメモリセルアレイの自走テストを実行する。

(もっと読む)

半導体装置

【課題】低周波数のクロックしか供給できないバーンインテスタを用いた場合であっても、テストに長時間を要するディスターブテストを、高周波数で実行可能な半導体装置を提供する。

【解決手段】テスト動作モードにおいて、ロウアドレスバッファ部12dにより、第1のワード線の位置を示すロウアドレスを取り込む。制御回路18a及びタイミング制御回路18bは、第1のワード線とビット線対を共有する第1のワード線とは異なる第2のワード線を選択し、当該ワード線に接続されるメモリセルのリフレッシュ動作を、外部から供給されるクロック信号の第1の周波数に比べて高い第2の周波数で実行する、ことを特徴とする。

(もっと読む)

半導体集積回路及び半導体集積回路のテスト方法

【課題】内部に備えられた順序回路の動作検証にかかる時間を短縮できる半導体集積回路を提供すること

【解決手段】半導体集積回路1は、入力信号3が論理回路4を通過した信号である通過信号が供給されるD型F/F10を備える。遅延量測定回路6は、論理回路4により生じる入力信号3の遅延量を、D型F/F10の動作検証前に測定する。遅延制御回路5は、D型F/F10の動作検証の際に、入力信号3を遅延量測定回路6が測定した遅延量だけ遅延させた遅延信号を生成する。比較回路11は、D型F/F10の動作検証の際に、遅延制御回路5が生成した遅延信号をD型F/F10の入力とした場合のD型F/F10からの出力と、期待値と、を比較してD型F/F10の動作検証を行う。

(もっと読む)

プリント基板劣化検査装置および劣化検査方法

【課題】プリント基板を破壊することなく、故障発生前にプリント基板またはプリント基板上の回路(検査部位)の修理もしくは交換を容易にできる劣化検査装置を提供する。

【解決手段】プリント基板劣化検査装置は、パルス波を出力するパルス発生器51と、プローブ32と、オシロスコープ53と、コンピュータ60とを備える。プローブ32は、検査部位と接続されたプリント基板上の配線パターンにパルス波を印加するために用いられる。オシロスコープ53は、パルス波がプリント基板から反射された反射波を、プローブ32を介して測定する。コンピュータ60は、プリント基板または検査部位に対して測定された反射波と比較のための参照用波形に基づいて、プリント基板あるいは検査部位の劣化を判定する。

(もっと読む)

スイッチング素子の劣化診断回路及びその動作方法

【課題】より簡素な構成でより精度が良いスイッチング素子の劣化診断回路およびその動作方法を提供すること

【解決手段】スイッチ部11及びスイッチ部11に対して接続された容量部12を含むと共に、入力波形に対してローパスフィルタ処理を実行するローパスフィルタ部1と、前記入力波形の入力に応じたローパスフィルタ部1の出力と参照電圧とに基づいて、ローパスフィルタ部1に含まれるスイッチ部11の状態を示す状態値を生成する状態判定部2を備える劣化診断回路。

(もっと読む)

電子機器用の埃試験装置および埃試験方法

【課題】長期間使用した電子機器における埃の付着状況を適切に再現可能な、電子機器用の埃試験装置および埃試験方法を提供する。

【解決手段】埃Dを封入するための筐体11と、筐体内に電子機器30を配置するための配置台13と、第1の周期で筐体内に埃を飛散させるための第1の送風部15と、第1の周期より長い第2の周期で、電子機器の通気口31に付着した埃を吹飛ばすための第2の送風部17とを備える。通気口に詰まった埃を周期的に吹飛ばすことで、試験開始後の早い段階で通気口が完全に詰まることがなく、試験の継続が可能となるので、長期間使用後の埃の付着状況を適切に再現することができる。

(もっと読む)

素子寿命予測方法及び素子寿命予測機能を備えた回路基板

【課題】回路基板に搭載した電子部品の接続部の破壊による電子部品の寿命を、電子部品の接続部が実際に破壊する前に予測することを可能にする。

【解決手段】

電子部品を実装した回路基板に熱伝導部材を介して実装した半導体装置の寿命を予測する方法において、回路基板上に第1の熱伝導部材を介して実装した半導体装置と回路基板上に第1の熱伝導部材よりも熱伝導率が小さい第2の熱伝導部材を介して実装した余命診断部とに同期して通電し、同期して通電することを繰返すことにより余命診断部で発生する故障を検出し、検出した余命診断部に発生した故障から半導体装置の寿命を予測する

ようにした。

(もっと読む)

試験測定機器及び方法

【課題】ディスパリティ・エラーから独立してシンボル・エラー・レート及びビット・エラー・レートを測定する。

【解決手段】被試験信号を受け(505)、被試験信号内の開始シーケンスを検出し(510)、開始シーケンスに応答して同期信号を発生する(515)。同期信号に応答して基準試験パターンをメモリから出力する(520)。メモリからの基準試験パターンの8bコード化シンボルを被試験信号の8bコード化シンボルと比較して、シンボル・エラー・レート値を発生する(525)。基準試験パターン及び被試験信号を8bコード化フォーマットから10bコード化フォーマットに変換し(530)、10bコード化基準試験パターンを10bコード化被試験信号とビット毎に比較する(545)。

(もっと読む)

評価用半導体チップ、評価システム及びそのリペア方法

【課題】半導体チップを評価する技術を提供する。

【解決手段】

シリコン基板の一方の面に、複数領域からなる抵抗測温体としての金属配線膜101、及び、1つ又は複数領域からなるヒータとしての金属配線膜102の少なくとも何れかと、金属配線膜101及び金属配線膜102を実装基板と接続するための電極103と、が積層された半導体チップを実装基板に実装して、金属配線膜101を電流計及び電圧計と、金属配線膜102を電源と、電気的に接続することで、半導体チップの上記各領域における測温及び加熱、及び、その温度プロファイルが評価可能な評価システムを提供する。

(もっと読む)

プローブカードの搬送機構、プローブカードの搬送方法及びプローブ装置

【課題】プローブカードが大型化しても機械的強度を十分に確保することができると共にプローブカードの交換作業を円滑に行うことができるプローブカードの搬送機構を提供する。

【解決手段】本発明のプローブカードの搬送機構は、プローブカードを搬送する第1のカード搬送機構11と、第1のカード搬送機構11とインサートリング54との間でプローブカード56を搬送する第2のカード搬送機構12と、を備え、第1のカード搬送機構11は、ヘッド旋回駆動機構57側に設けられ且つ第2のカード搬送機構12との間でプローブカード56の受け渡しを行う進退動可能なカード保持具13を有し、第2のカード搬送機構12は、第1のカード搬送機構11とインサートリング54の間でプローブカード56を搬送する載置台52と、載置台52の周囲に互いに所定間隔を空けて昇降可能に設けられ第1、第2、第3昇降機構16A、16B、16Cと、を有する。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】実際の動作条件下においてエレクトロマイグレーションの劣化現象を検知すると共に、故障の兆候を検知することが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路10は、カウンタ回路6と、遅延クロック信号56を生成する遅延素子5と、クロック信号52のクロックサイクル毎にトグルするデータを入力する第1のフリップフロップ1と、第1のフリップフロップ1からの出力信号を入力する配線4と、遅延クロック信号56に基づき駆動し、配線4からの出力信号を入力する第2のフリップフロップ2と、クロック信号52に基づき駆動し、第1のフリップフロップ1からの出力信号を入力する第3のフリップフロップ3と、第2及び第3のフリップフロップ2、3からの出力信号の排他的論理和を出力する排他的論理和回路7と、を有する。

(もっと読む)

劣化検出回路

【課題】半導体集積回路の素子(特にトランジスタ)の劣化を正確に測定する。

【解決手段】リングオシレータ(1)の周波数情報を出力する周波数測定器(2)と、リングオシレータ(1)を良否判定する判定回路(7)とを具備する劣化検出回路(8)を構成する。判定回路(7)は、周波数情報と、リングオシレータ(1)の動作環境と発振周波数との関連性を示す環境依存特性情報(15)(16)(17)と、リングオシレータ(1)の発振周波数として許容される許容範囲情報(6)と、リングオシレータ(1)の動作時の環境特定情報(13)(14)とを受けとる。そして、環境特定情報(13)(14)と環境依存特性情報(15)(16)(17)とに基づいてリングオシレータ(1)の理想的な発振周波数である理想周波数を算出し、周波数情報が、許容範囲情報(6)に対応する条件に含まれているか否かを判定する。

(もっと読む)

電子機器及びストレス試験装置

【課題】発生頻度の少ない不具合が発生した場合に、その発生原因となっている電子回路を容易に特定できる電子機器を、提供する。

【解決手段】電子機器は、複数の電子回路(LSI10等)のそれぞれとして、容量の異なる2種のバイパスコンデンサとして機能可能なバイパスコンデンサ回路17、外部から所定の指示が与えられたときにバイパスコンデンサ回路17を容量が少ない方のバイパスコンデンサとして機能させる制御回路18が設けられている回路を、備える。

(もっと読む)

半導体装置

【課題】開発の早期において、様々な条件におけるクロストーク耐性を確認することができる半導体装置を提供する。

【解決手段】信号発生回路3と、遅延回路40、41、42、43、…、4mと、遅延回路50、51、52、53、…、5mと、出力バッファ70、71、72、73、…、7mそれぞれに対応して設けられ、遅延回路40、41、42、43、…、4mから出力された信号または遅延回路50、51、52、53、…、5mから出力された信号のいずれかを選択して対応する出力バッファ70、71、72、73、…、7mに出力する選択回路60、61、62、63、…、6mと、を備える。

(もっと読む)

半導体チップ調整装置及び前記装置を用いた検査方法

本発明は半導体チップ調整装置及び検査方法を提供する。前記装置は一又は複数の半導体チップ(C)を受け入れるチップ温度制御手段(TE1,TE2,TE3)と対応する数のチップ結合台(S)とマザーボード(30)とを備える。前記制御手段は、温度制御用流体が流されるように構成され且つ前面(VS)から後面(RS)へ至る対応する数のリセス(GA)を有する基体(G)を備える。前記チップ結合台(S)は、前記基体(G)に熱的接触状態で前記リセス(GA)に挿入され、前面(VS)にチップ受入領域(SM)を且つ内部に前記チップ受入領域(SM)内の前記半導体チップ(C)に対して電気信号を送受信する電気信号配線手段(D1,D2)を有している。前記マザーボード(30)は、前記チップ結合台(S)の配線手段(D1,D2)が前記マザーボード(30)における配線手段(32)に電気的に接続されるように前記後面(RS)に装着されている。 (もっと読む)

劣化検出回路、劣化検出システム及び劣化検出方法

【課題】回路規模を増大することなくトランジスタの劣化具合を正確に評価することができる電圧出力回路、劣化検出システム及び劣化検出方法を提供すること

【解決手段】本発明にかかる劣化検出回路10は、電源(VDD)100と電源(VDD)100よりも電位が低い電源(GND)110との間に設けられたMOSトランジスタ30と、電源(VDD)100と電源(GND)110との間においてMOSトランジスタ30と直列に接続され、MOSトランジスタ30の劣化進行度よりも遅い劣化進行度を有する抵抗部20と、MOSトランジスタ30と抵抗部20との接点における電圧を、MOSトランジスタ30の劣化度を測定するために出力する劣化度測定用出力端子40と、を備えるものである。

(もっと読む)

1 - 20 / 84

[ Back to top ]