Fターム[2H092JA23]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 種類 (8,621) | FET(半導体基板を使用したもの) (162)

Fターム[2H092JA23]に分類される特許

1 - 20 / 162

液晶表示装置及びその製造方法

光変調装置

電気光学装置及び電子機器

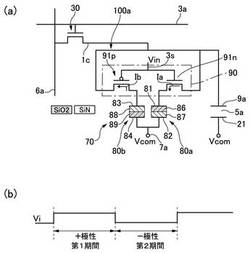

【課題】極性反転駆動を行う際、極性反転に伴って、画素電極に導通する保持容量を切り換えることのできる電気光学装置、および電子機器を提供する。

【解決手段】電気光学装置において、画素電極9aの電位が共通電極21の電位より高い第1期間では、第1保持容量80aが画素電極9aに導通状態となるので、第1電極81、第1誘電体層86(第1絶縁材料/シリコン酸化膜/SiO2)、第2誘電体層87(第2絶縁材料/シリコン窒化膜/SiN)、および第2電極82に向けて電流が流れ、電荷が蓄積される。これに対して、画素電極9aの電位が共通電極21の電位より低い第2期間では、第2保持容量80bが画素電極9aに導通状態となるので、第4電極84、第4誘電体層89(第1絶縁材料/シリコン酸化膜/SiO2)、第3誘電体層88(第2絶縁材料/シリコン窒化膜/SiN)、および第3電極83に向けて電流が流れ、電荷が蓄積される。

(もっと読む)

液晶表示素子および液晶表示装置

【課題】高い動作信頼性を有する表示素子を提供する。

【解決手段】この液晶表示素子は、透明基板と、その一方の面に形成された透明電極とを有する透明電極基板と、液晶層と、液晶層を挟んで透明電極と対向する領域に位置する複数の画素電極、およびそれ以外の領域に位置する第1の導電膜を含む第1の層と、第1の導電膜と重複する領域に位置する第2の導電膜を含む第2の層とを順に有する画素電極基板とを備える。ここで、第1および第2の導電膜の少なくとも一方が電気的に孤立している。

(もっと読む)

半導体装置

【課題】単極性のTFTを用いて構成するデジタル型式の表示装置において、消費電流を低減することの出来る回路を提供する。

【解決手段】デジタル映像信号の保持を行うラッチ回路であって、TFT101の入力電極にデジタル映像信号が入力されると、TFT101の出力電極からは非反転出力信号が出力され、TFT102およびTFT103の出力電極からは反転出力信号が出力されるラッチ回路を提供する。出力を非反転、反転の2系統得られるため、後段のバッファを駆動する際に、電源間の直流パスが生ずる期間を短くすることが出来、消費電流の低減に寄与する。

(もっと読む)

液晶装置、液晶装置の製造方法、電子機器

【課題】光の干渉による色ムラや表示ムラが低減され、明るい表示品質が得られる液晶装置、液晶装置の製造方法、この液晶装置を備えた電子機器を提供すること。

【解決手段】液晶装置は、素子基板10と、素子基板10と対向配置された透光性の対向基板20と、素子基板10と対向基板20との間に挟持された液晶層50と、素子基板10の液晶層50側に形成された光反射性の複数の画素電極15と、対向基板20の液晶層50側に形成された導電性の第1透光性膜22aと、第1透光性膜22aの液晶層50側に形成され、第1透光性膜22aよりも屈折率が小さい絶縁性の第2透光性膜22bと、第2透光性膜22bの液晶層50側に形成され、第2透光性膜22bよりも屈折率が大きい導電性の第3透光性膜22cと、を備え、複数の画素電極15を有する画素領域における液晶層50の厚みdが、所定の値d0に対して±10%以内となっている。

(もっと読む)

半導体装置

【課題】1画素に複数の副画素を設けることにより視野角特性を向上させた表示装置を提

供することを課題とする。又は、複数の副画素を設けた場合であっても開口率の低下を抑

制する表示装置を提供することを課題とする。

【解決手段】第1の副画素、第2の副画素及び第3の副画素を有する画素と、走査線と、

信号線と、第1の容量配線と、第2の容量配線と、第3の容量配線とを設け、第1の副画

素〜第3の副画素にそれぞれ、第1の容量素子〜第3の容量素子の一方の電極及び第1の

容量配線〜第3の容量配線に電気的に接続する画素電極とを設け、第1の容量配線及び第

2の容量配線の電位を変化させ、第3の容量配線の電位を概略一定に保持する構成とする

。

(もっと読む)

電気光学装置および投射型表示装置

【課題】反射部を構成する溝の構造を改良して、入射した光をより効率よく画素電極に向かわせることのできる電気光学装置、および投射型表示装置を提供すること。

【解決手段】電気光学装置100において、第2基板20の基板本体20w(透光性基板)には、隣り合う画素電極9aの間(画素間領域10f)に向けて開口する第1溝260が形成されている。また、基板本体20wの一方面20sおよび第1溝260の側面261、262には透光膜25が形成されており、かかる透光膜25によって、第1溝260と平面視で重なる領域には、第1溝260より深くて第1溝260より幅が狭い第2溝265が形成されている。このため、第2溝265の側面266、267を反射面として利用し、画素間領域10fに向かおうとする光を画素電極9aに向かわせる。

(もっと読む)

薄膜半導体装置と薄膜半導体装置を用いた表示装置

【課題】IGZO等の酸化物半導体膜からなる薄膜半導体装置において、無酸素雰囲気中で加熱しても酸素が酸化物半導体膜に拡散してTFT特性を発現する薄膜半導体装置を提供すること。

【解決手段】薄膜半導体装置は、ガラスの基板20、ゲート電極23G,ゲート絶縁膜21、ソース電極23S、ドレイン電極23D、IGZOの酸化物半導体膜24、二酸化マンガン(MnO2)の酸素放出絶縁膜25、保護膜22からなる。薄膜半導体装置は、蛍光表示装置等の薄膜形成時における加熱工程、焼成工程、封着工程において加熱すると、酸素が酸素放出絶縁膜25から放出されて酸化物半導体膜24に拡散してTFT特性を発現する。

(もっと読む)

液晶パネル及びそれを用いた電子機器並びに投写型表示装置

【課題】半導体装置でパシベーション膜として一般的に使用されている減圧CVD法による窒化シリコン膜は、膜厚の10%程度のばらつきが生じるので、これを反射型液晶パネルに用いると、パシベーション膜の膜厚のばらつきによって反射率が大きく変化したり、液晶の屈折率が変動したりするという不具合がある。

【解決手段】基板(1)上に反射電極(14)がマトリックス状に形成されるとともに各反射電極に対応して各々トランジスタが形成され、前記トランジスタを介して前記反射電極に電圧が印加されるように構成された液晶パネル用基板において、パシベーション膜(17)として、膜厚が500〜2000オングストロームの酸化シリコン膜を使用し、入射光の波長に応じて膜厚を適当な値に設定するようにした。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】シフトレジスタなどに用いられる新規な回路を提供する。

【解決手段】基本構成は、第1のトランジスタ〜第4のトランジスタと、第1の配線〜第

4の配線を有する。第1の配線には電源電位VDDが供給され、第2の配線には電源電位

VSSが供給されている。第3の配線、第4の配線には2値の値を持つデジタル信号が供

給される。このデジタル信号は、高レベルのときには電源電位VDDと同電位となり、低

レベルのときには電源電位VSSと同電位である。第3の配線と第4の配線の電位の組み

合わせは4とおりあるが、第1のトランジスタ〜第4トランジスタは、いずれかの電位の

組み合わせによりオフさせることができる。つまり、定常的にオン状態となるトランジス

タがないため、トランジスタの特性劣化が抑制することができる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】画素電極の間隙からの光が駆動基板内部に到達しないようにすることにより、確実に光リークを低減する。

【解決手段】液晶表示装置100は、駆動基板5上に形成されている複数の画素電極11の下層に配置された層間絶縁膜15における、隣接する画素電極11の隙間の下方の位置に、その隙間よりも広い幅の遮光埋め込み層28が形成されている。遮光埋め込み層28は、隣接する画素電極11の隙間から入射しようとする光Bを遮光し、層間絶縁膜15への入射を阻止するため、駆動基板5に形成されている画素回路へ光が入射することはなく、よって光リーク不良を確実に防止することができる。

(もっと読む)

液晶表示素子

【課題】より小型化、低コスト化した液晶表示素子を提供する。

【解決手段】シリコン基板1とガラス基板2は回路基板3上の電極パッド14、電極パッド15と導通をとるため、液晶11を介し、均一な位置関係でシール材9により貼り合わせて液晶表示素子を構成している。前記シリコン基板1に形成された画素電極12は貫通電極4を介して、導電性材料16(例えば金ペースト、はんだ等)によって回路基板3の電極パッド14と電気的に接続される。また、ガラス基板2に形成された対向電極6は、これと対向する位置に配置された前記シリコン基板1上の貫通電極8と導電性樹脂7を介して接続され、貫通電極8の下面側において導電性材料16(例えば金ペースト、はんだ等)を介して回路基板3の電極パッド15と接続されている。前記画素電極12と前記対向電極6とはそれぞれ異なった電位が供給される。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

液晶表示装置

【課題】ソースフォロワ出力の線形領域を従来より拡大する。

【解決手段】画素10内のソースフォロワ用PMOSトランジスタTr13及びTr14は、ゲートが保持容量Cs1、Cs2に接続されて常にオン状態で使用されるため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのみが+0.5Vに設定され、ノーマリーオン状態とされる。ソースフォロワ用PMOSトランジスタTr13及びTr14の電流値は定電流負荷トランジスタTr7で制御し、オンオフは定電流負荷トランジスタTr7とスイッチング用NMOSトランジスタTr5、Tr6で制御する。また、トランジスタTr5、Tr6が介在し出力可能の電圧範囲が存在するため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのシフトによって線形性を保つ領域が最大になるように最適化する。

(もっと読む)

アクティブマトリクス基板、電気光学装置及び電子機器

【課題】レイアウトの自由度を高め、基板上の熱源による表示品質の低下を防止できるアクティブマトリクス基板を提供する。

【解決手段】走査線22、データ線24及び画素26を含む画素回路と、半導体基板の一辺に沿って形成された複数のパッドを含む入力パッド部30と、高速シリアルインターフェース回路40と、高速シリアルインターフェース回路からの出力に基づいて階調データを生成するロジック回路50と、階調データに基づいて複数のデータ線を駆動するデータ線駆動回路60と、制御信号に基づいて走査線を駆動する走査線駆動回路70とを有し、半導体基板の一辺と画素回路との間で、該一辺側から順に、入力パッド部、高速シリアルインターフェース回路及びロジック回路が配置され、ロジック回路と画素回路との間に、データ線駆動回路及び走査線駆動回路の一方が配置される。

(もっと読む)

反射型液晶表示装置及び液晶プロジェクターシステム

【課題】 遮光だけでは抑制できない、入射してしまう光により生じる電子(ホール)による影響を抑制する。

【解決手段】 トランジスタのドレイン領域34よりも、多数キャリアに対して、ドレイン領域における電圧とQ(単位電荷量)との積の基準値よりも低いポテンシャルとされる領域36を設けるか、もしくはドレイン領域の周りにポテンシャル障壁を設ける。かかる構成により、フローティングとなる反射電極30と接続されたドレイン領域34の回りのポテンシャル制御を行い、半導体基板内に発生した光キャリアがドレイン領域34に導かれにくくする。

(もっと読む)

電気光学装置、電気光学装置の駆動方法および電子機器

【課題】表示に寄与する画素とダミー画素との境界での表示上の不具合を抑える。

【解決手段】マトリクス状に配列する表示画素110aに対して、ダミー画素110bは、平面視で表示画素110aを囲むように配列する。駆動回路は、表示画素110aの画素電極の各々に対して、フレームを単位として繰り返し供給された映像データであって、かつ、表示画素110aの各々にそれぞれ対応した映像データで指定された階調レベルに応じた電圧をそれぞれ印加する。一方、ダミー画素110bの画素電極の各々に対しては、隣り合う表示画素110aについて1フレーム前の映像データで指定された階調レベルに応じた電圧を印加する。

(もっと読む)

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

1 - 20 / 162

[ Back to top ]