Fターム[2H092JA24]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 種類 (8,621) | TFT (8,450)

Fターム[2H092JA24]の下位に属するFターム

スタガ構造(トップゲート構造) (1,511)

逆スタガ構造(ボトムゲート構造) (2,339)

Fターム[2H092JA24]に分類される特許

4,581 - 4,600 / 4,600

線パターン形成方法、デバイスとその製造方法及び電気光学装置並びに電子機器

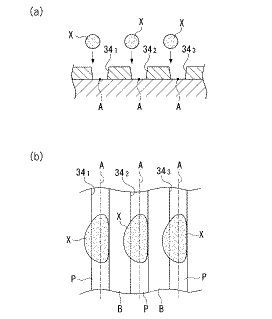

【課題】複数の線パターンの形成領域から一時的に溢れ出した機能液同士が接触しないように機能液を吐出することによって短絡を防止すると共に、線パターンと線パターンとをより近接させる。

【解決手段】線パターンの形成方法であって、隣合うバンク間34から一時的に溢れ出した上記機能液X同士が接触しないように各上記バンク間34の幅方向の中央Aに対し当該幅方向に変位した位置を各々のバンク間34の吐出位置として上記機能液Xを吐出することによって複数の上記バンク間34に同時に機能液を配置する。

(もっと読む)

液晶表示装置

【課題】機械的衝撃に伴って生じる表示ムラを軽減して表示品位を向上させる。

【解決手段】カラーフィルタ124上に配置される画素電極151およびカラーフィルタ124に形成されるコンタクトホール126を介して画素電極151に接続される画素TFT151を含むアレイ基板101と、画素電極151に対向する対向電極153を含む対向基板102と、これら基板101,102間に挟持される液晶層190とを備える。画素電極151は、カラーフィルタ124上でスリットを介して互いに隣接する複数のサブピクセル電極部、およびスリットの一部を横断して複数のサブピクセル電極部を接続するブリッジ配線部3を含み、コンタクトホール126はブリッジ配線部3を収容してブリッジ配線部3を複数のサブピクセル電極部よりも低い位置に設定するよう配置される。

(もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

液晶表示装置及びその駆動回路

【課題】ガラス基板上の配線を単層構造にして、製造工程を簡略化することができる駆動回路及び液晶表示装置を提供すること。

【解決手段】本発明にかかる液晶表示装置は対向電極13を備えたCF基板及びTFTアレイ基板38を備えている。TFTアレイ基板38は直交するゲート配線18及びソース配線20と、対向電極38に接続されたトランスファー電極14を備えている。またVCOM電圧及びVEEG電圧を生成するDC/DC部6と、VEEG電圧をゲート配線18に供給するゲートドライバIC2と、VEEG電圧を入出力するLCD用入出力端子41、39を備えている。そしてゲートドライバIC2上にVCOM電圧を入出力するドライバIC用ダミー入出力端子42、44を備え、これらがダミースルー配線15により接続されている。

(もっと読む)

配線構造

【課題】 高い周波数が印加され、数cm〜数10cmの長さを有する配線の抵抗を低減し、伝送される信号波形のなまりを低減する。

【解決手段】 高周波が印加される配線111は、層間絶縁膜107を介して、配線111の線方向にそって複数設けられたコンタクトホールにより配線106と電気的に並列接続している配線構造を採用する。その配線構造を周辺回路一体型アクティブマトリクス型液晶表示装置の周辺回路に用いることで、高周波信号が印加される配線において信号波形のなまりを低減できる。

(もっと読む)

液晶表示装置

【課題】 液晶表示装置に関し、簡単な構成により中間調における応答速度を含む全階調における応答速度を改善するとともに、視野角特性を改善する。

【解決手段】 一対の電極の内の少なくとも一方の電極はストライプ形状を有するとともに、前記一対の基板1,2の内の少なくとも一方の基板2(1)上に、前記ストライプ形状の走査方向とは異なる方向に走査する構造物5(6)を有し、電圧無印加時に液晶分子10は少なくとも一方の基板1面において略垂直配向であり、且つ、前記ストライプ状電極3の走査方向とは異なる方位角方向にプレチルト角を有するように構成する。

(もっと読む)

液晶表示装置の製造方法

【課題】 画素電極近傍の光り抜けを防止できるアクティブマトリックス型液晶表示装置の製造方法を提供すること。

【解決手段】 アレイ基板に対して略平行な電界を発生させることにより、液晶分子の配列を変化させる、アクティブマトリックス型液晶表示装置において、アレイ基板10上に、配線を形成した後透明な絶縁膜20を成膜する工程と、該配線側面に、該配線の膜厚に対する比が0.5以上1.0以下の膜厚の前記絶縁膜を残すように、該絶縁膜をドライエッチングする工程と、前記配線の膜厚に対する比が0.2以下の膜厚の前記配線のみ、ウェットエッチングする工程とを含むようにした。

(もっと読む)

液晶表示装置の製造方法

【課題】 少ない回数のフォトリソグラフィで横電界型液晶表示装置のアクティブマトリクス基板を製造する方法を提供する。

【解決手段】 横電界型液晶表示装置の製造方法において、逆スタガ型薄膜トランジスタのゲート電極および共通電極を形成する工程と、ゲート絶縁膜と半導体層とソース・ドレイン電極と画素電極とを形成する工程と、ゲート絶縁膜と薄膜トランジスタ上に形成したパッシベーション膜に所定の開口を形成する工程とから成り、開口形成後、共通配線結束線と各ドレイン配線と高抵抗を介して接続する連結線とを各線の端部に形成した前記開口を介して導電ぺーストで接続するようにした。

(もっと読む)

液晶表示装置

【課題】 共通電極配線の低抵抗化を図る。

【解決手段】 一対の基板と、前記一対の基板のうちの一方の基板上の表示領域に形成される複数のアクティブ素子と、前記一方の基板上に行方向に形成され行方向のそれぞれのアクティブ素子に走査信号を印加する複数の走査信号線と、前記一方の基板上に列方向に配列されたドレイン信号線を介して映像信号が印加される画素電極と、前記一方の基板上に行方向に配列されている共通電極信号線とを有する液晶表示装置において、前記各共通電極信号線は、その両端部が共通電極配線によって接続されると共に、前記共通電極信号線の一端に接続された共通電極配線と他端に接続された共通電極配線で配線層数が異なる。

(もっと読む)

液晶表示装置

【課題】 光効率の向上を図る。

【解決手段】 液晶を介して対向配置される各基板SUBの一方の基板の液晶側の画素領域に、画素電極PXとこの画素電極との間に電界を生じせしめる対向電極CTを備え、前記画素電極および対向電極はそれぞれ一方向に延在し該方向に交差する方向に交互に配置される帯状の複数の電極からなり、これら各電極のうち他の電極よりも幅広に設定される電極を備え、この幅広に設定された前記電極とそれに隣接する電極の離間幅は、他の隣接する電極の離間幅よりも大きく設定されている。

(もっと読む)

電気光学装置及び電子機器

【課題】 液晶装置等の電気光学装置において、耐光性を高め、高品位の画像を表示する。

【解決手段】 電気光学装置は、TFTアレイ基板(10)上に、画素電極(9a)と、これに接続されたTFT(30)と、これに接続された配線(3a、6a)と、TFTの少なくともチャネル領域を上側から覆う上側遮光層(300、6a)と、このTFTの少なくともチャネル領域を下側から覆う下側遮光層(11a)とを備える。基板には、配線に対向する領域に格子状やストライプ状の溝(10cv)が掘られており、この溝内でチャネル領域に対向する領域に凹部(401)が更に掘られている。下側遮光膜は、該凹部内に形成されている。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

液晶装置、投射型表示装置及び電子機器

【課題】 画素と画素の間隔が狭くなる高精細な液晶表示装置に対してディスクリネーションに起因する表示欠陥を生じないようにし、高コントラストでかつ明るい表示を可能とした液晶装置及び投射型表示装置と電子機器の提供を目的とする。

【解決手段】 第1基板と第2基板に挟持された液晶層と、前記第2基板の前記液晶層側の面に形成された第1電極、第2電極を備え、前記第1電極と前記第2電極は前記液晶層に対し実質的に基板面と平行な電界が印加できるように構成された液晶装置において、液晶分子の配列の変化する方向が異なる複数の領域を前記第1電極、第2電極とで形成される画素領域内に有することを特徴とする液晶装置。

(もっと読む)

液晶表示パネル

【課題】本発明は、液晶の配向分割制御をMVA方式により行う液晶表示パネルに関し、連結不良を生じている画素を救済して、製造歩留まりを向上させることができる液晶表示パネルを提供することを目的とする。

【解決手段】画素領域毎に形成されて所定のバスライン1,2に接続される薄膜トランジスタ3aと、スリット5a、5b、5cにより3つの分割電極領域a、b、c、dに分割された画素電極4aと、隣り合う分割電極領域a〜d間を電気的に接続する接続電極6a〜6cと、薄膜トランジスタ3aと画素電極4aとを電気的に接続する接続部(コンタクトホール)7aとを有している。接続部7aは、2つの分割電極領域a、cと接続電極6a、6bを介して接続する分割電極領域bに設けられている。

(もっと読む)

液晶表示装置

【課題】表示領域最外周画素部に設けられた画素電極のパターニング不良を無くし、表示品位の向上した液晶表示装置を提供することにある。

【解決手段】表示領域の最外周に沿って位置した画素部の着色層25Bを黒着色層からなる額縁パターン32側へ延在させて延在部27を形成することにより、着色層と額縁パターンとの段差部分を画素電極30から離して配置する。また、着色層の延出部の下方に、液晶表示素子を構成する金属配線を配置して、画素電極と額縁パターンとの間の領域を遮光する。

(もっと読む)

多結晶シリコン薄膜の平坦化方法

【課題】 多結晶シリコン薄膜の表面に形成された突起を容易且つ確実に除去することができる多結晶シリコン薄膜の平坦化方法を提供することを目的とする。

【解決手段】 多結晶シリコン薄膜を炭素(C)とフッ素(F)と水素(H)とを少なくとも含有するガスのプラズマに曝すことにより突起を除去して多結晶シリコン薄膜の表面を容易且つ確実に平坦化することができる。

(もっと読む)

半導体装置、画像表示装置、半導体装置の製造方法、及び画像表示装置の製造方法

【課題】 CMOS−TFTを構成するp型及びn型TFTの各しきい値電圧を独立に効率良く(最小限のフォトリソグラフィーで)高精度に制御する。

【解決手段】 CMOS−TFTを製造するに際して、しきい値電圧(Vthp ,Vthn )制御として極低濃度にp型不純物(B:ボロン)の非選択的添加(p型及びn型TFTの双方に添加)及び選択的添加(n型TFTのみに添加)を連続的に行なう。具体的には、当初図4(a)のようにId −Vg 特性がp型及びn型TFT共に負シフトした状態から、非選択的添加により図4(b)のようにp型及びn型TFT共に正シフトさせてVthp を先ず仕様値とし、続いて選択的添加によりn型TFTのみ正シフトさせてVthn を仕様値に調整する。

(もっと読む)

電気光学装置及びその製造方法並びに電子機器

【課題】 電気光学装置において、比較的簡単な構成を用いて、画素部のTFTのチャネル領域やチャネル隣接領域における入射光や戻り光に対する遮光性能を高める。

【解決手段】 電気光学装置は、一対の基板間に挟持された電気光学物質層(50)と、TFTアレイ基板(10)にマトリクス状に設けられた画素電極(9a)とを備える。TFT(30)の下側には、第1遮光膜(11a)が設けられている。データ線(6a)は、遮光性の材料からなり、TFTのチャネル領域(1a’)及びチャネル隣接領域(1a”)を対向基板(20)の側から見て夫々覆う主配線部と、この主配線部の縁から層間絶縁膜に形成された溝に向けて伸びておりチャネル隣接領域を側方から囲む側方遮光部(6b)とを有する。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

4,581 - 4,600 / 4,600

[ Back to top ]