Fターム[2H092KA08]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子、光導電体層の材料 (8,799) | 素子材料 (4,927) | 物質 (1,730) | 無機材料 (1,105) | 化合物 (540)

Fターム[2H092KA08]に分類される特許

101 - 120 / 540

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による脱水化または脱水素化処理を行った酸化物半導体膜を含み、且つ、作製工程において酸素ドープ処理されたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

非晶質酸化物、及び電界効果型トランジスタ

【課題】TFTの活性層等に適用できる新規な非晶質酸化物を提供する。

【解決手段】非晶質酸化物が微結晶を含む、又は層厚方向に組成が変化していること、又は所定の材料を含むことを特徴とする。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

有機薄膜トランジスタアレイ基板及びその製造方法

【課題】有機薄膜トランジスタアレイ及びその製造方法を提供する。

【解決手段】本製造方法は、ベース基板に、第1透明導電薄膜層とソース・ドレイン金属薄膜層を順次形成し、第1回パターニング工程を行って、第1画素電極パターン、ソース電極パターン、ドレイン電極パターン及びデータラインパターンを形成する工程と、有機半導体薄膜層とゲート絶縁薄膜層とを順次形成し、第2回パターニング工程を行って、前記ソース電極パターンとドレイン電極パターン上に位置する有機半導体アイランドパターン及びゲート絶縁アイランドパターンを形成する工程と、一層のパッシベーション層薄膜を形成し、第3回パターニング工程を行って、データラインパッド領域を形成する工程と、第2透明導電薄膜層とゲート金属薄膜層とを順次形成し、第4回パターニング工程を行って、第2画素電極パターン、ゲート電極パターン、及びゲートラインパターンを形成する工程とを備える。

(もっと読む)

アクティブマトリクス基板及びそれを備えた表示パネル

【課題】フォトマスクの枚数を増やすことなく、酸化物半導体の半導体層を用いたTFTの特性の低下を抑制することにある。

【解決手段】マトリクス状の複数の画素電極Pと、各画素電極Pに接続されたTFT5と、互いに平行に延びる複数のソース線15aとを備え、TFT5が、絶縁基板10上のゲート電極11aと、ゲート電極11aを覆うゲート絶縁膜12aと、ゲート絶縁膜12a上でゲート電極11aに重なる酸化物半導体層13aと、酸化物半導体層13aに接続されたソース電極17a及びドレイン電極17bとを備え、ソース電極17a及びドレイン電極17bと酸化物半導体層13aとの間には、酸化物半導体層13aを覆う保護絶縁膜14aが設けられ、各ソース線15aは、金属材料により形成され、ソース電極17a及びドレイン電極17bは、各画素電極Pと同一材料により形成されている。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

アレイ基板及びその製造方法

【課題】アレイ基板及びその製造方法を提供する。

【解決手段】本発明による製造方法は、基板に無機材料の突起を形成するステップと;それぞれ第一透明導電層と第一金属層からなる反射領域パターン、ゲートライン及びゲートラインから分岐して出されるゲート電極と共通電極を形成するステップと;半導体層からなる活性化ランドパターンと第二金属層からなるデータラインパターンを形成し、活性化ランドパターン上でデータラインに接続されるソース電極とドレイン電極、及び半導体層からなるチャネルを形成するステップと;基板に無機材料を塗布し、無機材料に対して焼き戻し工程を行って一平坦層を形成し、ドレイン電極にビアホールを形成するステップと;反射領域に、ビアホールを介してドレイン電極に接続され且つ第二透明導電層からなる画素電極を形成するステップと、を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第1の結晶性酸化物半導体膜ともいう)を形成し、該酸化物半導体膜に酸素を導入して少なくとも一部を非晶質化し酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜(第2の結晶性酸化物半導体膜ともいう)を形成する。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

薄膜トランジスタ構造、ならびにその構造を備えた薄膜トランジスタおよび表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、保護膜等の形成時に酸化処理層を必要とせずに、薄膜トランジスタの電気特性を安定させることが可能である酸化物半導体層を提供する。

【解決手段】基板上に少なくとも、基板側から順に、酸化物半導体層と、ソース・ドレイン電極と、保護膜とを備えた薄膜トランジスタ構造であって、前記酸化物半導体層は、金属元素全体に占めるZnの含有量が50原子%以上であり、ソース・ドレイン電極および保護膜側に形成される第1酸化物半導体層と、In、Ga、およびZnよりなる群から選択される少なくとも1種の元素と、Snとを含み、基板側に形成される第2酸化物半導体層との積層体であり、かつ、前記第1酸化物半導体層と、前記ソース・ドレイン電極および保護膜とが、直接接触していることを特徴とする薄膜トランジスタ構造。

(もっと読む)

酸化物材料および半導体装置

【課題】トランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、このような半導体装置を実現する酸化物材料を提供する。

【解決手段】それぞれ、c軸配向し、ab面、上面または被形成面に垂直な方向から見て少なくとも三角形状または六角形状の原子配列を有し、c軸においては、金属原子が層状または金属原子と酸素原子とが層状に配列しており、In2SnZn2O7(ZnO)m(mは0または自然数。)で表される、ab面(または上面または被形成面)においては、a軸またはb軸の向きが異なる二種以上の結晶部分を含む酸化物膜を用いる。

(もっと読む)

部材の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

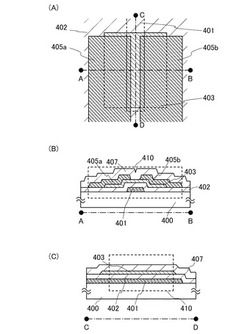

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かす

には、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上

においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層

103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層10

4aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170

aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導

体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可

能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

薄膜トランジスタ構造、ならびにその構造を備えた薄膜トランジスタおよび表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、保護膜等の形成時に酸化処理層を必要とせずに、薄膜トランジスタの電気特性を安定させることが可能である酸化物半導体層を提供する。

【解決手段】基板上に少なくとも、基板側から順に、酸化物半導体層と、ソース・ドレイン電極と、保護膜とを備えた薄膜トランジスタ構造であって、前記酸化物半導体層は、金属元素全体に占めるZnの含有量が50原子%以上であり、ソース・ドレイン電極および保護膜側に形成される第1酸化物半導体層と、In、Ga、およびZnよりなる群から選択される少なくとも1種の元素を含み、基板側に形成される第2酸化物半導体層との積層体であり、かつ、前記第1酸化物半導体層と、前記ソース・ドレイン電極および保護膜とが、直接接触していることを特徴とする薄膜トランジスタ構造。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

表示装置

【課題】簡便な構成及び動作によって表示装置の消費電力を低減すること。

【解決手段】表示装置が入力デバイスを備え、該入力デバイスから出力される画像操作信号に応じて、駆動回路に対する画像信号の入力を制御する。具体的には、入力デバイスが操作されない際の画像信号の入力頻度を、入力デバイスが操作される際の画像信号の入力頻度よりも低くする。これにより、当該表示装置が使用される際の表示の劣化(表示品質の低下)を抑制することが可能となり、且つ使用されない際の消費電力を低減することが可能になる。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

101 - 120 / 540

[ Back to top ]