Fターム[2H092MA08]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 成膜方法 (5,204) | CVD (1,864) | プラズマ (1,102)

Fターム[2H092MA08]に分類される特許

161 - 180 / 1,102

電気光学装置

【課題】電気光学装置の作製工程においてマスク枚数を追加することなく、反射電極の散

乱構造を作製する。

【解決手段】層間膜に感光性樹脂膜を用いる。フォトマスク100の第1の透光部101

を通して露光してパターニングしてコンタクトホール103〜106を得る。フォトマス

ク100の第2の透光部102を通して露光すると、感光性樹脂膜が解像不能となり、感

光性樹脂膜の表面に凹凸ができる。これにより一枚のフォトマスクでコンタクトホール形

成と層間膜表面に凹凸を有する散乱構造とができる。

(もっと読む)

アレイ基板、及び表示装置

【課題】 1枚の基板から得られる表示パネルの枚数が多くでき、放電破壊を抑制するショート配線としても機能する共通配線の構成のアレイ基板において、外部接続端子と共通配線とを接続する接続配線の、共通配線のコンタクトホールを有する接続部での腐食を抑制して信頼性の向上を図る。

【解決手段】 絶縁性基板1上に、複数の表示パネル50を構成する複数の表示領域40が配置され、走査配線2、信号配線6、及び共通配線80に接続される外部接続端子60を有するアレイ基板110において、外部接続端子60と隣接する表示パネル50の共通配線80とを接続する接続配線70は、隣接する表示パネル50の共通配線80に設けられたコンタクトホール64を有する接続部65において接続され、接続部65は対向基板120を貼り合わせるシール材95が形成される領域下、又はシール材95より表示領域40側である内側に配置される。

(もっと読む)

アレイ基板及び液晶表示装置

【課題】製造歩留まりの高いアレイ基板及び液晶表示装置を提供する。

【解決手段】アレイ基板は、複数の補助容量電極と、複数の半導体層15と、複数のゲート電極20を含んだ複数の走査線19と、複数の補助容量線と、複数のコンタクトホールを有した層間絶縁膜と、複数のコンタクトホールを通って複数の半導体層のソース領域に電気的に接続された複数の信号線と、複数の画素電極と、を備えている。走査線19が延在した方向に互いに隣合う一方の画素電極が接続された補助容量電極と、他方の画素電極が接続された補助容量電極とは、走査線を挟んで位置している。薄膜トランジスタのチャネル面積CSは、24μm2以上である。

(もっと読む)

液晶表示装置、パーソナルコンピュータ、ディスプレイ、電子書籍

【課題】液晶滴下により、広視野角表示のマルチドメイン垂直配向型の液晶表示装置を実

現する。

【解決手段】第1の基板及び第2の基板間に滴下された液晶を保持するためのシール材と

、シール材に囲まれ、第1の基板上に設けられた画素部と、シール材の外側において、第

2の基板とは重ならない領域の第1の基板上に配置されるICチップと、シール材の外側

において、第2の基板とは重ならない領域の第1の基板上に配置される、画素部とICチ

ップとを電気的に接続する異方性導電膜と、シール材と交差するように画素部から異方性

導電膜が配置される領域まで延び、第1の基板上に設けられた画素部とICチップとを電

気的に接続する配線とを有する液晶表示装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

液晶表示装置

【課題】本発明は、液晶表示装置の製造工程のうちの表示板に集積されたゲート駆動部に静電気が流入することを防止する液晶表示装置を提供する。

【解決手段】本発明の液晶表示装置は、基板、基板上に形成された複数のスイッチング素子を各々含む複数の画素、スイッチング素子に接続され、行方向に延びている複数のゲート線、ゲート線と各々接続されている回路部及び回路部と接続されている配線部を含むゲート駆動部を含み、回路部はトランジスタを含み、配線部は信号線を含み、トランジスタと信号線は接続部材を介して接続されていることを特徴とする。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

導電性素子およびその製造方法、配線素子、情報入力装置、表示装置、ならびに電子機器

【課題】精細かつ高スループットの導電性素子を提供する。

【解決手段】導電性素子は、第1の波面と第2の波面とを有する基体と、第1の波面上に形成された、2層以上の層が積層された積層膜とを備える。積層膜が、導電パターン部を形成する。第1の波面および第2の波面が、0≦(Am1/λm1)<(Am2/λm2)≦1.8(但し、Am1:第1の波面の振動の平均幅、Am2:第2の波面の振動の平均幅、λm1:第1の波面の平均波長、λm2:第2の波面の平均波長)の関係を満たす。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく

作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体層とする薄膜トランジスタ

を有する半導体装置の作製方法において、酸化物半導体層に接する酸化物絶縁膜を形成す

る。酸化物半導体層を減圧されたチャンバー内に導入後、窒素雰囲気下で加熱処理工程、

プラズマ(少なくとも酸素プラズマを含む)の導入工程を行い、成膜ガスを導入して酸化

物絶縁膜を形成する。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

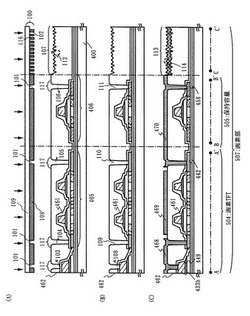

薄膜トランジスタアレイ基板及びその製造方法、並びに液晶表示装置

【課題】画素電極と共通電極とが絶縁膜を介して対向した構造を有し、画素の一部に電気的欠陥が生じた場合にも良品化することが可能なTFTアレイ基板を提供する。

【解決手段】TFTアレイ基板101は、薄膜トランジスタ10と、ドレイン電極16に導電接続された画素電極20と、画素電極40と絶縁膜30を介して対向形成された共通電極40とを含む画素が複数マトリクス状に形成されたものである。TFTアレイ基板101は、1個の画素に着目したとき、画素電極20が複数の分割画素電極20Dに分割されており、かつ、ドレイン電極16と複数の分割画素電極20Dとをそれぞれ導電接続する複数の分岐導電部16Bを有し、平面視上、複数の分岐導電部16Bの少なくとも一部の形成領域に、共通電極40が形成されていない。

(もっと読む)

半導体装置の製造方法

【課題】フォトダイオードの出力特性のばらつきを抑制しつつ、検出精度の低下が防がれた高性能なフォトダイオードを形成することができる半導体装置の製造方法を提供する。

【解決手段】所定のゲート金属を用いて、フォトダイオード用の第1の半導体層30aのうち、真性半導体領域となる部分を覆うシールド部34aをゲート絶縁膜29上に形成するとともに、薄膜トランジスタ用の第2〜第5の各半導体層30b〜30eのうち、チャネル領域となる部分を覆う第1〜第4のゲート電極34b〜34eをゲート絶縁膜29上に形成する。その後、シールド部34aをマスクとして用いて、第1の半導体層30aにn型領域及びp型領域を形成した後、当該シールド部34aを除去する。

(もっと読む)

液晶表示装置

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

反射型液晶表示装置及び液晶プロジェクターシステム

【課題】 遮光だけでは抑制できない、入射してしまう光により生じる電子(ホール)による影響を抑制する。

【解決手段】 トランジスタのドレイン領域34よりも、多数キャリアに対して、ドレイン領域における電圧とQ(単位電荷量)との積の基準値よりも低いポテンシャルとされる領域36を設けるか、もしくはドレイン領域の周りにポテンシャル障壁を設ける。かかる構成により、フローティングとなる反射電極30と接続されたドレイン領域34の回りのポテンシャル制御を行い、半導体基板内に発生した光キャリアがドレイン領域34に導かれにくくする。

(もっと読む)

薄膜トランジスタ液晶ディスプレーのアレイ基板およびその製造方法

【課題】薄膜トランジスタ液晶ディスプレーのアレイ基板及びその製造方法を提供する。

【解決手段】アレイ基板は画素領域を画成するゲートラインとデータラインとを備え、前記画素領域内に薄膜トランジスタ、共通電極および電極ストリップ構造の画素電極とが形成され、前記共通電極は前記データラインを覆う第2絶縁層上に形成され、前記画素電極は前記共通電極を覆う第3絶縁層上に形成される。これによって、表示領域の面積が拡大され、開口率が効果的に向上される。

(もっと読む)

成膜方法

【課題】窒化シリコン膜と酸化シリコン膜との積層構造体を単一のプラズマCVD装置にて一貫して成膜する際に、両膜間に異質な薄膜が形成されないという機能を有しつつ、短時間で効率のよい成膜が可能な成膜方法を提供する。

【解決手段】本発明の成膜方法は、反応室2aに処理すべき基板Wを設置し、真空雰囲気中にてシリコンを含む原料ガスと窒素を含む一の反応ガスとを反応室内に導入し、放電用の高周波電力を投入してプラズマCVD法にて窒化シリコン膜を成膜する第1工程と、前記原料ガスを供給しながらプラズマ放電を維持した状態で、反応室内の窒素分圧を高める第2工程と、一の反応ガスの供給のみを停止し、酸素を含む他の反応ガスを反応室内に供給してプラズマCVD法にて酸化シリコン膜を成膜する第3工程とを含む。

(もっと読む)

液晶表示装置及び電子機器

【課題】液晶素子に印加される電圧を異ならせて視野角特性を改善する。

【解決手段】 本発明の一は、一画素に三以上の液晶素子を有し、該液晶素子の各々に印

加される電圧値が異なる液晶表示装置である。各液晶素子に印加される電圧を異ならせる

には、加えた電圧を分圧する素子を配置することにより行う。印加される電圧を異ならせ

るためには、容量素子、抵抗素子、又はトランジスタ等を用いる。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

薄膜トランジスタ液晶ディスプレイのアレイ基板及びその製造方法

【課題】本発明はTFT−LCDアレイ基板及びその製造方法に関する。

【解決手段】本発明はTFT−LCDアレイ基板及びその製造方法に関し、アレイ基板はベース基板と、ベース基板上に形成され画素領域を限定するゲートライン及びデータラインを含み、前記画素領域内には画素電極、薄膜トランジスタと共通電極が形成される。また、導電性薄膜材料により製造されるブラックマトリクスを含み、前記ブラックマトリクスは前記共通電極と接続される。

(もっと読む)

161 - 180 / 1,102

[ Back to top ]