Fターム[2H092NA22]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | 素子性能の向上 (1,705) | ON/OFF比の向上 (571)

Fターム[2H092NA22]に分類される特許

81 - 100 / 571

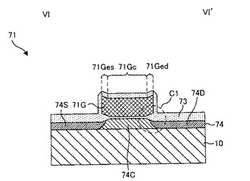

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、サンプリング用トランジスターの高速化とプッシュダウン現象の抑制を両立させ、高品位な表示を行う。

【解決手段】電気光学装置は、データ線(6)に画像信号線(60)から供給される画像信号をサンプリングするサンプリング用トランジスター(71)を備える。サンプリング用トランジスターのゲート絶縁膜(73)は、ゲート電極(71G)の第1ソースドレイン領域(74S)側の縁部(71Ges)に重なる部分及びゲート電極の第2ソースドレイン領域(74D)側の縁部(71Ged)に重なる部分の各々の膜厚が、ゲート電極の中央部(71Gc)に重なる部分の膜厚よりも厚くなるように形成されている。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】Gaを含まないIn−Zn−Oの酸化物半導体を備えた薄膜トランジスタのスイッチング特性およびストレス耐性が良好であり、特に正バイアスストレス印加前後のしきい値電圧変化量が小さく安定性に優れた薄膜トランジスタ半導体層用酸化物を提供する。

【解決手段】Inと;Znと;Al、Si、Ta、Ti、La、Mg、およびNbよりなる群から選択される少なくとも一種の元素(X群元素)と、を含む薄膜トランジスタの半導体層用酸化物である。

(もっと読む)

液晶表示装置

【課題】視野角特性に優れ、表示品位の良好な横電界方式の液晶表示装置を提供する。

【解決手段】第1基板ARと、第2基板CTと、第1基板ARと第2基板CTとの間に保持された液晶層LQと、マトリクス状に配置された画素からなる表示エリアとを備え、第1基板ARは、各画素に配置されたトップゲート型のスイッチング素子と、スイッチング素子を覆う第1絶縁膜25と、第1絶縁膜25の上において複数の前記画素にわたって配置された第1電極E1と、第1電極E1を覆う第2絶縁膜26と、第2絶縁膜26の上において各画素に配置され、スイッチング素子に接続され、第1電極E1と対向するスリットが形成された第2電極E2とを備えた液晶表示装置。

(もっと読む)

表示素子の製造方法

【課題】安定した電流駆動能力を発揮させる。

【解決手段】アレイ基板20の製造方法は、基板上にゲート電極24aを形成するゲート電極形成工程と、ゲート電極24a上に不純物を含有するゲート絶縁膜24b、半導体膜SM、導電膜COの順で成膜する成膜工程と、導電膜CO上にレジストRSを塗布し、そのレジストRSに対してフォトマスクを介して露光を行った後に現像を行うことでレジストRSをパターニングするレジストパターニング工程と、パターニングされたレジストRSをマスクとして導電膜COをエッチングすることで開口領域OPを挟んで配されるソース電極24d及びドレイン電極24eを形成する導電膜パターニング工程と、開口領域OPから半導体膜SMを介してゲート絶縁膜24bに含有される不純物を脱離させる不純物脱離工程とを含む。

(もっと読む)

薄膜トランジスタアレイパネル

【課題】薄膜トランジスタアレイパネルにおいて、酸化シリコン膜の厚さを減少させる。

【解決手段】本発明の実施形態に係る薄膜トランジスタアレイパネルは、絶縁基板と、絶縁基板上に配置され、ゲート電極を含むゲート線と、ゲート線上に配置され、窒化シリコンを含む第1ゲート絶縁膜と、第1ゲート絶縁膜上に配置され、酸化シリコンを含む第2ゲート絶縁膜と、第2ゲート絶縁膜上に配置される酸化物半導体と、酸化物半導体上に配置され、ソース電極を含むデータ線と、酸化物半導体上に配置され、ソース電極と対向するドレイン電極と、ドレイン電極と接続される画素電極と、を含み、第2ゲート絶縁膜の厚さは200Å以上500Å未満であることを特徴とする。

(もっと読む)

電気光学装置及び電子機器

【課題】 画素選択トランジスタにて光リークが生じたとしても、電気光学素子の階調が劣化しない画素回路、それを用いた電気光学装置及びその駆動方法並びに電子機器を提供すること。

【解決手段】 電気光学装置の画素回路10は、一端にデータ線DLが接続され、かつ走査線WLによってオン/オフが制御される画素選択トランジスタ12と、画素選択トランジスタ12を経由して書き込まれる表示電圧に基づいて光透過率が変化する電気光学素子40と、画素選択トランジスタ12と電気光学素子40との間に設けられたメカニカルスイッチ20と、を有する。メカニカルスイッチ20は、画素選択トランジスタ12と電気光学素子40との間の導通経路上の固定接点26と、固定接点26に対して接離される可動接点24とを備える。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果による電気特性の変動が生じにくい、チャネル領域に酸化物半導体を含むトランジスタを用いた半導体装置を作製する。

【解決手段】窒素を含む一対の酸窒化物半導体領域、および該一対の酸窒化物半導体領域に挟まれる酸化物半導体領域を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体領域上に設けられるゲート電極とを有する半導体装置。ここで、一対の酸窒化物半導体領域はトランジスタのソース領域およびドレイン領域となり、酸化物半導体領域はトランジスタのチャネル領域となる。

(もっと読む)

半導体装置、半導体装置の製造方法、電気装置

【課題】半導体装置、半導体装置の製造方法、電気装置を提供する。

【解決手段】本発明の半導体装置は、一面に、ソース電極41cおよびドレイン電極41dを有する第1基板34と、一面に、ゲート電極41e、ゲート絶縁膜41bおよび半導体層41aを有する第2基板39と、第1基板34および第2基板39が互いの一面側を対向させて貼り合わされることによりこれら第1基板34と第2基板39との間に構成される薄膜トランジスタTRと、を備えている。

(もっと読む)

薄膜トランジスタ形成用基板、半導体装置、電気装置

【課題】多層基板内にTFT素子の構成要素のうちの少なくとも1つを内蔵させることによって薄膜トランジスタの高精細化を実現できる薄膜トランジスタ形成用基板、半導体装置、電気装置を提供する。

【解決手段】本発明の第1基板30(素子基板300)は、表面に制御トランジスタの構成要素の少なくとも一部を備え、内部には制御トランジスタの構成要素に接続される走査線66、データ線68、保持容量線、保持容量が埋め込まれていることを特徴とする。

(もっと読む)

半導体装置及び表示装置

【課題】高融点メタルバリア層を有していなくても、高温熱処理後の電気特性を良好にする技術を提供することを目的とする。

【解決手段】半導体装置は、透明絶縁性基板1上に形成されたゲート電極2と、ゲート電極2上にゲート絶縁膜6を介して順次に形成されたSi半導体能動膜7と、n型の導電型を有するオーミック低抵抗Si膜8とを含む半導体層51と、半導体層51と直接接合された、少なくともアルミニウム(Al)を含むソース・ドレイン電極9,10とを備える。半導体層51は、平面視においてゲート電極2の外周よりも内側に形成され、Si半導体能動膜7の側面とソース・ドレイン電極9,10との界面近傍である第1領域には、少なくとも窒素(N)が含まれる。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

酸化物半導体薄膜トランジスタ及びその製造方法

【課題】高電圧に対する高い耐久性と信頼性を有する酸化物半導体薄膜トランジスタを提供することが可能な、新規かつ改良された酸化物半導体薄膜トランジスタ及びその製造方法を提供する。

【解決手段】酸化物半導体薄膜トランジスタは、基板の上部に形成されて第1面積を有するゲート電極、ゲート電極をカバーするためにゲート電極の上部に形成されるゲート絶縁膜、ゲート絶縁膜の上部に形成されて第1面積より狭い第2面積を有する活性層、活性層のソース領域にコンタクトし、活性層の上部に形成されるソース電極、活性層のドレーン領域にコンタクトし、活性層の上部に形成されるドレーン電極及び活性層、ソース電極及びドレーン電極をカバーする保護膜を含む。従って、酸化物半導体薄膜トランジスタは高電圧に対する高耐久性及び信頼性を有することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】従来では、LDD構造を備えたTFTやGOLD構造を備えたTFTを形成しようとすると、その製造工程が複雑なものとなり工程数が増加してしまう問題があった。

【解決手段】第2のドーピング工程によって低濃度不純物領域24、25を形成した後、第4のエッチング工程を行うことによって、第3の電極18cに重なる低濃度不純物領域の幅と、第3の電極に重ならない低濃度不純物領域の幅とを自由に調節できる。こうして、第3の電極18cと重なっている領域は、電界集中の緩和が達成されてホットキャリアによる防止ができるとともに、第3の電極18cと重なっていない領域は、オフ電流値を抑えることができる。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】入射光が確実に遮光され安定した動作が得られるトランジスターを備えた電気光学装置、電気光学装置の製造方法、この電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置は、ソース領域30sと、ドレイン領域30dと、チャネル領域30cと、チャネル領域30cとドレイン領域30dの間に形成された接合領域30fとを有する半導体層30aと、半導体層30aを覆う第1絶縁膜を介してチャネル領域30cに対向するゲート電極部30gと、平面的に接合領域30fに沿って第1絶縁膜および第2絶縁膜に設けられた溝としてのコンタクトホールCNT5,CNT6と、コンタクトホールCNT5,CNT6内に、ゲート電極部30gから延在して設けられる第1導電膜と、データ線6aを構成する第2導電膜とを含む少なくとも2層の導電膜を有する遮光性の側壁部と、を備えた。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

アレイ基板及び液晶ディスプレイ

【課題】本発明はアレイ基板及び液晶ディスプレイに関する。

【解決手段】本発明は、アレイ基板と液晶ディスプレイを開示している。このアレイ基板は、サブストレートと、前記サブストレートに形成された、横縦方向に交差して複数の画素ユニットを囲んで形成したデータライン及びゲートラインと、を備え、各画素ユニットは画素電極と薄膜トランジスタースイッチ素子とを備え、前記薄膜トランジスタースイッチ素子は、ゲート電極、ソース電極、ドレイン電極、活性層を備え、前記ゲート電極と活性層との間にゲート絶縁層が設けられ、前記ゲート絶縁層は不透明絶縁層を含む。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバICの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジスタを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給する。

(もっと読む)

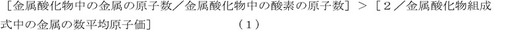

金属酸化物半導体薄膜

【課題】移動度が高く電気的特性に優れ、印刷法でも製造可能な金属酸化物半導体薄膜を提供する。更に、本発明は、該金属酸化物半導体薄膜の製造方法及び該金属酸化物半導体薄膜を用いた薄膜トランジスタを提供する。

【解決手段】金属酸化物を含有する金属酸化物半導体薄膜であって、前記金属酸化物は、下記式(1)に規定する関係を満たすことを特徴とする金属酸化物半導体薄膜。

[数1] (もっと読む)

(もっと読む)

トランジスタの作製方法

【課題】特性のバラツキが少なく、電気特性が良好なトランジスタを作製する。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体を含む半導体層を形成し、半導体層上に不純物半導体層を形成し、不純物半導体層上にマスクを形成した後、マスクを用いて半導体層及び不純物半導体層をエッチングして、半導体積層体を形成し、マスクを除去した後に半導体積層体を希ガスを含む雰囲気で発生させたプラズマに曝して半導体積層体の側面に障壁領域を形成し、半導体積層体の不純物半導体層に接する配線を形成する。

(もっと読む)

81 - 100 / 571

[ Back to top ]