Fターム[2H093NC26]の内容

Fターム[2H093NC26]に分類される特許

1 - 20 / 677

液晶表示装置および電子機器

【課題】COM分割駆動を行う際に、共通電極が異常な電位となるのを回避することができる液晶表示装置及び電子機器を提供する。

【解決手段】画素を構成する共通電極108が複数に分割されており、複数の共通電極108にそれぞれ対応して設けられた単位制御回路Pを有する共通電極駆動回路(制御回路)40を備える。単位制御回路Pは、ラッチ回路Qと選択回路Rとを含んで構成され、選択回路Rは、極性信号POLに応じて電圧VCOML又は電圧VCOMHを共通電極108に供給する電圧供給状態と、共通電極108を電気的に切り離したHi−Z状態(ハイ・インピーダンス状態)とする電圧遮断状態とを切り替え可能に構成する。

(もっと読む)

電気光学装置の駆動回路、電気光学装置、及び電子機器

【課題】安価に高い表示品位を実現することができる電気光学装置の駆動回路及び電気光学装置、並びに当該回路又は装置を備える電子機器を提供する。

【解決手段】電気光学装置1は、複数行の走査線Y1〜Ynを所定の順番で選択して走査信号を印加する走査線主駆動回路40と、走査線Y1〜Ynの各々に設けられて走査線主駆動回路40によって走査線Y1〜Ynのうちの一の走査線が選択される前後に選択される他の走査線に印加される走査信号によって動作し、走査線主駆動回路40によって一の走査線が選択されて走査信号が印加される期間に、走査信号を整形するための補助信号を一の走査線に印加する走査線補助駆動回路50とを備える。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】低電圧動作が可能でありながら、中間電源電圧の供給の有無に関わらず動作可能である表示パネルドライバを提供する。

【解決手段】データ線ドライバ3が、出力アンプ回路14と出力端子16A、16Bとを具備する。出力アンプ回路14は、電源電圧VDDと電圧VMLとの供給を受けて、正の駆動電圧を出力する正専用出力段24Aと、電源電圧と接地電圧の間の駆動電圧を出力可能な正負共用出力段28とを備えている。正専用出力段24Aのプルダウン出力トランジスタは、ディプレッション型であり、正負共用出力段28のプルダウン出力トランジスタは、エンハンスメント型である。電圧VMLがVDD/2に設定されたときは、正専用出力段24Aが正の駆動電圧を出力端子16A又は16Bに出力する。電圧VMLが接地電圧VSSに設定されたときは、正負共用出力段28が正の駆動電圧を出力端子16A又は16Bに出力する。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】階調電圧の下限電圧をグランド電圧にできる集積回路装置、電気光学装置及び電子機器等を提供すること。

【解決手段】集積回路装置は、階調電圧生成回路160と、ドライバー回路100−1〜100−kと、を含み、階調電圧生成回路160は、高電圧側電源電圧VDDRWとグランド電圧VSSとの間を電圧分割して階調電圧VG1〜VGiを生成し、ドライバー回路100−1〜100−kは、第1のキャパシターCI1〜CIkと第2のキャパシターCF1〜CFkとを有するデータ線駆動回路140−1〜140−kを有し、データ線駆動回路140−1〜140−kは、第1のキャパシターCI1〜CIkと第2のキャパシターCF1〜CFkとの容量比に応じた増幅率の反転増幅を行って、下限電圧がグランド電圧VSSより高くなる出力範囲のデータ電圧V1〜Vkを出力する。

(もっと読む)

表示装置および駆動装置

【課題】画像信号線駆動回路の消費電力を削減可能な表示装置等を提供する。

【解決手段】液晶表示装置は複数の画像信号線駆動回路を含んでいる。複数の画像信号線駆動回路のそれぞれは、タイミングコントローラ310と、画像データ抽出回路350と、画像データ抽出回路350によって抽出された画像データをラッチするデータラッチ回路360とを含んでいる。画像データ抽出回路350は、画像データRGBdataのうちから、その画像信号線駆動回路に対して予め割り当てられた所定数の画像信号線に対応する部分のデータを抽出する。画像データ抽出回路350は、画像データの抽出期間以外の期間では、一定電位の信号をデータラッチ回路360へ供給する。

(もっと読む)

液晶表示装置

【課題】製品の小型化を図ることができ、製品コストを抑制することができ、低消費電力化を図ることができる液晶表示装置を提供する。

【解決手段】液晶表示装置は、複数の信号線並びに複数の画素を有したアレイ基板と、対向基板と、液晶層と、を具備した液晶表示パネルと、それぞれN本の信号線に接続され、入力される映像信号をN本の信号線の何れかに選択的に与える複数の切替え素子群を含んだ切替え回路と、複数の切替え素子群に接続され、それぞれ複数の切替え素子群に映像信号を与えるドライバ回路81と、ドライバ回路に接続され、ドライバ回路が複数の切替え素子群に映像信号を与えるタイミングを制御するコントロール回路82と、を備えている。ドライバ回路81及びコントロール回路82は、多結晶化された同一のシリコンチップ80に形成されている。

(もっと読む)

ガンマ回路及びそれを用いた表示用駆動回路

【課題】ガンマ回路31のプッシュプルアンプにおける貫通電流を抑止する。

【解決手段】ガンマ回路31において、プッシュプルアンプ10に代えて、互いに隣接した基準電位を入力し、入力した基準電位と同一の電位の出力電圧を出力するNトップ型レギュレータ40−4〜40−1と、Pトップ型レギュレータ50−3〜50−0とを設けた。その結果、階調電位の出力端子VH0〜VH63及びVL0〜VL63に接続される負荷が“L”になっても“H”になっても互いに隣接するNトップ型レギュレータ40とPトップ型レギュレータ50とは、相補的に動作してプッシュプルアンプ10と同等に動作することができる。更に、プッシュプルアンプ10で発生した貫通電流がほとんど発生しなくなりためガンマ回路31の消費電流を大幅に削減することができる。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】表示ムラを防止できる集積回路装置、電気光学装置及び電子機器等を提供すること。

【解決手段】集積回路装置は、データ線駆動回路100−iと、パターン出力回路130と、順番設定回路140と、を含み、マルチプレクスされたデータ信号がデマルチプレクスされることで得られた複数のデータ信号が1水平走査期間において画素P1i〜Ppiに供給され、パターン出力回路130が、1または複数のフレーム毎に、画素P1i〜Ppiの駆動順番のローテーションパターンであるローテーションパターンPT1〜PTMのいずれかを出力ローテーションパターンQPTとして出力し、順番設定回路140が、出力ローテーションパターンQPTに基づいて、画素P1i〜Ppiの駆動順番を設定する。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】表示ムラを防止できる集積回路装置、電気光学装置及び電子機器を提供すること。

【解決手段】集積回路装置は、データ線駆動回路200−iと、位置オフセット用レジスター230と、位置オフセット用加算回路210−iと、を含み、マルチプレクスされたデータ信号がデマルチプレクスされることで得られた複数のデータ信号が、1水平走査期間において第1〜第pの画素に供給され、位置オフセット用レジスター230が、位置オフセット用設定値OG1と、位置オフセット用設定値OGpとを少なくとも記憶し、位置オフセット用加算回路210−iが、画像データGD1iに対して、位置オフセット用設定値OG1に基づく位置オフセット補正値を加算する処理と、画像データGDpiに対して、位置オフセット用設定値OGpに基づく位置オフセット補正値を加算する処理とを少なくとも行う。

(もっと読む)

初期リセット信号生成回路

【課題】同一導電型のトランジスタのみを用いて構成可能な初期化信号の生成回路(初期リセット信号生成回路)を提供する。

【解決手段】シフトレジスタの初期化のための初期リセット信号IRSを生成する初期リセット信号生成回路110は、プルアップ回路11とプルダウン回路12とから成る。プルアップ回路11は、電源の投入に応じて初期リセット信号IRSを活性化させる。プルダウン回路12は、シフトレジスタの動作を開始させるためのスタート信号STの活性化に応じて初期リセット信号IRSを非活性化する。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】表示ムラを防止できる集積回路装置、電気光学装置及び電子機器を提供すること。

【解決手段】集積回路装置は、データ線駆動回路200−iと、マルチプレクスされたデータ信号がデマルチプレクスされた複数のデータ信号が1水平走査期間において第1〜第pの画素に供給されるときに、第1〜第pの画素の駆動順番に依存して生じる順番オフセットに対応する順番オフセット用設定値OJ1〜OJpを記憶する順番オフセット用レジスター270と、第1〜第pの画素の駆動順番を設定する順番設定回路250と、順番オフセット用加算回路260−iと、を含み、データ線駆動回路200−iが、第qの画素を第r番目に駆動するときに、順番オフセット用加算回路260−iが、画像データGDqiに対して、順番オフセット用設定値OJrに基づく順番オフセット用補正値を加算する処理を行う。

(もっと読む)

ドライバ及び表示装置

【課題】表示部に縦線の異常表示が現れることない上に、アンプ回路が同じタイミングで動作するときに発生するノイズを削減できること。

【解決手段】本発明のドライバ(30)は、制御信号に応じて出力階調電圧を表示部(10)に出力する複数のアンプ回路(36−1〜36−N)と、制御回路(40)と、遅延部(41、42、43)と、を具備している。制御回路(40)は、制御信号として第1制御信号(CTR1)を出力する。遅延部(41、42、43)は、第1制御信号(CTR1)を複数のアンプ回路のうちの半数のアンプ回路である第1アンプ回路群の各々に順番に出力し、第1制御信号(CTR1)を任意の遅延時間遅延させた第2制御信号(CTR2)を第1アンプ回路群以外の第2アンプ回路群の各々に順番に出力する。

(もっと読む)

表示装置および電子機器

【課題】黒輝度、白輝度の最適化、フリッカ発生の抑止、リップル抑制を可能とする表示装置および電子機器を提供する。

【解決手段】比較出力部125Bは、出力電位と比較回路との検出結果を保存するメモリを有し複数回の比較結果をメモリに格納可能に構成され、格納結果を参照し出力値が目標値付近であることを判定し、判定が行われると出力系回路を一部停止させて出力電位をある一定期間中、容量すなわち平滑化キャパシタC123に保持した電荷のみで駆動させ、ソースフォロワーの前段を停止させ、平滑化キャパシタC123だけで電位を保持させ、キャパシタC123に溜まった電荷でソースフォロワーを駆動させる。

(もっと読む)

表示装置の駆動回路

【課題】表示装置の高階調化に対応して、階調電圧回路と駆動部とを結ぶ配線数を十分に少なくすることが困難となっている。

【解決手段】互いに異なる複数の基準電圧を生成する階調電圧回路1、基準電圧のいずれかを第1選択電圧として選択するとともに、第1選択電圧とは異なる基準電圧のいずれかを第2選択電圧として選択する第1選択回路2、第1選択電圧に基づいて出力端から出力電圧を出力する増幅器5、第1選択電圧及び第2選択電圧に基づいて生成した調整電圧を用いて前記出力電圧の電位を調整する出力電圧調整回路50A、を備える。出力電圧調整回路50Aが、増幅器5から出力される出力電圧の電位を調整する。よって、階調電圧回路にて生成される基準電圧の数を減らすことができ、階調電圧回路1と第1選択回路2とを結ぶ配線数を減らせる。結果として、駆動回路のチップ面積を小さくできる。

(もっと読む)

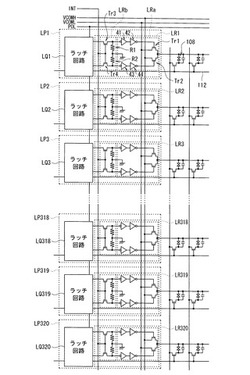

表示ドライバのデータ線駆動装置

【課題】様々な解像度の表示パネルに対応したマルチチャンネルシフトレジスタを用いた表示ドライバのデータ線駆動装置において、データ線を分割し、低消費電力化を図る。

【解決手段】データ線をDL1、DL2に分割し、第一のシフトレジスタ(S1〜S6)のシフトパルスによりデータ線DL1のデータをラッチする第一の表示ラッチ部(L1〜L6)と、第二のシフトレジスタ(S7〜S12)のシフトパルスによりデータ線DL2のデータをラッチする第二の表示ラッチ部(L7〜L12)と、第一のシフトレジスタのシフトしたシフトパルスを第二のシフトレジスタに伝える第三のシフトレジスタ21と、第一のシフトレジスタから第三のシフトレジスタへの接続と、第三のシフトレジスタから第二のシフトレジスタへの接続を切り替えるセレクタ回路を設け、第三のシフトレジスタを用いてデータ線の駆動開始と駆動停止を制御する。

(もっと読む)

表示装置及びドライバ

【課題】DAC遅延時間の影響を受けずに高速駆動を実現すること。

【解決手段】本発明の表示装置によれば、1出力にY個(Yは2以上の整数)のDAC13とY個のアンプ14とY個のスイッチ15とを備え、M個の保持部11、M個のスイッチ12をY個のグループに分けている。そこで、スイッチ15は、時分割タイミング(信号22)に同期することにより、アンプ14の出力の切り替えを行う。また、スイッチ15の切り替わりタイミングの周期をTとしたとき、DAC13が表示データ51を入力するタイミングは、時分割タイミングより位相をT/Y進めて、周期(Y×T)としている。即ち、DAC13が、Yクロック分の信号21により表示データ51を入力した場合、表示データ51に応じた階調電圧52は、信号21のYクロック目にアンプ14から出力される。これにより、DAC遅延時間の影響を受けずに高速駆動を実現することができる。

(もっと読む)

駆動回路、電気光学装置及び電子機器

【課題】パネル非駆動時に対向電極を確実にディスチャージさせる。

【解決手段】対向電極電位を供給する駆動回路は、外部電源電位VDD2に基づいて内部電源電位VLDO2を生成する内部電源電位生成回路と、出力線をディスチャージする第1ディスチャージ手段(Tr3、R)と、極性反転信号に基づいて電位VCOMH、VCOMLを交互出力するスイッチング回路320と、スリープモードへの移行当初のディスチャージ期間に、VCOM供給線303が基準電位VSSとなるように、ディスチャージする第2ディスチャージ手段(MV1、MV2)と、少なくともディスチャージ期間内からディスチャージ期間経過後に亘ってVCOM供給線の電位を保持する第1基準電位保持手段(HV1,HV2,R1)とを有し、第1ディスチャージ手段は、ディスチャージ期間に第2ディスチャージ手段によってディスチャージされるようにディスチャージ動作を遅らせる。

(もっと読む)

集積回路装置及び電子機器

【課題】 簡易な構造を有する異常検知可能な集積回路装置等を提供する。

【解決手段】 集積回路装置10は、異常を検出する少なくとも1つの検出回路36と、制御データを保持する複数の制御保持回路30と、を含む。前記少なくとも1つの検出回路36は、基準データを保持する基準保持回路37と、前記基準データと実質的に等しい等価データを保持する等価保持回路38と、前記基準データと前記等価データとを比較する比較回路39とを有する。前記少なくとも1つの検出回路36は、前記比較回路39の比較結果に基づき、前記基準データが異常であるか否かを表す検出信号を生成する。前記基準データが異常である場合、前記少なくとも1つの検出回路36は、前記検出信号として異常信号を出力する。前記基準保持回路37に保持される前記基準データは、前記比較回路39の比較動作のみに使用される。

(もっと読む)

表示パネルの駆動電圧出力回路

【課題】 動作速度の向上を図ることができる表示パネルの駆動電圧出力回路を提供する。

【解決手段】 ソースドライバの低圧側及び高圧側の電圧フォロワ各々は、差動入力段と、制御段と、出力段と、を備え、制御段は第1及び第2トランジスタの差動入力段の非反転入力の第1電位と反転入力の第2電位とが供給され、高圧側電源電位の供給端子と前記低圧側電源電位の供給端子との間にプッシュプル接続された互いに異なるチャンネルの第3及び第4トランジスタを有し、第3トランジスタの制御端に第1電位を供給し、第4トランジスタの制御端に第1電位と第2電位との差に応じた第3電位を供給して第3及び第4トランジスタの被制御端の接続点から制御電位を出力し、出力段は直列に接続された同一チャンネルの第5及び第6トランジスタからなり、第5トランジスタの制御端に第1電位を供給し、第6トランジスタの制御端に制御電位を供給し、第5及び第6トランジスタの被制御端の接続点が出力端子となる。

(もっと読む)

オペアンプ及び表示パネルの駆動装置

【課題】回路のレイアウト面積を小さくすることができるオペアンプ及び表示パネルの駆動装置を提供する。

【解決手段】ソースアンプ121は、差動回路300、カレントミラー回路210、出力回路212を含んで構成されている。差動回路300は、高耐圧のNMOSトランジスタN11A、N11Bがカレントミラー回路210と並列接続された差動対N11と、NMOSトランジスタN13と、を含んで構成されている。シンクアンプは、差動回路302、カレントミラー回路216、及び出力回路218を含んで構成されている。差動回路302は、高耐圧のPMOSトランジスタP12A、P12Bがカレントミラー回路216と並列接続された差動対P12と、PMOSトランジスタP15と、を含んで構成されている。

(もっと読む)

1 - 20 / 677

[ Back to top ]