Fターム[2H093ND42]の内容

Fターム[2H093ND42]に分類される特許

81 - 100 / 432

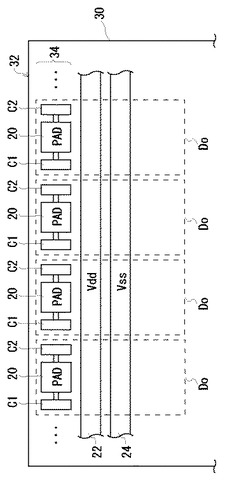

ソースドライバ回路

【課題】チップ面積を削減する。

【解決手段】複数のソースアンプDoは、複数のデータ線ごとに設けられ、画素の輝度を示す輝度データに応じた駆動電圧を生成し、対応するデータ線に供給する。各ソースアンプの出力端子20は、対応するデータ線と接続される。ハイサイドトランジスタは、電源ライン22と出力端子20との間に設けられ、ローサイドトランジスタは、接地ライン24と出力端子20との間に設けられる。第1キャパシタC1は、出力端子20とハイサイドトランジスタのゲートの間に設けられ、第2キャパシタC2は、出力端子20とローサイドトランジスタのゲートの間に設けられる。各ソースアンプDoの出力端子20として機能する各パッドPADを、ソースドライバが集積化される半導体基板30の一辺32に沿って配置する。第1キャパシタC1および第2キャパシタC2を、一辺32に沿って、パッドPADと隣接する位置に配置する。

(もっと読む)

液晶表示装置

【課題】それぞれの画素に対して十分に書き込みを行うことが可能な液晶表示装置を提供する。

【解決手段】この液晶表示装置100は、複数の表示画素10と複数のゲート線11および信号線12とを含む表示部1と、信号線12に対応する線を順次走査するHドライバ3と、Hドライバ3からの走査信号に基づいて映像データを記憶するラッチ回路6と、2値からなる信号が供給されるとともに、ラッチ回路6に記憶された映像データに基づいて2値からなる信号のいずれか一方を選択して映像信号として信号線12に供給する選択回路7とを備える。

(もっと読む)

表示装置

【課題】画像品質、位置検出精度の向上を実現する。

【解決手段】液晶パネル200の一方の面の側から、その表示領域PAへ照明光を出射するバックライト300の動作を、外光センサ素子32bによって得られた受光データに基づいて制御する。ここでは、表示領域PAに配置された外光センサ素子32bによって得られた受光データに基づいて、バックライト300の動作を制御する。

(もっと読む)

アクティブマトリクス型表示装置

【課題】アクティブマトリクス型表示装置において、ICチップの実装に要する表示部以外の面積を低減し、小型化、狭額縁化を達成する。また、ICチップの実装に伴う信号線の接続不良を低減する。

【解決手段】絶縁表面を有する第1の基板と、第1の基板に対向する絶縁表面を有する第2の基板と、第1の基板及び第2の基板がはめ込まれた外枠と、を有し、第1の基板には、信号線駆動回路、走査線駆動回路、及び画素領域が設けられ、第2の基板には、ロジック回路が設けられ、外枠には、溝、及び溝に形成された配線が設けられ、外枠の溝に形成された配線を介して信号線駆動回路及び走査線駆動回路の電極パッドとロジック回路の電極パッドとが電気的に接続され、画素領域と、ロジック回路が設けられる領域とは重なる。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】回路の小規模化を図れ、効率的なレイアウトが可能な集積回路装置等の提供。

【解決手段】集積回路装置10は、第1の方向(D1)に沿って配置される第1〜第Nのデータドライバブロックを含み、第1〜第Nのデータドライバブロックの各データドライバブロックは、第1〜第Mのサブドライバブロック(SDB0〜SDB5)を含む。各サブドライバブロック(SDB0)は、画像データ(ID0)を受け、画像データのD/A変換を行うD/A変換回路(DAC0)と、D/A変換回路の第2の方向(D2)において第1の方向に沿って配置され、D/A変換回路を共用する第1〜第Lのデータ線駆動回路(GR0、GG0、GB0)を含む。

(もっと読む)

オーバードライブ駆動回路、表示装置用ドライバIC、表示装置、及び、オーバードライブ駆動方法

【課題】モバイル機器の表示部に高画質な画像を表示可能とするオーバードライブ駆動回路、表示装置用ドライバIC、表示装置、及び、オーバードライブ駆動方法を提供することを課題とする。

【解決手段】1フレーム前の表示信号の信号レベルが、オーバードライブ駆動を行う駆動基準を満たしていたか否かを示す第1符号を第1符号記憶部10に記憶し、1フレーム前の表示信号の信号レベルが、所定の基準よりも高いか低いかを示す第2符号を第2符号記憶部11に記憶しておき、送信された表示信号の信号レベルが該駆動基準を満たすか否かを判定した後、第1符号に基づいて、送信された表示信号の信号レベルが前述の駆動基準を満たしていなかった信号レベルから該駆動基準を満たす信号レベルに変化したか否かを判定し、表示信号の信号レベルが変化したと判定される場合に、第2符号に応じて、送信された表示信号をオーバードライブ駆動する駆動信号を選択する。

(もっと読む)

液晶表示装置、電子機器

【課題】低温環境下であっても良好な駆動を実現する液晶表示装置を提供する。

【解決手段】1画素内に反射表示領域Rと透過表示領域Tとを備えた液晶表示装置であって、液晶層80を挟持する一対の基板と、一対の基板のうちの一方の基板の液晶層80とは反対側に配置された照明装置100と、一方の基板の液晶層80側において反射表示領域Rに設けられた反射膜70と、反射膜70と一方の基板との間に配置され、光を熱に変換する光熱変換素子40と、反射膜70と一方の基板との間に配置され、照明装置100から入射された光を光熱変換素子40に向けて集光する集光素子50と、光熱変換素子40に接続され、光熱変換素子40で発生した熱を液晶層80に伝導する熱伝導体42と、を備えることを特徴とする。

(もっと読む)

液晶プロジェクター

【課題】機器設計の自由度を制限したり機器を大型化させず、且つ耐久性や機器の寿命を低下させずに、光源を点滅させてスメアを低減することのできる液晶プロジェクターを提供する。

【解決手段】光源として固体素子光源1を用い、この固体素子光源1を、入力映像信号の1フレーム期間内に点滅させる点灯回路2を備える。

(もっと読む)

電圧生成回路及びそれを用いた表示装置

【課題】 コモン駆動回路の駆動能力を落とさず、左右対称な額縁や狭額縁化を実現可能な液晶表示装置を提供する。

【解決手段】 液晶表示基板10上にはコモン駆動回路4とともに、液晶表示装置駆動用のデータドライバ回路2とゲートドライバ回路3とが集積され、コモン電圧VCOMH,VCOMLが外部からパッドを通して印加されている。ゲートドライバ回路3は液晶表示装置の4端の内の1端に隣接するように配置する。コモン駆動回路4はゲートドライバ回路3が配置されている反対側の端に隣接し、できるだけパッド近くに、ゲートドライバ回路3の領域と同じ幅程度になるように配置する。コモン電圧VCOMH,VCOMLを印加するパッドとしてはコモン駆動回路4が配置された近くのパッドを使用する。

(もっと読む)

液晶表示装置及び液晶プロジェクターシステム

【課題】サンプリング信号のオーバーラップを防いでゴーストや縦筋の発生を抑え、且つ、書込み時間の変動を低減することでDAC回路の過剰な書込み能力を抑えることが可能な液晶表示装置を提供する。

【解決手段】タイミング制御回路20は第2のクロック信号HCKの立ち上がりを第1のクロック信号DCK分遅延させたサンプリング制御信号HCTN、HCTNBを生成し、水平走査回路11に出力する。水平走査回路11は第2のクロック信号HCKに同期して第1の出力信号HSRを出力するシフトレジスタ11aと、サンプリング制御信号と第1の出力信号との論理積の第2の出力信号HOUTを転送回路部に出力するアンド回路11bと、を具備する。

(もっと読む)

ドライバ及び表示装置

【課題】ドライバの仕様を切り替える場合、出力数制御端子が不要なドライバ及び表示装置を提供すること。

【解決手段】ドライバ(30)に供給されるシフトパルス信号(STH)は、複数の仕様用シフトパルス信号(STH’、STH”)のうちの1つの仕様用シフトパルス信号(STH’)(STH”)を表している。複数の仕様用シフトパルス信号(STH’、STH”)は、それぞれ仕様に応じて異なる出力数(“414”、“384”)を表している。1つの仕様用シフトパルス信号(STH’)(STH”)は、複数の出力数(“414”、“384”)のうちの設定出力数(“384”)を表している。これに応じて、ドライバ(30)内の出力切り替え制御部(40)は、複数の出力部(38−1〜38−414)のうちの、設定出力数(“384”)に対応する出力部群(38−1〜38−192、38−223〜38−414)を選択する。

(もっと読む)

表示駆動回路

【課題】表示駆動回路のレイアウトスペースを削減する。

【解決手段】データ線駆動回路5には、制御部11、グラフィックメモリアレイ(RAM)12、アドレスデコーダ13、プリチャージ回路14、ライトマスク回路15、ライト回路16、リード回路17、アドレスデコーダ18、RGBシフトレジスタ19、セレクタ回路20、ラインメモリ21、データセレクタ22、出力部23、及びマルチバス31が設けられる。マルチバス31は、動画データ(RGBデータ)、アドレスデータ、ライトデータ、ライトマスクデータ、及びリードデータに対応する共用データバスとして使用される。RGBシフトレジスタ19は、グラフィックメモリを介さずに直接パネルに動画データ(RGBデータ)を転送し、グラフィックメモリへのデータ書き込み動作及びグラフィックメモリからのデータ読み出し動作にも対応する。

(もっと読む)

データドライバ、集積回路装置及び電子機器

【課題】階調数が増加した場合にも、小規模な回路構成でデータ線に電圧を供給できるデータドライバ、集積回路装置及び電子機器を提供すること。

【解決手段】データドライバは、階調データを受け、階調データに対応した第1、第2の階調電圧VG1、VG2を第1〜第Nのサンプリング期間の各サンプリング期間に時分割に出力するD/A変換回路52と、D/A変換回路52を共用する第1〜第Nのデータ線駆動回路60-1〜60-Nを含む。第1〜第Nのデータ線駆動回路60-1〜60-Nは、第1〜第Nのサンプリング期間においてD/A変換回路52から出力された第1、第2の階調電圧VG1、VG2をサンプリングし、第1、第2の階調電圧VG1、VG2の間の階調電圧を生成する階調生成アンプ62-1〜62-Nを含む。

(もっと読む)

表示装置

【課題】省スペース化、低電力化を図れる表示装置を提供する。

【解決手段】表示を制御するための画像信号を記憶する記憶回路部21Aと、記憶回路部21Aが記憶した画像信号に基づいて表示制御をするアクティブ素子部22Bとを表示の最小単位であるドット毎に備え、パネルの基板上に、各ドットパターンに対応させて集積する。OEL発光部25Aは、6つのOEL素子が各アクティブ素子と接続されている。各OEL素子の面積は、接続された各メモリセルの画像信号が示す値に対応し、その面積比は、S1:S2:S3:S4:S5:S6=1:2:4:8:16:32となっており、面積に比例した明るさで発光するように設定されている。

(もっと読む)

表示装置の駆動回路

【課題】分離合成型D/A変換回路の誤差電圧、又はゲインが1ではない出力バッファの誤差電圧を時間的に均一化して表示むらを抑制する。

【解決手段】第1選択回路(16)に接続される第1バッファ(11)と、第2バッファ(12)のオフセット電圧の極性を周期的に反転してD/A変換回路(10)の出力電圧を時間的に平均化する。また、第2選択回路(17)に接続される出力バッファ(70)のゲインばらつきは、複数の素子(72、73)の位置関係を周期的に入れ換えることで出力バッファ(70)のゲインばらつきを時間的に平均化する。また、下位ビットが所定のデータのときに、第1バッファ(11)と第2バッファ(12)を介さないで、第1選択回路(16)で選択した第1選択電圧(VL)を第3ノード(N3)に直接出力する。

(もっと読む)

デジタルアナログ変換回路とデータドライバ及び表示装置

【課題】多ビット化に対して参照電圧の数の増大を抑制し、省面積(低コスト)を実現可能とし、画質の向上を図るデータドライバの提供。

【解決手段】第1乃至第(2×h+1)(ただし、hは所定の正整数)の参照電圧について、(2×j−1)番目の(ただし、jは1乃至h所定の正整数)のh個の参照電圧からなる第1の参照電圧群21と、(2×j)番目のh個の参照電圧からなる第2の参照電圧群22と、(2×j+1)番目のh個の参照電圧からなる第3の参照電圧群23とにグループ分けする。第1、第2、第3の参照電圧群21、22、23の出力のデジタル信号に基づき参照電圧Vrk、Vr(k+1)、Vr(k+2)を第4のサブでコーダに入力させ、重複も含めて少なくとも2個の電圧Vo1、Vo2を選択して出力する。それら電圧を増幅回路30へ入力し、合成電圧を出力する。

(もっと読む)

半導体表示装置

【課題】駆動回路の面積を小さく、駆動周波数を低くし、かつ高精細化したデジタル階調方式の半導体表示装置を提供する。

【解決手段】デジタル階調方式の半導体表示装置の駆動回路において、ソース信号線群を複数のグループに分け、各グループに1組のD/A変換回路を設けて、該1組のD/A変換回路によって、複数のソース信号線を時分割駆動する。さらにD/A変換回路は、上位ビットのD/A変換を行う第1のD/A変換回路と、下位ビットのD/A変換を行う第2のD/A変換回路とを有する。さらに駆動周波数を低減するため、ソース信号線群を2群に分け、一方を第1のソースドライバ、他方を第2のソースドライバによって並列駆動する。

(もっと読む)

点灯装置、バックライトユニット及び液晶表示装置

【課題】複数の熱陰極ランプを用いた点灯装置において、液晶表示装置のバックライトユニットに適するように配線をコンパクト化・軽量化し、且つ隣り合う熱陰極ランプのランプ電流を逆位相にできる構成を提供する。

【解決手段】複数の熱陰極ランプLa1〜La4を点灯するための点灯回路と、前記複数の熱陰極ランプLa1〜La4のそれぞれのフィラメントF11〜F14、F21〜F24を予熱するための予熱回路Y1と、複数の回路基板を有し、第一の回路基板には前記点灯回路及び前記予熱回路Y1の一部が実装され、第二の回路基板には、前記予熱回路Y1の一部が実装または配線される。例えば、第一の回路基板には点灯回路及び予熱回路Y1の構成部品:コンデンサC11〜C15、予熱トランスT1が実装され、第二の回路基板には予熱回路Y1の構成部品:コンデンサC22〜C25及びフィラメントF21〜F24の予熱配線が実装または配線される。

(もっと読む)

表示装置、表示装置の駆動方法および電子機器

【課題】キャンセル容量を搭載した従来回路よりもアナログスイッチ部分の回路サイズを小さくする。

【解決手段】アナログスイッチHSW(HSW1〜HSWm)を、入力端が映像信号線53に接続された第1スイッチ(アナログスイッチ)HSWcと、当該第1スイッチHSWcの出力端と信号線32(32−1〜32−m)との間に接続されたキャンセル容量CSWcと、映像信号線53と信号線32との間に接続された第2スイッチ(アナログスイッチ)HSWdとによって構成し、第2スイッチHSWdによって第1スイッチHSWcの充放電能力(駆動能力)を補うようにする。

(もっと読む)

アクティブマトリクス回路基板および表示装置

【課題】データ線の電位変動を抑制することで画像データの書き込みが確実に行え、回路規模が大幅に増大することがないアクティブマトリクス回路基板を提供する。

【解決手段】本発明のアクティブマトリクス回路基板1は、各画素2に、ゲート線4およびデータ線5に接続された画素スイッチング素子(駆動用TFT18)と、画素スイッチング素子に接続され、データ線および画素スイッチング素子を介して入力される画像データを記憶し、当該画像データを示す出力信号を出力するメモリ回路(SRAM19)と、メモリ回路と画素電極21との間に設けられ、メモリ回路からの出力信号に基づいて第1制御線11または第2制御線12のいずれか一方を画素電極21と電気的に接続するスイッチ回路20と、が備えられ、画素表示部3内に位置する各データ線5に、データ線5の電位を保持する電位保持手段(ラッチ回路33)が接続されている。

(もっと読む)

81 - 100 / 432

[ Back to top ]