Fターム[4E351AA03]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | プリント基板の材料と性質 (2,230) | 合成樹脂を主体とするもの (1,208) | 樹脂材料を特定したもの (941) | エポキシ樹脂系(ガラスエポキシ基板等) (263)

Fターム[4E351AA03]に分類される特許

161 - 180 / 263

導電性ペースト組成物並びにそれを用いたプリント配線基板とその製造方法

【課題】高品質なビアホール導体をバラツキ少なく安定的に形成し、小径ビアホールにおいても高い接続信頼性を有するビアホール充填用導電性ペースト組成物と、それを用いたプリント配線基板を実現する。

【解決手段】(a)平均粒径が0.5〜20μmの導電性金属フィラー80〜95重量%、(b)フタル酸ジアリルを主成分とし、トリアリルイソシアヌレートを含む液状樹脂成分4〜18重量%、(c)硬化剤1〜5重量%から成る組成物であることを特徴とする導電性ペースト組成物並びにそれを用いたプリント配線基板とその製造方法である。

(もっと読む)

エンベデッド印刷回路基板の製作方法

【課題】誘電物質を同一な厚みに加工することが容易なエンベデッド印刷回路基板及びその製作方法を提供する。

【解決手段】本発明によるエンベデッド印刷回路基板の製作方法は、基材に第1伝導層及び第2伝導層を順次積層する段階と、第2伝導層にホールを形成した後、誘電物質で充填する段階と、第2伝導層の上に第3伝導層を積層した後一部を除去することで誘電物質の上部に位置する上部電極及び第1伝導層と電気的に繋がるパッドを形成する段階と、第3伝導層の上に絶縁層を積層した後上部電極及びパッドと電気的に繋がるビアホール及び外層回路を形成する段階とを含むが、これにより誘電物質を同一な厚みに容易に加工することができて、キャパシタと抵抗を同時に具現することができる。

(もっと読む)

薄膜キャパシタが内蔵された印刷回路基板及びその製造方法

【課題】低温で所望の誘電特性を有する非晶質常誘電体薄膜を形成すると共に製品の信頼性を高めることの出来る薄膜キャパシタが内蔵された印刷回路基板及びその製造方法を提供する。

【解決手段】絶縁基材31a上に順次下部電極33と、上記下部電極上に形成された非晶質常誘電体膜35と、上記常誘電体膜上に形成された金属シード層37と、上記金属シード層上に形成されたその表面粗度Raが300nm以上である上部電極39と、を形成して薄膜キャパシタが内蔵された印刷回路基板30とする。この場合、上記下部電極33は無電解メッキで形成された部分33aと電解メッキで形成された部分33bとを含む。

(もっと読む)

基板の配線構造

【課題】多層構造を持たない基板において、高周波信号の伝送品質を確保することが可能な基板の配線構造を提供することを目的とする。

【解決手段】複数の集積回路を搭載可能な基板の配線構造100において、集積回路間を接続するための信号配線150と、対向配置される第1電源層130および第2電源層140と、信号配線150に略並行に配されたリターン・パス用配線130a、140aとを備え、リターン・パス用配線130aの両終端を第1電源層(Vcc層)130に接続し、リターン・パス用配線140aの両終端を第2電源層(Gnd層)140に接続する。

(もっと読む)

プリント配線板

【課題】セミアディティブ法によるプリント配線板の導体回路パターン形成において、導体回路間のショート不良が少なく、回路形成性のよいプリント配線板の製造方法を提供する。

【解決手段】導体回路パターンとなる電気銅めっき層の形成時の電流密度よりも大きい電流密度で作製された厚み5μm以下の銅箔を貼り付けた層間絶縁樹脂を内層回路基板の上下面に積層し、さらに、導体回路パターン部以外の銅のエッチングにハロゲンを含まない酸及び過酸化水素を主成分とするエッチング液を用いることで課題を解決した。

(もっと読む)

高誘電性薄膜用コーティング溶液及びこれを用いた誘電薄膜の製造方法、並びにこの製造方法により製造される誘電薄膜およびこの誘電薄膜を含むエンベッディドキャパシタ

【課題】高い誘電性を有する薄膜の製造のためのコーティング溶液、及びこれを用いた誘電薄膜の製造方法を提供する。

【解決手段】チタニウムアルコキサイド、β−ジケトンまたはβ−ジケトン改質化合物、及び電子供与基に改質されたベンゾ酸を含んで成る薄膜製造のためのコーティング溶液及び上記コーティング溶液を低温で乾燥して薄膜を結晶化させる誘電薄膜の製造方法を提供する。このように提供されるチタニウムコーティング溶液は非常に安定しており、基板の種類にかかわらず低温で薄膜工程進行が可能なだけでなく、PCB工程内でインライン工程進行が可能である。

(もっと読む)

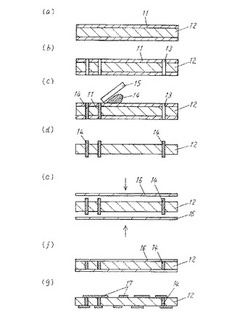

コンデンサを内蔵した基板およびその製造方法

【課題】大容量かつ高信頼性のコンデンサを量産性よく基板に内蔵する。

【解決手段】コンデンサの一方の電極となる第一導体パターン12を転写用基板11上に形成する工程、第一導体パターンを絶縁材13に埋設するように転写して第一基板構成材を作成する工程、コンデンサの他方の電極となる第二導体パターン22を転写用基板上に形成する工程、第二導体パターンを絶縁材23に埋設するように転写して第二基板構成材を作成する工程、第一及び第二基板構成材の何れか一方の導体パターン埋設側の面に誘電体層14aを配する工程、第一及び第二基板構成材をプレスして一体化する工程を含む。誘電体層は、樹脂にフィラーを混入して形成した誘電体シートを真空ラミネートする。

(もっと読む)

配線基板および電子装置

【課題】ますます周波数の高くなる高周波信号を高速に伝送することが容易な配線基板を提供することにある。

【解決手段】接地導体層6と電源供給用導体層10とが絶縁層2を介して対向するように形成された配線基板において、接地導体層6および電源供給用導体層10の少なくとも一方の絶縁層側の主面に絶縁層に埋入した複数の突起12を形成している。

(もっと読む)

配線回路基板の製造方法

【課題】ウィスカーの発生を抑制するとともに、電子部品との接続性を確保しつつ接続性のばらつきを低減することができる配線回路基板の製造方法を提供することである。

【解決手段】 ベース絶縁層BIL上に金属薄膜31および導体層33からなる配線パターン12を形成し、配線パターン12を覆うように無電解錫めっき層34を形成する。ここで、配線パターン12および錫めっき層34に加熱処理を施す。加熱処理温度は175〜225℃とし、加熱処理時間は2〜10分とする。加熱処理を施すことにより、銅および錫からなる混合層35が形成される。その後、ベース絶縁層上の所定領域で配線パターン12および錫めっき層34を覆うようにソルダーレジストSOLを形成する。次に、ソルダーレジストSOLの熱硬化処理を行う。

(もっと読む)

プリント配線板、半導体チップ搭載基板、半導体パッケージ、プリント配線板の製造方法、及び半導体チップ搭載基板の製造方法

【課題】 ブリッジの発生が抑制されたプリント配線板、半導体チップ搭載基板、半導体パッケージ、プリント配線板の製造方法、及び半導体チップ搭載基板の製造方法を提供する。

【解決手段】 このプリント配線板の製造方法では、まず、複数の銅配線4が表面2a上に設けられた基板2上に、複数の銅配線4を露出させる開口6aを有する絶縁マスク6を形成する。次に、複数の銅配線4間に絶縁物8を形成する。絶縁物8を形成した後、複数の銅配線4上に、ニッケルめっき皮膜12、パラジウムめっき皮膜14及び金めっき皮膜16を順に形成する。

(もっと読む)

抵抗素子、プリント配線板及びそれらの製造方法

【課題】本発明は、抵抗値の安定した抵抗素子及びこれを具備するプリント配線板を得ることを課題とする。また、抵抗体を保持する基板を傷つけることなくトリミングを行うことのできる抵抗素子及びこれを具備するプリント配線板を得ることを課題とする

【解決手段】抵抗体と抵抗素子を具備する抵抗素子であって、当該抵抗素子を保持する基板上に接着剤層を介して抵抗体が接着されていることを特徴とする抵抗素子とする。この抵抗素子は転写によってプリント配線板上に配置され、転写の前に転写基材上でトリミングが行われているため、トリミング時に下層の配線板を傷つけることがなく、良品のみを用いることができる。

(もっと読む)

積層体及び電気回路基板

【課題】ハンドリング性能に優れた、静電容量の大きい容量素子を精度良く製造することのできる積層体及びこれを用いた容量素子を内蔵した電気回路基板を提供する。

【解決手段】誘電体層と、誘電体層の一方の面に設けられた第一の導体層と、誘電体層の他方の面に設けられた第二の導体層とを具備し、第一の導体層は第二の導体層より薄いことを特徴とする積層体を用いることで、精度良く容量素子及び配線を電気回路基板に作り込むことができる。

(もっと読む)

メモリカード

【課題】 半導体メモリチップのマウントの密着性やボンデイング性への影響を低減しつつ、製造コストの削減を図ることが可能なメモリカードを提供する。

【解決手段】 本発明に係るメモリカードは、電源端子1、グランド端子2が形成された基板3と、この基板上に設けられたパッド4とワイヤボンディングにより接続されるとともに、電源端子1およびグランド端子2に電気的に接続されたNANDメモリチップ6と、電源端子1とグランド端子2との間にNANDメモリチップ6と並列に接続されるように基板3上に形成され、NANDメモリチップ6に電力を供給するための配線キャパシタ7と、を備える。配線キャパシタ7は、基板3上に形成された電源側配線10と、グランド側配線11と、電源側配線10とグランド側配線11との間に設けられたソルダレジスト12と、を有する。

(もっと読む)

固体電解コンデンサ内蔵回路基板とその製造方法

【課題】高い絶縁信頼性を有する、薄型、大容量の固体電解コンデンサ内蔵回路基板とその製造方法を提供する。

【解決手段】多孔質部を有する弁金属シート1を内蔵した回路基板において、前記弁金属シート1の一部に固体電解コンデンサを形成し、前記弁金属シート1の前記固体電解コンデンサを形成していない領域の多孔質部2に液状樹脂の硬化物からなる絶縁層3を充填し、前記固体電解コンデンサと、前記回路基板の配線パターン4とを電気的に接続することを特徴とする固体電解コンデンサ内蔵回路基板である。

(もっと読む)

積層回路基板

【課題】 低融点金属を含む導電性ペーストを使用した積層回路基板において、銅箔と低融点金属を含む導電性ペーストとの界面にボイド、亀裂が発生せず、接続信頼性の高い積層回路基板を提供する。

【解決手段】 本発明の積層回路基板は、銅箔または銅合金箔の少なくとも片面の表面粗さが0.1μm〜5μm以下の元箔上に、平均付着量が150mg/dm2以下で表面粗さが0.3〜10μmの突起物からなる粗化処理層が形成された粗化処理銅箔の該粗化処理層上に、低融点金属を含有する導電性ペーストが設けられ、かかる表面処理銅箔を樹脂基板と積層したものである。

(もっと読む)

薄膜エンベディッドキャパシタンス、その製造方法、及びプリント配線板

【課題】 単位あたりの静電容量の大きな薄膜エンベディッドキャパシタンス及びその製造方法を提供する。

【解決手段】 非降伏状態の金属材料からなる配線用金属薄膜2Pと;前記配線用金属薄膜上に形成された第1電極4と;前記第1電極及び前記配線用金属薄膜上に、常温以上、前記配線用金属薄膜の降伏温度未満の温度でスパッタリング法により形成された、前記配線用金属薄膜よりも小さな熱膨張率を有する誘電体材料層6と;前記誘電体材料層上に形成された第2電極8と;を備える、薄膜エンベディッドキャパシタンス、及びその製造方法を提供する。

(もっと読む)

積層回路基板

【課題】 錫と銀からなる導電性ペーストを使用した積層回路基板において、銅箔と低融点金属を含む導電性ペーストとの界面にボイド、亀裂が発生せず、接続信頼性の高い積層回路基板を提供する。

【解決手段】 本発明の積層回路基板は、銅箔または銅合金箔の少なくとも片面の表面粗さが0.1μm〜5μmの元箔上に、平均付着量が150mg/dm2以下で表面粗さが0.3〜10μmの突起物からなる粗化処理層が形成された粗化処理銅箔の該粗化処理層上に、平均粒径が0.1〜10ミクロン径であり20〜80質量%を占める錫と銀からなる金属粒子を穿設した貫通孔に充填した熱可塑性樹脂基板とを積層したものである。

(もっと読む)

抵抗素子、それを内蔵した多層配線基板および抵抗素子の抵抗値調整方法

【課題】配線基板に内蔵する抵抗素子を形成する際に抵抗体の形成時に形成不良が発生するとトリミングの範囲を超えてしまい、抵抗値を調整することができなかった。

【解決手段】本発明では、第一の電極と第二の電極と両電極間を接続する抵抗体とを備え、抵抗体をトリミングすることで抵抗値の調整が可能な抵抗素子において、前記第二の電極の端部は前記第一の電極の端部に対して傾斜している、あるいは前記第二の電極の端部は曲線であることを特徴とする抵抗素子とすることで、同じ基本形状の抵抗素子から大きな幅を持って抵抗値を調整することが可能となった。また、精度の高い加工が行える抵抗素子を得ることができた。

(もっと読む)

樹脂付き金属箔、金属張積層板、これを用いたプリント配線板およびその製造方法

【課題】絶縁樹脂組成物層と金属箔との界面の密着性と平坦性を両立し、かつ、経済性や取扱い性等のプリント配線板製造時に係る実用的な要素をも満たす金属張積層板または樹脂付き金属箔を提供することを目的とし、さらに、該金属張積層板または樹脂付き金属箔を用い、信頼性および回路形成性に優れ、導体損失の非常に少ないプリント配線板およびその製造方法を提供することを目的とする。

【解決手段】絶縁樹脂組成物層と、絶縁樹脂組成物層の片面もしくは両面に固着してなる金属箔とを有する樹脂付き金属箔において、金属箔の少なくとも絶縁樹脂組成物層側が表面処理されており、かつ金属箔の両面が実質的に粗し処理されていないことを特徴とする金属張積層板または樹脂付き金属箔を提供する。

(もっと読む)

配線基板及びその製造方法

【課題】セラミック副コアを収容したコア基板上に配線積層部を形成する際に、配線積層部となる誘電体層及びそれに貫通形成されるビア導体とセラミック副コアの導体パッドとの密着性が十分に得られる配線基板及びその製造方法を提供することを目的とする。

【解決手段】 本発明の配線基板1は、コア基板CBに収容されたセラミック副コア3の導体パッド31において、その表面にCuメッキ層が形成され、且つ、Cuメッキ層の表面が高分子材料との密着性を向上させるためのCu表面化学処理が施された処理面とされ、処理面に配線積層部L1,L2の最下層の誘電体層B11,B21及びそれに貫通形成されたビア導体6が接触してなることを特徴とする。

(もっと読む)

161 - 180 / 263

[ Back to top ]