Fターム[4K030BA09]の内容

Fターム[4K030BA09]に分類される特許

121 - 140 / 167

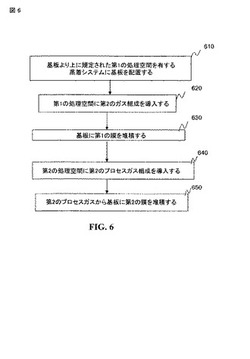

シングルチャンバ内で異なる堆積プロセスを実行する方法およびシステム

【課題】 シングルチャンバ内で異なる堆積プロセスを実行する方法およびシステムを提供することである。

【解決手段】 第1の蒸着プロセスに係る処理空間に第1のプロセスガス組成を導入し、基板上に第1の膜を堆積させ、第1の処理空間よりサイズが異なる第2の処理空間に第2のプロセスガス組成を導入し、そして第2のプロセスガス組成から基板上に第2の膜を堆積させる基板上への蒸着のための方法、コンピュータ読み取り可能なメディア、およびシステムである。このように、システムは、第1のボリュームを有する第1の処理空間を含む処理チャンバを有する。処理チャンバは、更に、第1の処理空間の少なくとも一部を含んで、第1のボリュームと異なる第2のボリュームを有する第2の処理空間を含む。

(もっと読む)

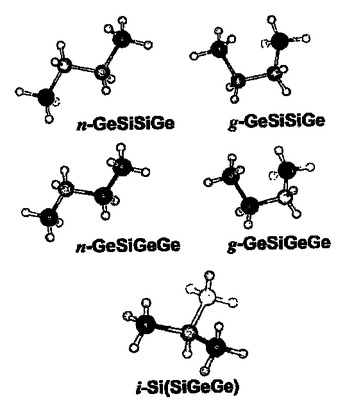

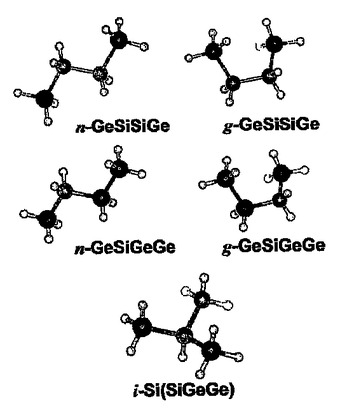

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:SiHn1(GeHn2)yによって定義される。式中、yは2,3または4であり;n1は、0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たす。  (もっと読む)

(もっと読む)

化学蒸着法により形成されたガス貯蔵コンテナーライニング

ガス貯蔵コンテナーの内部にコーティングする方法であって、上記方法は化学蒸着のための前駆物質を上記貯蔵コンテナーに供給する工程、および金属コーティングを上記コンテナーの内部表面上に形成する工程を含み、上記コーティングは化学蒸着のための前駆物質より形成される、方法。また、内部表面を有するガス貯蔵容器を含むガス貯蔵コンテナーであって、上記貯蔵容器の上記内部表面上に形成されたライナーを有する、ガス貯蔵コンテナー。上記ライナーは約99重量%またはそれ以上の純度のタングステン金属を含み得る。さらに、化学蒸着前駆物質発生器および上記前駆物質をガス貯蔵コンテナー中に輸送するための前駆物質注入アセンブリを含み得る金属ライニングされたガス貯蔵コンテナーを作製するためのシステム。上記システムは、上記ガス貯蔵容器からガス状の蒸着生成物を除くための排気出口も含み得る。  (もっと読む)

(もっと読む)

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、新規水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの新規化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:(SiHn1)x(GeHn2)yによって定義される。式中、xは2,3または4であり;yは1,2または3であり;x+yは3,4または5であり;n1は、化合物中の各Si原子に関して独立に0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たし;但し、yが1のとき、n2は0ではなく;さらに、xが3、かつ、yが1のとき、n2は2または3であり;さらに、xが2、かつ、yが1のとき、n2は3である。  (もっと読む)

(もっと読む)

成膜装置、成膜方法、及び光電変換装置の作製方法

【課題】基板のカールを抑制し、信頼性の高い光電変換装置を得ることを課題とする。

【解決手段】基板を送り出すローラを有する第1の搬送室と、放電電極を有する成膜室と、前記搬送室と前記成膜室との間、もしくは前記成膜室どうしの間に設置されたバッファ室と、前記バッファ室の前記基板が出入りする部分に設けられたスリットと、前記基板を巻き取るローラを有する第2の搬送室と有し、前記スリットには少なくとも1つのタッチロールが設置されており、前記タッチローラは前記基板の成膜面に接触する成膜装置、及びこのような成膜装置を用いて行う成膜方法並びに光電変換装置の作製方法に関する。このような成膜方法を用いると、素子の受光領域に傷を付けるのを防ぐことができる。

(もっと読む)

ドープされた窒化シリコン膜の低温堆積のための方法及び装置

ドープされた窒化シリコン膜の低温堆積のための方法及び装置が開示される。改善には、低温処理のための均一な熱分配とプロセス化学薬品の均一な分配を与えるCVDチャンバの機械的設計と、基板を加熱し、シリコン含有前駆物質を混合領域がアダプタリングと一つ以上のブロッカープレートによって画成された処理チャンバと排気システムへ流し、該アダプタリングと該排気システムの一部を加熱し、水素、ゲルマニウム、ホウ素、又は炭素含有前駆物質の一つ以上を該処理チャンバへ流すことによって、更に、所望により、窒素含有前駆物質を該処理チャンバへ流してもよいことによって、基板上にシリコンと窒素を含む少なくとも一つの層を堆積させる方法が含まれる。 (もっと読む)

半導体ヘテロ構造、および半導体ヘテロ構造を形成する方法

【課題】ヘテロ構造を形成する方法、ならびによりよい表面粗さ特性および/または埋込み境界面粗さ特性を有する、対応する半導体ヘテロ構造を提供すること。

【解決手段】本発明は、第1の面内格子パラメータa1を有する基板を提供するステップと、第2の面内格子パラメータa2を有するバッファ層を設けるステップと、このバッファ層の上に上部層を設けるステップとを含む、半導体ヘテロ構造を形成する方法に関する。半導体へテロ構造の表面粗さを改善するために、バッファ層と上部層の間に追加層が設けられ、この追加層は、第1および第2の格子パラメータの間である第3の面内格子パラメータa3を有する。

(もっと読む)

Si含有膜の選択的堆積のための断続的堆積処理方法

断続的堆積処理において基板においてSi含有膜を選択的に形成する方法を提供する。その方法は、成長表面及び非成長表面を備える段階と、塩素化シランガスのパルスに基板を同時に晒しながら、基板をHXガスに晒すことにより、成長表面においてSi含有膜を選択的に形成する段階とを有する。Si含有膜は、酸化物、窒化物又は酸窒化物非成長表面でなく、Si又はSiGe成長表面に選択的に形成されるSi膜又はSiGe膜である。  (もっと読む)

(もっと読む)

Ge−Sb−Te薄膜蒸着方法

【課題】Ge−Sb−Te薄膜蒸着方法を提供する。

【解決手段】基板が内蔵されたチャンバであってGe、Sb及びTeのうち選択されたいずれか一つを含む第1前駆体と、Ge、Sb及びTeのうち選択された他の一つを含む第2前駆体と、Ge、Sb及びTeのうち選択された残りの一つを含む第3前駆体と、をフィーディング及びパージすることで基板上にGe−Sb−Te膜を形成するGe−Sb−Te膜形成ステップと、少なくとも第1ないし第3前駆体のうちいずれか一つがフィーディングされる間にチャンバに反応ガスをフィーディングする反応ガスフィーディングステップと、を含む。

(もっと読む)

Si含有膜を成膜する連続的成膜処理方法

連続的堆積処理でSi膜を成膜する方法が供される。当該方法は、処理チャンバ内に基板を供する工程、前記基板を塩素化されたシランガスに曝露することによって塩素化されたSi膜を成膜する工程、及び前記塩素化されたSi膜をドライエッチングすることによって前記Si膜の塩素含有量を減少させる工程、を有する。Si膜は基板上に、選択的又は非選択的に堆積されて良い。堆積は自己制限的であっても良いし、非自己制限的であっても良い。他の実施例は、連続的堆積処理でSiGe膜を成膜する方法を供する。  (もっと読む)

(もっと読む)

気相成長装置

【課題】 均熱板の材質を改善し、不純物の混入の少ない半導体結晶を成長することが可能な半導体製造装置を提供すること。

【解決手段】 加熱した半導体基板4上に原料ガス15を流し、半導体基板4上に半導体結晶を気相成長する半導体製造装置において、半導体基板4を均一に熱するために、半導体基板4に隣接して、加熱源との間に均熱板7をセットし、この均熱板7の材質に炭化珪素またはガス不透過性のカーボンを用いる。

(もっと読む)

ゲルマニウム膜を堆積させる方法

化学気相堆積法により、連続的で滑らかなゲルマニウム膜層が提供される。このゲルマニウム膜層は十分に低い温度で金属基板上に堆積されて、アルミニウムおよび銅など、温度の影響を受けやすい材料と一緒に使用するのに適したゲルマニウムデバイスを提供する。別の化学気相堆積法により、連続的で滑らかなシリコン−ゲルマニウム膜層が提供される。このシリコン−ゲルマニウム膜層は十分に低い温度で二酸化シリコン基板上に堆積されて、アルミニウム、銅およびカルコゲナイドメモリ材料など、温度の影響を受けやすい材料と一緒に使用するのに適したゲルマニウムデバイスを提供する。  (もっと読む)

(もっと読む)

インサイチュでドープしたn型エミッタのドーピングプロファイルの改善方法

エミッタ−ベース接合を形成する方法。前記方法は、ベース層(26)を設けるステップと、一組の処理ガスからなるガスの流れを用いて、ベース層(26)上にドープしたモノエミッタ層(28)を成長させるステップとを含み、ガスの流れは、ガスの流れの最初の数秒間、処理ガスにゲルマニウム(Ge)源を添加することを含む。  (もっと読む)

(もっと読む)

半導体ウェーハの製造方法

【課題】貫通転位密度が少なく、表面の粗さが小さい表面に二次元引張り歪みを内在させた歪みSi層が形成された半導体ウェーハの製造方法を提供する。

【解決手段】Si基板上にSiGe混晶層を形成する工程と、形成したSiGe混晶層上にSi層を形成する工程とを含む半導体ウェーハの製造方法の改良であり、その特徴ある構成は、SiGe混晶層を形成する工程が高温形成工程と低温形成工程の双方を含み、高温形成工程が750〜1100℃の温度範囲で濃度が傾斜又は一定のSiGe混晶層を形成し、かつ低温形成工程が高温形成工程の温度より100〜600℃低い500〜750℃の温度範囲で濃度が傾斜又は一定のSiGe混晶層を形成するところにある。

(もっと読む)

積層層構造およびその形成方法

【課題】基板と、少なくとも2つの化合物AおよびBを含む材料の複数の層のスタックとから成る積層層構造の製造方法を提供する。

【解決手段】化合物Aが基板3上でホモエピタキシャル成長又はヘテロエピタキシャル成長が十分にできるような結晶構造を有し、スタック5の層の少なくとも一部は、xが0≦x≦1の範囲を有する組成パラメータであり、且つ、組成パラメータ(1−xg)が対応する層の厚みの上に徐々に、特に線形に増大する勾配組成AxB(1−xg)を有する。表面粗さと転位密度に関して積層層構造1の品質を改善するため、スタック5内の勾配組成を有する層と後続層との界面で、組成パラメータが、勾配組成を有する層側の組成パラメータ(1−xg)よりも小さくなるように選択される。本発明は、また、このような積層層構造1を製造する方法にも関する。

(もっと読む)

高誘電率膜上のシリコンオキサイドキャップ

【課題】高kゲート絶縁膜上のドープされたシリコンゲート間に短絡をもたらす欠陥、トラッピングを回避する、前記高kゲート絶縁膜および前記高kゲート絶縁膜上のシリコンオキサイド膜の製造法を提供する。

【解決手段】原子層堆積プロセスを用いて基板上に高kゲート絶縁材料を堆積することを包含する、半導体基板上に集積回路構造を形成するための方法。シリコンオキサイドキャッピング層は、高速熱化学蒸着プロセスにおいてゲート絶縁材料上に堆積される。ゲート電極は、シリコンオキサイドキャッピング層上に形成される。

(もっと読む)

固相エピタキシー方式を用いた半導体素子のコンタクト形成方法

【課題】SPE方式及び後続熱処理を用いてコンタクト物質をエピタキシャルシリコンとして形成する場合に発生する後続CMP工程でのディッシング現象を最小化させること。

【解決手段】 接合層が形成された半導体基板の上部に層間絶縁膜を形成するステップと、前記層間絶縁膜をエッチングして前記接合層を露出させるコンタクトホールを形成するステップと、前記コンタクトホールの底面の自然酸化膜を除去するための表面洗浄ステップと、固相エピタキシー方式を用いて前記コンタクトホールを埋めるコンタクト層を形成するが、前記接合層とのコンタクト領域ではエピタキシャル層に成長させ、前記コンタクトホールの残りの領域及び前記層間絶縁膜の表面では非晶質層に成長させるステップと、前記コンタクト層の非晶質層を選択的に平坦化させ、セルランディングプラグコンタクトを形成するステップとを含む。

(もっと読む)

処理管

【課題】バッチ式リモートプラズマ処理装置における処理管を提供する。

【解決手段】バッチ式リモートプラズマ処理装置に適用される処理管は、複数枚のウエハ1が積層して収容される処理室12と、処理室12から区画され、処理ガス41が供給される放電室33であって、少なくともこの放電室33内でプラズマ40を生成する一対の電極部を収容可能な放電室33と、を備えている。処理管は放電室33内のプラズマ40で活性化させた粒子42を処理室12へ供給することができる。

(もっと読む)

高機能粒子構造を有する多結晶膜の堆積方法

多結晶Si含有膜の粒子構造を制御するための方法は、最初の段階で堆積される第1の膜層のモフォロジーが、後の段階で堆積される第2の膜層のモフォロジーに有利に作用するような、膜を段階的に堆積するステップを含む。例示する実施形態では、最初の段階は、アニーリングするステップを含む。別の実施形態では、後の段階は、第1の層用とは異なる堆積条件下で第2の層を堆積するステップを含む。  (もっと読む)

(もっと読む)

膜の製造方法

【課題】 高密度なダイヤモンドライクカーボン膜、シリコン膜、ゲルマニウム膜等の製造方法を提供することを目的とする。

【解決手段】 14族元素を含む化合物、及び超臨界状態とした物質の混合系でプラズマ放電を行うことにより基材上に膜を形成する膜の製造方法である。ここで、14族元素が炭素であり、形成される膜がダイヤモンドライクカーボン膜であることが好ましい。また、14族元素がケイ素であり、形成される膜がシリコン膜であることが好ましい。さらに、14族元素がゲルマニウム原子であり、形成される膜がゲルマニウム膜であることが好ましい。

(もっと読む)

121 - 140 / 167

[ Back to top ]