Fターム[4K030BA09]の内容

Fターム[4K030BA09]に分類される特許

141 - 160 / 167

低エネルギープラズマを用いた化学気相蒸着法による半導体層の形成及び半導体ヘテロ構造デバイス

厚さ100nm〜800nmを有し高度に緩和したエピタキシャル半導体層(52)をチャンバ内で形成する方法である。本発明の方法は、基板キャリア上の成長チャンバ内に基板(51)を配置し、基板(51)の基板温度(Ts)を350〜500℃の範囲で一定に維持し、基板(51)をプラズマに曝すように成長チャンバ内に高密度・低エネルギーのプラズマを発生させ、ガス導入口からシランガス(SiH4)とゲルマンガス(GeH4)をチャンバ内に導入し、その際、上記半導体層(52)を成長速度1〜10nm/sで蒸着により形成可能にシランガスとゲルマンガスの流速を調整し、かつ上記半導体層(52)のゲルマニウム濃度xを、0<x<50%とする。  (もっと読む)

(もっと読む)

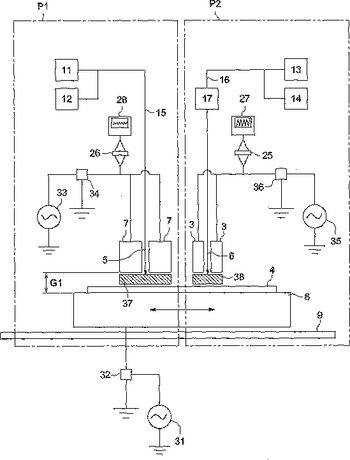

薄膜製造方法および形成された薄膜を有する基材

大気圧もしくはその近傍の圧力下、高周波電界Aを発生させた第1の放電空間に放電ガスを供給して励起し、前記励起した放電ガスのエネルギーを薄膜形成ガスに伝えて励起し、基材を、前記励起した薄膜形成ガスに晒すことにより、前記基材上に薄膜を形成する第1の工程と、高周波電界Bを発生させた第2の放電空間に酸化性ガスを含有するガスを供給して励起し、前記第1の工程で形成された前記薄膜を、前記励起した酸化性ガスを含有するガスに晒す第2の工程とを有することを特徴とする薄膜形成方法。  (もっと読む)

(もっと読む)

化学気相蒸着法によるGeSbTe薄膜の製造方法

【課題】化学気相蒸着法によるGeSbTe薄膜の製造方法を提供する。

【解決手段】反応チャンバ内でGeを含む第1前駆体、Sbを含む第2前駆体及びTeを含む第3前駆体間の化学反応により基板の表面にGeSbTe薄膜を形成する第1ステップ及び前記GeSbTe薄膜の表面を水素プラズマで表面処理する第2ステップを含むGeSbTe薄膜の製造方法である。

(もっと読む)

カルコゲニド材料の化学蒸着法

電気および光学カルコゲニド材料を生成するための化学蒸着法(CVD)工程である。好ましい実施形態では、本発明のCVDにより蒸着した材料は次の特性のうち1つまたは1つ以上の特性を実現する:電気スイッチング、累積機能、セッティング機能、可逆的多重状態作動、リセッティング機能、認識機能、可逆性の非結晶‐結晶転移。一実施形態では、カルコゲン元素を含有した少なくとも1層を含んだ多層構造がCVDによって蒸着され、蒸着後のエネルギー付加を施されて、本発明の性質を有するカルコゲニド材料を生成する。別の実施形態では、本発明による性質を備えた単層のカルコゲニド材料が、少なくとも1つがカルコゲン元素前駆物質である3つまたは3つ以上の蒸着前駆物質を含んだCVD蒸着工程から形成される。好ましい材料は、カルコゲンTeならびにGeおよび/またはSbを含有しているものである。 (もっと読む)

ゲルマニウム前駆体、これを利用して形成されたGST薄膜、前記薄膜の製造方法及び相変化メモリ素子

【課題】ゲルマニウム前駆体、これを利用して形成されたGST薄膜、該薄膜の製造方法及び相変化メモリ素子を提供する。

【解決手段】ゲルマニウム、窒素及びシリコンを含有した低温蒸着用のゲルマニウム前駆体、これを利用して形成された窒素及びシリコンでドーピングされたGST薄膜、該薄膜の製造方法及び相変化メモリ素子である。これにより、低温蒸着用のゲルマニウム前駆体は、窒素及びシリコンを含有しているところ、薄膜、より具体的には、窒素及びシリコンでドーピングされたGST薄膜形成時に低温蒸着が可能である。特に、低温蒸着時、水素プラズマを利用できる。低温蒸着用のゲルマニウム前駆体を利用して形成された窒素及びシリコンでドーピングされたGST相変化膜は、減少したリセット電流を有するところ、これを備えたメモリ素子は、集積化が可能になり、高容量及び高速作動が可能である。

(もっと読む)

歪みシリコンウェーハの製造方法

【課題】SiGe層を有する歪みシリコンウェーハにおいて、SiGe層上に形成される歪みSi層における貫通転位密度の一層の低減化を図ることができる歪みシリコンウェーハの製造方法を提供する。

【解決手段】単結晶シリコン基板上にGe濃度を上げながら組成傾斜SiGe層(Si1−xGex層のGe濃度比xが0<x≦0.5)を厚さ0.1〜3μmにエピタキシャル形成し、その上に厚さ0.1〜1μmのGe組成比が一定である歪み緩和Si1−xGex層を形成し、更に、厚さ5〜30nmの第1歪みSi層を形成し、その上に第2歪みSi層として、第1歪みSi層の成膜温度より低い温度で厚さ10nm以下の歪みSi層をエピタキシャル成長させる。

(もっと読む)

基板処理装置及び半導体デバイスの製造方法

本発明は、Ge含有ガスを供給してEpi−SiGe等の成膜処理をする場合に、基板界面の酸素濃度上昇を抑え、良好な膜を形成することができる基板処理装置を提供することを課題としている。

基板に成膜処理をする際に、ステップS18においてEpi−SiGe成膜処理を行う前に、ステップS13においてSiコーティング処理を行う。 これにより基板支持体に付着したGeO等の酸化物をコーティングで封じ込めることができ、GeOから脱離した酸素がEpi−SiGe膜のSi基板との界面に取り込まれるのを防止することができる。  (もっと読む)

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】 ヘテロエピタキシャル成長膜の、応力の緩和と、緩和に伴って発生し表面へ貫通する結晶欠陥の密度の抑制を両立させるために要求される、膜厚に対する制限を低減し、プロセス設計の自由度を向上させる。

【解決手段】 単結晶半導体基板10の上に単結晶半導体基板10とは格子定数及び/又は熱膨張率が異なる第1単結晶半導体層12を成長させた後に、水素を含む還元性雰囲気中で熱処理することにより、第1単結晶半導体層12の表面は平坦化され、結晶欠陥は単結晶半導体基板10との界面近傍の領域14に局在化され、表面近傍の領域16に加わる応力は緩和される。この熱処理工程の後に実施される第2成長工程において、下地となる第1単結晶半導体層12はその応力が緩和されているので、第1単結晶半導体層12とは格子定数及び/又は熱膨張率が異なる第2単結晶半導体層18に応力が加わり、良質な歪み半導体基板を得ることができる。

(もっと読む)

気体の下流解離化のための方法及び装置

気体を活性化し解離する方法及び装置であって、チャンバの中のプラズマを用いて活性化気体を発生するステップを含む。下流気体入力をチャンバの出力に対して配置することにより、気体入力によって導かれる下流気体の解離を容易化し、解離された下流気体がチャンバの内側表面と実質的に相互作用しないようにする。  (もっと読む)

(もっと読む)

交互ガス供給による選択的エピタキシープロセス

一実施形態において、基板表面上にシリコン含有材料をエピタキシャル形成する方法であって、単結晶表面及び第2表面(アモルファス又は多結晶)を有する基板をプロセスチャンバー内に位置させるステップと、基板を、堆積ガスに露出されて、単結晶表面にエピタキシャル層を形成すると共に、第2表面に多結晶層を形成するステップとを備えた方法が提供される。堆積ガスは、シリコンソースと、少なくとも第2の元素ソース、例えば、ゲルマニウムソース、炭素ソース又はその両方とを含むのが好ましい。その後、この方法は、更に、基板をエッチング剤ガスに露出させて、多結晶層がエピタキシャル層より速い速度でエッチングされるようにするステップも備えている。基板は、堆積ガス及びエッチング剤ガスに順次に繰り返し露出されて、シリコン含有材料を形成する。一実施例において、堆積ガスはシランを含み、エッチング剤ガスは塩素及び窒素を含む。 (もっと読む)

シリコンエピタキシャル膜形成時のCl2および/またはHClの使用

第1の態様では、基板にエピタキシャル膜を形成するための第1の方法が提供される。該第1の方法は(a)基板を提供するステップと、(b)該基板の少なくとも一部にエピタキシャル膜を形成するために少なくともシリコンソースに該基板を暴露するステップと、(c)ステップ(b)中に形成された該エピタキシャル膜および他の膜をエッチングするためにHClおよびCl2に該基板を暴露するステップとを含む。多数の他の態様が提供される。 (もっと読む)

直接ウェハ結合による低欠陥のゲルマニウム膜の製造

【課題】絶縁体またはシリコン基板上に低欠陥のゲルマニウム膜を製造する方法を提供する。

【解決手段】本発明による方法は、シリコンウェハを準備すること、二つの工程のCVDプロセスを用いてゲルマニウム膜を形成すること、多重サイクルプロセスを用いてゲルマニウム薄膜をアニーリングすること、水素イオンを注入することと、テトラエトキシシラン酸化物(TEOS)層を堆積かつ滑らかにすること、カウンタウェハを準備することと、ゲルマニウム薄膜をカウンタウェハに結合して結合構造を形成すること、少なくとも375℃の温度で結合構造をアニーリングして結合ウェハのスプリットを助長すること、結合構造をスプリットしてゲルマニウム薄膜を露出すること、ゲルマニウム薄膜の表面からゲルマニウム薄膜の欠陥区域部分とともに残留するシリコンを除去すること、および所望の最終デバイス内に低欠陥のゲルマニウム薄膜を組み込むことを含む。

(もっと読む)

拡散器重力支持体

【課題】熱と重力でガス分配プレートが変形する事を防ぐガス分配プレートを提供する。

【解決手段】少なくとも1つの支持部材15は、拡散器20を通る1つ以上ののガスの流れを妨げることのない噛み合い接続によって拡散器20と係合し、かつ拡散器から外すができ、また、その周辺を支持された拡散器20を垂直方向に吊り下げるように設計され、あるいは周辺支持体を備えることなく、拡散器を支持することができる。1つの態様においては、少なくとも1つの支持部材15は、ガス供給導管の一部分であり、拡散器の中央領域を垂直方向に並進させて持ち上げ、あるいは垂直方向に圧縮することができる。

(もっと読む)

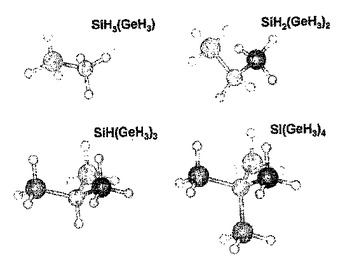

基板上でのSi−Ge半導体材料およびデバイスの成長方法

Geリッチな含有率(Ge>50原子%)および正確な化学量論的SiGe、SiGe2、SiGe3およびSiGe4を有するSi−Ge材料をSi(100)上に成長させる方法が提供される。化合物(H3Ge)xSiH4−x(x=1〜4)の群から得られる直接Si−Ge結合を有する新たな水素化物を用いて、約300〜450℃という前例のない低温で、欠陥密度の低い均一でリレーされた(relayed)高度に平面状の膜を成長させることで、厚い組成勾配のある緩衝層およびリフトオフ法を用いる必要が全くなくなる。約500〜700℃では、SiGex量子ドットが、狭い径分布、無欠陥微細構造および原子レベルで高度に均質な元素含有率にて成長する。その方法は、気体前駆体の全Si/Ge骨格の膜への組み込みを介して、形態、組成、構造および歪みの正確な制御を提供するものである。成長した材料は、高周波数電子および光学システム、ならびに高移動度SiおよびGeチャネルに基づく商業的デバイスの開発のための鋳型および緩衝層での利用に必要な形態的および微細構造的特徴を有している。  (もっと読む)

(もっと読む)

成膜装置、プラズマCVD装置、成膜方法及びスパッタ装置

【課題】 形成する膜の物性を容易に制御でき、また、生産性良く膜の形成が可能な制御性の良い成膜装置を提供する。

【解決手段】 膜を形成すべき基板5をアノード電極3に載置し、反応室1中に原料ガスを供給し、前記アノード電極3と、該アノード電極3に対向して配置してあるカソード電極4との間に高周波電圧を印加して原料ガスのプラズマを発生させ、制御部9を用いて駆動部8を制御することによって、成膜中にカソード電極4をアノード電極3に接近又は離隔させる。

(もっと読む)

ゲルマニウム基板タイプ材料およびその手法

ゲルマニウム回路タイプの構造が促進される。一実施形態例では、多段階の成長およびアニール・プロセスを実施して、ヘテロエピタキシャルル・ゲルマニウムなどのゲルマニウム(Ge)含有材料を、シリコン(Si)またはシリコン含有材料を含む基板上に成長させる。いくつかの応用例では、ゲルマニウム含有材料の上面に向かって貫通する欠陥が全体的に抑制されて、欠陥が全体的にシリコン/ゲルマニウム境界面付近に閉じ込められる。これらの手法は、ゲルマニウムMOSコンデンサ、pMOSFET、およびオプトエレクトロニック・デバイスを含む、さまざまなデバイスに適用できる。  (もっと読む)

(もっと読む)

SiとGeを含有する膜の堆積方法

【課題】SiGe膜を堆積させる効率的な方法を提供すること。

【解決手段】本発明は、プロセス室(2)内において少なくとも1つの半導体膜を少なくとも1つの基板上に堆積し、半導体膜が複数の成分からなり、成分が、個々のインジェクションユニット(5)を介して液体の又は液体に溶解した原料(3)が不連続に吐出されることによって、温度制御された蒸発室(4)内で蒸発され、この蒸気がキャリアガス(7)によってプロセス室に導入される、膜の堆積方法に関する。Siを含有する第1の原料とGeを含有する第2の原料(3)の流量の時間経過が、インジェクション圧、インジェクション周波数、及び、1つ以上の他のインジェクションユニットのデューティ比に対するデューティ比の位相関係等のデューティ比パラメータ等の、割り当てられたインジェクションユニット(5)が決定する流量パラメータを介して、個々に制御又は変化される。

(もっと読む)

エピタキシャル層を形成する方法および装置

本発明は、シリコン基材上にIV族元素をベースとするエピタキシャル層を化学蒸着により堆積させる方法であって、キャリヤーガスとして窒素または希ガスの一種を使用する、方法を提供する。本発明はさらに、ガス入口(14)およびガス出口(16)を有するチャンバー(12)と、チャンバー(12)の中にシリコン基材を取り付ける手段(18)とを備えてなる化学蒸着装置(10)を提供するが、該装置は、入口に接続され、なおかつキャリヤーガスとして窒素または希ガスを供給するように配置されたガス供給源を包含する。  (もっと読む)

(もっと読む)

UV線を用いたシリコン含有膜の低温エピタキシャル成長

シリコン含有及び/又はゲルマニウム含有膜の一括的又は選択的エピタキシャル堆積の清浄な基板表面を調製する方法。更に、シリコン含有及び/又はゲルマニウム含有膜を成長させる方法であって、基板洗浄方法と膜成長方法の双方が750℃未満、典型的には約700℃〜約500℃の温度で行われる前記方法。洗浄方法と膜成長方法は、シリコン含有膜が成長している処理容積において波長が約310nm〜約120nmの範囲にある放射線の使用を用いる。反応性洗浄又は膜形成成分化学種の具体的な分圧範囲と組み合わせたこの放射線の使用は、業界で以前に知られている温度より低い温度で基板洗浄とエピタキシャル膜成長を可能にする。 (もっと読む)

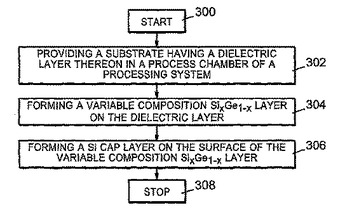

可変シリコン−ゲルマニウム組成を有するシリコンゲルマニウム薄層半導体構造および加工方法

誘電体層(410,510,610)、誘電体層(410,510,610)上の可変組成SixGe1-x層(440,520,620)、および可変組成SixGe1-x層(440,520,620)上のSiキャップ層(450,530,630)を持った基板(400,500,600)を含むSiGe薄層半導体構造である。可変組成SixGe1-x層(440,520,620)は、勾配を付けたGeを有するSixGe1-x層(520,620)、または、それぞれ異なったGe含有量(421,431)を有する複数のSixGe1-xサブ層(420,430)を含むことができる。本発明の一実施形態では、SiGe薄層半導体構造は、誘電体層(610)、誘電体層(610)上のSi含有シード層(615)、シード層(615)上の可変組成SixGe1-x層(620)、及び可変組成SixGe1-x層(620)上のSiキャップ層(630)を持つ半導体基板(600)を含む。SiGe薄層半導体構造を加工するための方法と処理ツール(1,100)も提供される。  (もっと読む)

(もっと読む)

141 - 160 / 167

[ Back to top ]