Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

2,201 - 2,220 / 2,474

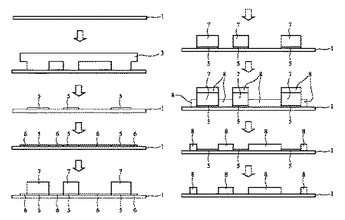

高解像度および低解像度にパターニングされた膜特徴部分をもつ大面積電子装置

【課題】大面積の電子装置の製造に利用できるパターニングされたIC用薄膜層の形成方法として、安価に大面積のパターンを形成できるパターニング技術と、小さな特徴パターンを形成できる微細パターニング技術と、を同時に実現する方法を提供する。

【解決手段】本発明は、装置の基板上にパターニングされた薄膜層を形成する方法であって、第1の処理ツールを用いて、前記装置基板上に比較的高解像度の第1構造を形成するステップ(ブロック110)と、第2の処理ツールを用いて、前記装置基板上に、前記第1構造と接続されるように、比較的低解像度の第2構造を形成するステップ(ブロック120)と、を含む方法であることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】ゲート電極や配線を低抵抗な金属膜を用いて形成することにより、大面積なデバイスにも対応できる半導体装置の作製方法を提供する。

【解決手段】基板上にアルミニウムを主成分とする第1の導電層を形成し、前記第1の導電層上に当該第1の導電層と異なる材料からなる第2の導電層を形成し、前記第1の導電層及び前記第2の導電層をパターニングしてゲート電極を形成することを特徴とする。また、前記第1の導電層は、炭素と、クロム、タンタル、タングステン、モリブデン、チタン、シリコン、ニッケルのいずれか一又は複数を含有していることを特徴とする。前記第2の導電層は、クロム、タンタル、タングステン、モリブデン、チタン、ニッケルまたはこれらの窒化物のいずれか一又は複数からなることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】好適な形状の配線を有する半導体装置を提供することを課題とする。

【解決手段】素子と接続される第1の導電層と、その上の第2の導電層とを形成し、第2の導電層上にレジストのマスクを形成し、マスクを用いたドライエッチングによって第2の導電層を加工し、マスクを残したままウエットエッチングによって第1の導電層を加工する配線の作製方法であって、ドライエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレートより大きく、ウエットエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレート以上とする。

(もっと読む)

横型バイポーラトランジスタ

【課題】 この発明は、SOI基板上に形成するうえで好適な構造を有する横型バイポーラトランジスタに関し、MOSプロセスの流用による形成を可能とし、かつ、十分なコレクタ電流を確保することを目的とする。

【解決手段】 埋め込み酸化膜11を有するSOI基板上に、複数のベース・エミッタ領域を形成する。個々のベース・エミッタ領域には、ベース引き出しP+拡散層(例えば14A)と、エミッタN+拡散層(例えば15A,15B)を含ませる。隣接するベース・エミッタ領域の間にコレクタN+拡散層16を配置する。各拡散層の間を埋めるように低濃度のP型ウェル拡散層(例えば12B,12C)を配置する。全てのベース引き出しP+拡散層14A〜14Eをベースコンタクト8に接続し、全てのエミッタN+拡散層15A〜15Iをエミッタコンタクト9に接続する。

(もっと読む)

表面のパターン処理および制御された析出成長物を用いたビアの製造

本発明は、表面のパターン処理の方法、および制御された析出成長物を用いたビアの製造、ならびにそのような本発明による方法によって調製されたパターン化された基板に関する。本発明による方法は、上部に材料をパターン化する必要のある、少なくとも一つの表面を有する基板を提供するステップであって、前記表面は、異なる表面特性を有する少なくとも第1および第2の表面領域を有し、前記第1の領域には、さらに保護析出成長物が設置されるステップと、少なくとも前記第2の表面領域に、少なくとも一つの材料を設置するステップであって、前記設置された材料は、前記第1の表面領域には実質的に設置されないか、前記第1の表面領域に設置される場合、前記設置された材料は、前記第1の表面領域から選択的に除去されるステップと、を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 非晶質化のためのイオン注入の際に影のできやすい溝やテーパ状シリコン突出体の表面を均一に非晶質化する方法を提供することを主要な目的とする。

【解決手段】 シリサイド前の非晶質化イオン107の注入の角度(チルト角θ、ツイスト角)に制限を設け、非晶質化のためのイオン注入の際に影のできやすい溝402の表面を均一に非晶質化する。その後シリサイド化することにより、フィールド領域内のシリコン表面を使った局所配線を形成し、隣り合うトランジスタのソースまたはドレインを局所的に接続する。

(もっと読む)

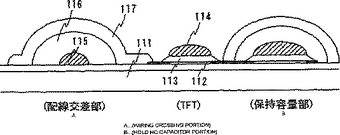

半導体装置およびその作製方法

島状の層間絶縁膜をソース線とゲート線が交差する領域に選択的に形成する。例えば、インクジェット法を用いて絶縁材料を含む液体をゲート線とソース線が交差する領域若しくは保持容量が形成される領域に滴下することにより、フォトリソグラフィー工程を削減し、TFT作製プロセス中において使用するマスク枚数を減らすことが可能となる。  (もっと読む)

(もっと読む)

薄膜半導体装置および液晶パネル

【課題】チャネル領域およびその近傍への迷光の入射を防ぐことが可能で光リーク電流の少ない薄膜トランジスタを有する薄膜半導体装置を提供する。

【解決手段】基板3上に設けられた配線パターン5と、配線パターン5を覆う層間絶縁膜7と、層間絶縁膜7上に設けられた半導体層9と、ゲート絶縁膜11を介して半導体層9上を横切る状態で設けられ層間絶縁膜7に形成された接続孔7aを介して配線パターン5に接続されたゲート電極13とを備えた薄膜半導体装置1において、ゲート電極13は、ゲート電極13が上部に重ねて配置された半導体層9のチャネル領域9aを挟んだ両側において、接続孔7aを介して配線パターン5に接続されている。

(もっと読む)

共通ゲートを備える相補型金属酸化物半導体薄膜トランジスタ、それを備える論理素子及びそのトランジスタの製造方法

【課題】共通ゲートを備える相補型金属酸化物半導体トランジスタ、それを備える論理素子及びそのトランジスタの製造方法を提供することである。

【解決手段】ベース基板及びベース基板上に備えられた所定形態のシリコン層を備えるが、シリコン層にP−チャンネルトランジスタ、及びそれと交差しつつ、ゲートを共有するN−チャンネルトランジスタが形成されており、P−チャンネル及びN−チャンネルトランジスタのうち、選択されたいずれか1つのソース及びドレイン表面にショットキー障壁誘発物質層が形成されたことを特徴とするCMOS薄膜トランジスタである。

(もっと読む)

ショットキー障壁貫通単電子トランジスタ及びその製造方法

【課題】PADOXのような工程を用いず、トンネル障壁の高さ及び幅を人為的に調節することができる上、電流駆動能力をさらに向上させることができるショットキー障壁貫通単電子トランジスタ及びその製造方法の提供。

【解決手段】ショットキー障壁貫通単電子トランジスタは、基板100上に形成された絶縁層110と、ソース/ドレイン領域120a/120bの少なくとも一部分はシリサイド化されてチャネル領域120bとショットキー接合される。また、ゲート絶縁膜130、ゲート電極140、側壁絶縁膜150、層間絶縁膜パターン160、及び露出した前記ゲート電極140及び前記ソース/ドレイン電極120a/120b上に形成された金属配線170を備える。

(もっと読む)

電子回路基板とその製造方法及び電子回路基板を用いた表示装置

【課題】繰り返し折り曲げても断線不良の起きない、接続信頼性が高いフレキシブル基板及びその製造方法、さらにその基板を用いた表示装置を提供する。

【解決手段】フレキシブル性を有するデバイスであって、基板に形成される金属配線12の少なくとも一部が導電性高分子により覆われている。具体的には、基板11上に金属の配線12を形成し、その配線上を覆うように導電性高分子の配線13を形成し、金属配線12と導電性高分子配線13とを多層構造にする。

(もっと読む)

有機薄膜トランジスタの製造方法、有機薄膜トランジスタ及び表示素子

【課題】工程の単純化およびコストの節減を図るとともに、電荷移動度および電流点滅比の高い有機薄膜トランジスタを製造することが可能な有機薄膜トランジスタの製造方法を提供する。

【解決手段】基板1、ゲート電極3、ゲート絶縁膜5、ソース/ドレイン電極7および有機半導体層9が順次形成された有機薄膜トランジスタ10を製造する方法であって、ソース/ドレイン電極7が形成されたゲート絶縁膜5の表面を、HI、HBr、HCl、HF、HNO3、H3PO4、H2SO4、またはこれらの混合物である無機酸または有機酸に含浸させ、焼き鈍しする。

(もっと読む)

有機電子デバイス、及び有機電子デバイス作成方法

【課題】 フォトリソプロセスを用いないIJプロセスによって正確な有機体材料液滴の着弾性を実現し、低温プロセスによる有機電子デバイスを提供する。

【解決手段】 電子デバイスを構成する一部もしくは全ての有機材料を、液滴に電荷付与することが可能なインクジェット法で吐出し、着弾させる電子デバイスに光反応電荷誘起層を設け、光によって発生した液滴とは逆の電荷部分に液滴を誘引着滴させる。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 高誘電率絶縁膜を用いて、閾値電圧の変動を低減することのできる半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板5の上に形成されたゲート絶縁膜9は、高誘電率絶縁膜を含む絶縁膜である。MOSFETのうちで、ゲート長およびゲート絶縁膜が同一であるものは、チャネル幅がWである単一のチャネルまたはチャネル幅がWであるチャネルを複数並列した構造を有する。また、チャネル幅の異なるMOSFETの素子分離領域6の端部における曲率が異なる。この場合、素子分離領域6の表面は実質的に同一面をなし、且つ、素子分離領域6の表面から底面までの深さが異なっていることが好ましい。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗性及び信頼性を同時に確保する。

【解決手段】基板110、該基板上に形成されゲート電極124を備えるゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜上に形成されているソース電極173を備えるデータ線及びソース電極と対向しているドレイン電極175、データ線及びドレイン電極上に形成されている保護膜180、及びドレイン電極と接続されている画素電極190を備える。ゲート絶縁膜及び保護膜の少なくとも一方の下部にケイ素を含むカバー層801、803を備えている。これにより、接着性が向上し、配線抵抗を低減することができる。

(もっと読む)

表示装置用配線、該配線を有する薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗特性及び信頼性を同時に確保する。

【解決手段】導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する表示装置用配線と、基板110、該基板110上に形成されているゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜140上に形成されているソース電極173を含むデータ線171及びソース電極173と対向しているドレイン電極175、及びドレイン電極175と接続されている画素電極190を有している。ゲート線とデータ線171及びドレイン電極175の少なくとも一方とは、導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する。これにより、配線の密着性が向上するので剥離を防止することができ、信頼性が向上する。

(もっと読む)

薄膜トランジスタ、その製造方法、これを有する表示装置、及び表示装置の製造方法

【課題】特性が向上した薄膜トランジスタの製造方法、これを有する表示装置、及び表示装置の製造方法を提供する。

【解決手段】薄膜トランジスタ100は、基板105上にゲート電極110、ゲート絶縁膜115、半導体パターン122及び半導体パターン上に相互離隔する第1及び第2導電性接合パターン127a,127b、第1バリヤーパターン131,141、ソース,ドレインパターン133,143、及び第1,第2キャッピングパターン135,145が形成されたソース,ドレイン電極130,140を含む。第1及び第2導電性接合パターン127a,127bが垂直なプロファイルを有するように形成する。

(もっと読む)

電界効果型トランジスタ

【課題】 ソース、ドレイン、ゲート電極、有機半導体層などを形成する場合に印刷法、インクジェット法などの簡便な方法によって形成しても、ON/OFF比が良好な素子を実現する。また、短チャネルを実現することにより、動作電流が大きく、且つ素子間の特性のばらつきの少ない有機材料を用いた電界効果トランジスタを安価に提供する。

【解決手段】 少なくとも支持基板、ソース電極、ドレイン電極、活性層、絶縁層、ゲート電極からなり、ソース電極およびドレイン電極が同一平面内に形成され、前記ソース電極、ドレイン電極に隣接して隔壁が設けられてなる間の幅が少なくとも前記活性層にて電気的に接続されてなる活性層として有機物を用いた電界効果型トランジスタ素子において、前記の隔壁の高さがソース−ドレイン間とその他の箇所において、高さが異なる。

(もっと読む)

薄膜トランジスタ、その製造方法及び薄膜トランジスタを備えた平板表示装置

【課題】薄膜トランジスタ、その製造方法及び薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】ゲート電極と、ゲート電極と絶縁されたソース及びドレイン電極と、ゲート電極と絶縁され、ソース及びドレイン電極にそれぞれ接する有機半導体層と、ソース及びドレイン電極及び有機半導体層とゲート電極とを絶縁させる絶縁層と、ゲート電極と連結された第1配線と、ソース及びドレイン電極の何れか一つと連結された第2配線と、を備え、ゲート電極、第1配線、ソース及びドレイン電極、及び、第2配線のうち、少なくとも何れか一つが、導電性ナノ粒子及び硬化性樹脂の硬化物を含む薄膜トランジスタである。また、その製造方法及び薄膜トランジスタを備えた平板表示装置である。これにより、薄膜トランジスタのうち導電性膜は、精密なパターンを有し、低コストの低温工程で製造されうる。

(もっと読む)

2,201 - 2,220 / 2,474

[ Back to top ]