Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

2,401 - 2,420 / 2,474

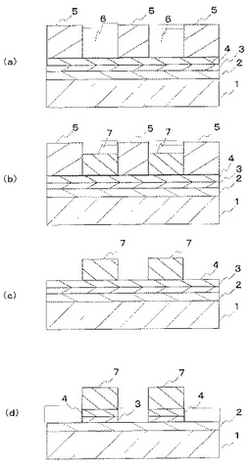

配線層の形成方法、配線層および薄膜トランジスタ

【課題】 配線膜厚が200〜1000nm程度のサブμmオーダの薄膜でも2.5μΩcm以下の比抵抗を得ること配線層の形成方法および配線層を提供すること。

【解決手段】 ガラス基板1上に下地絶縁膜2の窒化シリコン膜を形成し、この上に下地金属層3を形成し、この上に金属シード層4を形成し、この金属シード層4上に金属配線層7を形成した配線層であって、上記金属シード層4は主として結晶面が(111)に配向し、平均結晶粒径が0.25μm以上であり、上記金属配線層は膜厚が200乃至1000nmであり、無電解めっき法で形成された層である。

(もっと読む)

積層構造体、積層構造体を用いた光学素子、表示素子、演算素子及びこれらの製造方法

【課題】 印刷法のような低コストかつ材料使用効率の高い方法が適用でき、簡便に微細なパターンの形成が可能で、かつ、パターン形成以外に高付加価値機能を有する積層構造体を提供する。

【解決手段】 少なくとも第一の導電性材料7上に、絶縁性材料層2が積層され、その上に第二の導電性材料5が積層されている積層構造体1において、記絶縁性材料層2が、絶縁機能とエネルギーの付与によって臨界表面張力が変化する機能とを有する絶縁性濡れ変化層で構成され、第二の導電性材料5が絶縁性濡れ変化層の高表面エネルギー部3の部位に形成した。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた平板表示装置及びその平板表示装置の製造方法

【課題】 薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた平板表示装置及びその平板表示装置の製造方法を提供する。

【解決手段】 チャンネル領域、ソース、及びドレイン領域を有する活性層と、前記チャンネル領域に信号を印加するゲート電極と、前記ソース及びドレイン領域にそれぞれ接続し、Ti、Ti合金、Ta、及びTa合金のうち少なくとも一つを含むソース及びドレイン電極と、前記ソース及びドレイン電極と前記活性層との間に介在され、シリコンナイトライドを含む絶縁膜と、を含むことを特徴とする薄膜トランジスタ。これにより、ソース/ドレイン電極の配線抵抗を低め、活性層からの汚染を防止し、画素電極との接触抵抗特性が改善され、活性層への水素供給を円滑にして移動度、オンカレント特性、スレショルド電圧特性などに優れたTFT及びそれを備えた平板表示装置が得られる。

(もっと読む)

配線形成方法

【課題】 液滴吐出法を用いてゲート配線あるいはゲート配線と同一工程で形成される配線を形成しかつ絶縁膜を薄膜化した場合における絶縁不良を防止する。

【解決手段】 薄膜トランジスタ30の少なくともゲート電極41を兼ねるゲート配線40の形成方法であって、上記ゲート配線40の構成材料を含む液体材料を液滴として吐出する液滴吐出法を用いることによって、上記ゲート配線40の一部41を他の上記ゲート配線40の部分よりも薄く形成する。

(もっと読む)

トランジスタ構造及びその製作方法

トランジスタ構造の少なくとも一部分が実質的に透明であるエンハンスメント・モード電界効果トランジスタである。該トランジスタの一変形形態は、ZnO、SnO2及びIn2O3から選択された実質的に絶縁性で実質的に透明な材料から構成されるチャネル層を含む。実質的に透明な材料から構成されるゲート絶縁体層は、チャネル層/ゲート絶縁体層境界面を形成するようにチャネル層に隣接して配置される。該トランジスタの第2の変形形態は、アニーリングにより生成される実質的に絶縁性のZnO、SnO2及びIn2O3から選択される実質的に透明な材料から構成されるチャネル層を含む。該トランジスタを含む装置、及び該トランジスタを作る方法も開示されている。  (もっと読む)

(もっと読む)

太陽電池及び太陽電池の製造方法

【課題】

所定の電磁気的特性や耐腐食性を保持しながら、太陽電池のレーザスクライブ工程に対応可能な裏面電極を有する太陽電池及び太陽電池の製造方法を提供する。

【解決手段】

基板2と、基板2上に設けられ互いに直列に接続された複数の発電セル11とを具備する太陽電池を用いる。発電セル11は、基板2上の表面電極層3と、光により発電する表面電極層3上の光発電層5と、発電層5上の裏面電極層9とを備える。裏面電極層9は、銀を含む第1裏面電極層7と、第1裏面電極層7の腐食を抑制する第1裏面電極層7上の第2裏面電極層8とを含む。隣り合う発電セル11の間に、第2裏面電極層8の表面から表面電極層3へ延びる分離溝10を有する。裏面電極層9は、所定の電気的特性を満たす。分離溝10を記基板側がら照射したレーザで形成するとき、表面電極層3へ影響を与えずに、位置の光発電層5と裏面電極層9とをレーザで除去可能とする膜厚を有する。

(もっと読む)

トランジスタの製造方法、電気光学装置の製造方法、および電子デバイスの製造方法

【課題】 チャネル長の短い薄膜トランジスタを簡便に、かつ、低廉なコストで形成することができる薄膜トランジスタの製造方法を提供する。

【解決手段】 液滴乾燥法を用いることによってバンク30を形成し、このバンク30を挟んでソース電極40aとドレイン電極40bを形成する。その後、バンク30を剥離することによって得られる溝パターン50に半導体材料を供給して半導体層を形成し、ゲート絶縁膜、ゲート電極等を形成することにより、薄膜トランジスタを製造する。

(もっと読む)

薄膜トランジスタの製造方法、半導体装置、電気光学装置及び電子機器

【課題】 1度の不純物注入工程によってLDD構造を形成することができる薄膜トランジスタの製造方法等を提供する。

【解決手段】 本発明は、ゲート絶縁膜上に、チャネル長方向において端部から中央部に向けて徐々に膜厚が厚くなる傾斜部を有するゲート電極20を形成する工程を含む薄膜トランジスタうの製造方法を提供する。該ゲート電極20をマスクとしてリンなどの不純物元素のイオン打ち込みを行うことで、最終的には図3(B)に示すようなソース/ドレイン領域としての高濃度のN+型不純物拡散領域22a、低濃度のN-型不純物拡散領域22b、及びチャネル領域24が形成される。

(もっと読む)

ショットキー素子及びその形成方法

導電層(41)は第1部分を含み、第1部分は下層の第1導電型の第1領域とともにショットキー領域(25)を構成する。第2導電型の第2領域(11)は第1領域(22)の下に設けられ、第2導電型は第1導電型とは逆の導電型である。第1導電型の第3領域(21)は第2領域(11)の直下に位置し、かつ素子のカソード(52)に電気的に接続される。  (もっと読む)

(もっと読む)

導電性有機ポリマー/ナノ粒子複合材料およびその使用方法

導電性有機ポリマーと複数のナノ粒子との水性分散液を含んでなる組成物が提供される。発明組成物からキャストされるフィルムは、有機発光ダイオード(OLED)のようなエレクトロルミネセンスデバイスおよび薄膜電界効果トランジスタ用電極での緩衝層として有用である。ナノ粒子を含有する緩衝層は、ナノ粒子なしの緩衝層よりもはるかに低い導電率を有する。さらに、エレクトロルミネセンス(EL)デバイス中へ組み込まれた場合に、本発明による緩衝層はELデバイスのより高い応力寿命に寄与する。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】 高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】 ゲート電極106と異なる層に走査線102を形成し、容量配線107が信号線109と平行になるよう配置する。各画素はそれぞれ独立した容量配線107に誘電体を介して接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

薄膜トランジスタ、表示装置及びそれらの作製方法、並びにテレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等の構成物を、密着性よく形成できる技術を提供することも目的とする。

【解決手段】 本発明は、薄膜トランジスタ又は表示装置などを構成する構成物を、それらの被形成物表面を形成する物質のうち、少なくとも一つと同じ物質を添加(混入)して形成することによって、構成物と被形成物との密着性を向上させる。また、構成物上に形成される絶縁層において、構成物表面に生じる凹凸形状を十分に被覆し、かつ絶縁層として信頼性に足るように緻密化できるように、絶縁層を有機材料を含む第1の絶縁層と、無機材料を含む第2の絶縁層とを積層して形成する。

(もっと読む)

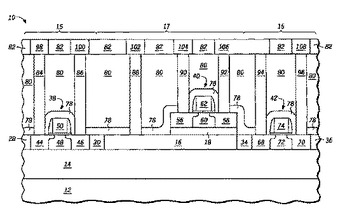

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置において、セル面積の縮小化を図ることにある。

【解決手段】 半導体装置100は、半導体基板10と、半導体基板10の内部に形成され、コントロールゲートとして機能する不純物領域22と、半導体基板10の上方に形成されたゲート絶縁層16と、ゲート絶縁層16の上方に、不純物領域22とオーバーラップして形成されたフローティングゲート18と、フローティングゲート18の上方に形成された層間絶縁層50と、層間絶縁層50の上方に、フローティングゲート18とオーバーラップして形成された遮光層52と、を含む。遮光層52は、不純物領域22と電気的に接続している。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

半導体装置および電子機器

【課題】 半導体集積回路において、今後のさらなるゲート電極の微細化を進める技術を提供することを課題とする。

【解決手段】 本発明は、レジストマスクをエッチングにより後退させて導電膜のエッチングを行い、ゲート配線の断面形状は上層配線とコンタクト可能な幅を有する台形とし、且つ、ゲート配線から分岐するゲート電極の断面形状を意図的に3つの内角をもつ形状、代表的には三角形状として1μm以下のゲート幅を実現する。本発明により、オン電流の増大が実現し、高速動作する回路(代表的にはCMOS回路やNMOS回路)を得ることができる。

(もっと読む)

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

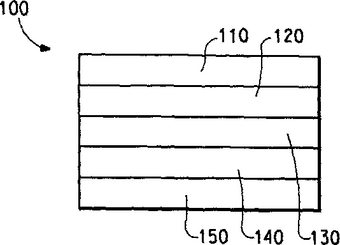

薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置

【課題】 ソース/ドレイン電極間の電気的疎通を円滑にすることが可能な,薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置を提供する。

【解決手段】 本発明に係る薄膜トランジスタは,基板110と,基板110上に形成されたゲート電極120と,ゲート電極120上に形成されるゲート絶縁層130と,ゲート電極120と絶縁されるようにゲート絶縁層130上に形成されるソース/ドレイン電極140a,140bと,ソース/ドレイン電極140a,140bと接するとともに,ゲート電極120と絶縁される有機半導体層150と,を含み,ソース/ドレイン電極140a,140bの少なくとも有機半導体層150と接する部分には酸化部140´a,140´bが設けられ,酸化部140´a,140´bを構成する物質は,有機半導体層150のHOMOエネルギー準位より大きい仕事関数を有する物質を含む。

(もっと読む)

2,401 - 2,420 / 2,474

[ Back to top ]