Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

2,361 - 2,380 / 2,474

半導体デバイスの形成方法およびその構造

一実施形態では、半導体デバイス(10)の形成方法が示される。半導体基板(11)は、第1の部分(14または16)および第2の部分(18または20)を有する。第1の誘電体層(24または26)は半導体基板の第1の部分の上に形成され、第2の誘電体層(30)は半導体基板の第2の部分の上に形成される。ポリシリコンなどのシリコンを含み得るキャップ(28)は第1の誘電体層の上に形成される。第1の電極層(40)はキャップの上に形成され、第2の電極層(32,36または40)は第2の誘電体の上に形成される。  (もっと読む)

(もっと読む)

表示装置

【課題】TFTと補助容量により各画素を駆動制御する表示装置において、電圧保持率を十分に維持しながら開口率を最大にすることができる表示装置を提供すること。

【解決手段】駆動回路基板118と、対向基板119と、これらの両基板の間に封止された液晶層112とを備え、駆動回路基板118には各画素に対応した駆動制御用の有機TFT117と補助容量部120とを有しており、有機TFT117のソース電極108、ドレイン電極109、ゲート電極104及び補助容量部120の補助容量電極103、特に補助容量電極103が透明導電材料で形成されることにより、開口率を最大にできる。

(もっと読む)

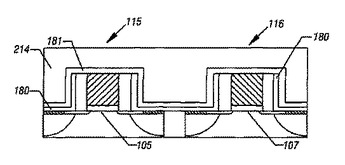

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

LCDのTFT基板及びその製造方法

【課題】 液晶表示装置の薄膜トランジスタ基板及びその製造方法が開示されている。

【解決手段】 シリコン元素を含む基板、前記基板上に形成された拡散防止膜、及び前記拡散防止膜上に形成され、前記拡散防止膜形成物質が0.5〜15at%範囲で含まれた銅合金層を含んで形成される。前記拡散防止膜は、Zr、Ti、Hf、V、Ta、Ni、Cr、Nb、Co、Mn、Mo、W、Rh、Pd、Pt等のような化合物を50〜5000Å範囲で蒸着して熱処理して、シリサイド化合物に変換して製造する。銅合金配線を用いてトランジスタ基板を製造するので、低い抵抗と高い伝導度を具現することができる。又、薄い厚さの拡散防止膜と同じ元素を添加した銅合金と用いて銅配線を形成したので、同時エッチングが可能であり、後続工程で基板との相互拡散を防止することができる。  (もっと読む)

(もっと読む)

サリサイド工程及びこれを利用した半導体素子の製造方法

【課題】サリサイド工程及びこれを利用した半導体素子の製造方法を提供する。

【解決手段】 本発明による金属シリサイド膜の形成方法は、シリコン領域を備える基板を準備する段階と、前記基板上にシリコン層を形成する段階と、前記シリコン層と接触する金属膜を形成する段階と、前記金属膜を有する基板を熱伝達気体を採択した対流または伝導方式を使用して等温熱処理して前記少なくとも前記金属膜の一部を金属シリサイド膜に転換する段階と、を含む。

(もっと読む)

液晶表示素子及びその製造方法

【課題】薄膜トランジスタの製造に使用されるマスクの数を減少させる液 晶表示素子及びその製造方法を提供する。

【解決手段】第1基板上にソース領域とドレイン領域及びチャンネル領域を有したアクティブ層を形成し、その上に第1絶縁膜を形成する段階と、第1絶縁膜上に第1導電膜と第2導電膜を形成、パターニングしてゲート電極とゲートライン及び画素電極を形成する段階と、この上に第2絶縁膜を形成し、前記第1絶縁膜と第2絶縁膜のソース/ドレイン部にコンタクトホールを形成して、前記画素電極の上部の第2絶縁膜を除去する段階と、その上に第3導電膜を形成パターニングして前記コンタクトホールを通じてソース/ドレイン領域と電気的に接続されるソース/ドレイン電極を形成し、前記画素電極の上部の第2導電膜を露出させる段階と、前記第1基板と第2基板間に液晶層を形成する段階とを含む。

(もっと読む)

ウェハ接合によって製造される半導体−誘電体−半導体デバイス構造体

【課題】 デバイス性能を犠牲にすることなく様々なゲート材料の使用を可能にする、半導体基板上に少なくとも部分的にゲート・スタックを作るための技術を提供する。

【解決手段】 高k誘電材料を含む少なくとも1つの構造体のウェハ接合を利用して、半導体電子デバイスのためのゲート・スタックを形成する方法が提供される。本発明の方法は、まず、それぞれが主面を有する第1及び第2の構造体を選択するステップを含む。本発明によれば、第1及び第2の構造体の少なくとも一方又は両方は、少なくとも高k誘電材料を含む。次に、第1及び第2の構造体の主面同士を接合して、ゲート・スタックの高k誘電材料を少なくとも含む接合構造体を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

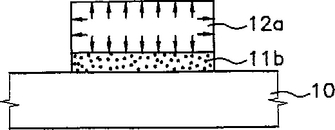

薄膜トランジスタの製造方法、電気光学装置、および電子機器

【課題】 本発明は、薄膜トランジスタに用いられるゲート電極や半導体膜を、簡易かつ安価な工程によってサブミクロンオーダーの精度で形成する技術を提供することを目的とする。

【解決手段】 本発明は、基板上に、半導体材料を含む液滴(14)を配置する工程と、液滴を乾燥させ、該液滴の少なくとも周縁部に半導体材料を析出させることによって、半導体膜(16)を形成する工程と、を含む半導体薄膜の形成方法、および/または、導電性材料を含む液滴を配置する工程と、液滴を乾燥させ、該液滴の少なくとも周縁部に導電性材料を析出させることによってゲート電極を形成する工程と、を含むゲート電極の形成方法を含む薄膜トランジスタの製造方法を提供する。

(もっと読む)

電界効果型トランジスタ

【課題】チャネル領域を構成する有機半導体材料層と良好なオーミック・コンタクトを形成することができるソース/ドレイン電極を備えた電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、ゲート電極12と、ゲート絶縁層13と、ソース/ドレイン電極21と、チャネル領域15を構成する有機半導体材料層14とを備え、ソース/ドレイン電極21は、金属から成る導体部22、及び、導体部22を少なくとも部分的に被覆し、不純物がドーピングされた有機導電材料層23から成り、有機導電材料層23を介して、チャネル領域15と導体部22との間の電気的接続が形成される。

(もっと読む)

有機機能素子、有機EL素子、有機半導体素子、有機TFT素子およびそれらの製造方法

【課題】 有機EL素子や有機TFT素子等の有機機能素子において、有機材料層への電極形成において蒸着を用いる必要が無く、また、折り曲げても断線しない信頼性の高い有機機能素子及びその製造方法を提供する。

【解決手段】 少なくとも複数の電極と有機材料層から構成される有機機能素子であって、該電極の少なくとも一つが液体金属で形成されている。

(もっと読む)

配線基板、薄膜トランジスタ、表示装置及びテレビジョン装置の作製方法

【課題】 本発明は、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置の作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】 本発明の配線基板の作製方法の一は、被処理物を有する第1の領域を形成し、一部の被処理物表面を改質して、第1の領域と境界線を有する第2の領域を形成し、境界線を越えて第1の領域の一部、及び第2の領域に連続的に導電性材料を含む組成物を吐出し、組成物を固化して導電層を形成し、境界線を越えて第1の領域の一部に形成された導電層を除去する。

(もっと読む)

有機半導体装置

【課題】 高移動度を有するN型有機トランジスタ、さらには電子をキャリヤとする高性能の有機半導体装置を実現するための電極を提供することを目的とする。

【解決手段】 有機半導体層40と、有機半導体層との電気的接点を構成する電極であって、該有機半導体への電子の注入効率を高めるため、該電極、又は有機半導体と接する側の電極の一部が、該有機半導体を構成する分子材料と同一又は類似のイオン化エネルギーを持つ電子受容性分子材料に、電子供与性分子材料を組み合わせることによって導電性電荷移動型錯体を形成した電極2、3とを少なくとも有する有機半導体装置によって解決される。

(もっと読む)

半導体デバイスのゲートのクリティカルディメンションを改善するためのゲート材料のプレーナ化

半導体デバイス(100)を製造する方法は、絶縁体(120)上にフィン構造(210)を形成するステップを含む。このフィン構造(210)は、側面および上面を含んでいてもよい。この方法はさらに、フィン構造(210)上にゲート材料(320)をたい積するステップと、たい積したゲート材料(320)をプレーナ化するステップを含んでいてもよい。反射防止膜(520)は、プレーナ化したゲート材料(320)上にたい積することができ、また、ゲート構造(510)は、反射防止膜(520)を使用して、プレーナ化したゲート材料(320)から形成することができる。  (もっと読む)

(もっと読む)

カーボンナノチューブトランジスタの製造方法

【課題】 カーボンナノチューブトランジスタの製造方法に関し、カーボンナノチューブトランジスタの製造歩留まりを向上させる。

【解決手段】 ソース部5、ドレイン部6、及び、ソース部5とドレイン部6との間の領域以外の領域上に堆積したカーボンナノチューブ9を除去する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 薄膜トランジスタ表示板の製造工程を簡素化する。また、画素電極の断線を防止できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】 本発明の一実施形態による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成する段階と、前記ゲート線上にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上に半導体層を形成する段階と、前記半導体層上にオーミック接触部材を形成する段階と、前記オーミック接触部材上にデータ線及びドレイン電極を形成する段階と、前記データ線及び前記ドレイン電極上に保護膜を蒸着する段階と、前記保護膜上に第1感光膜を形成する段階と、前記第1感光膜をマスクとして前記ゲート絶縁膜及び前記保護膜をエッチングすることによって、前記ドレイン電極の少なくとも一部と前記基板の少なくとも一部を露出させる段階と、導電体膜を蒸着する段階と、並びに前記第1感光膜を除去し、前記ドレイン電極の露出した部分上に画素電極を形成する段階とを含む。

(もっと読む)

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】 ゲート容量が小さく、短チャネル効果が抑制された薄膜トランジスタ(TFT)を作製する。またゲート配線の配線抵抗を減少させ、回路面積の減少とTFTの高速駆動を可能にする。

【解決手段】 ゲート電極を二層にし、下層の幅を上層よりも小さくすることにより、ゲート電極と半導体膜からなる活性層の重なる面積が小さくなる。これによりゲート容量を減少させ、短チャネル効果を抑制することができるので、TFTを高速駆動させることが可能である。また、ゲート電極と配線を一体形成せず別々に形成することによって、TFTによって構成される回路面積も縮小でき、高速化に寄与できる。

(もっと読む)

導電性インキ組成物、反射部材、回路基板、電子装置

【課題】 塗布対象物との密着性が、従来よりも改善された導電性インキ組成物を提供する。また、金属の粒成長を抑制し、表面平滑性に優れた膜を形成することができる導電性インキ組成物を提供する。

【解決手段】 少なくとも貴金属を含む合金からなる金属微粒子の表面を、少なくとも二種の有機化合物からなる保護コロイドで被覆されてなる固形物を有機溶媒に分散させて導電性インキ組成物とする。上記保護コロイドには、例えば、(A)アミン類と、(B)カルボン酸とを含む原料から得られる保護コロイドを使用する。上記導電性インキ組成物を塗布、焼成することで、粒成長が抑制され、表面平滑性に優れ、塗布対象物との密着性が従来よりも改善された金属膜を得ることができる。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

2,361 - 2,380 / 2,474

[ Back to top ]