Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

2,161 - 2,180 / 2,474

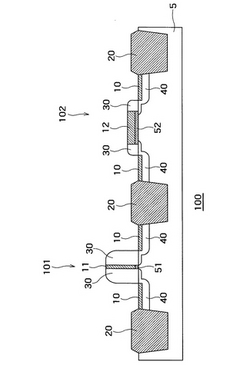

半導体装置および半導体装置の製造方法

【課題】 異なるゲート長またはゲート幅を有し、フルシリサイド化されたゲート電極を備えた半導体装置を提供する。

【解決手段】 半導体装置100は、半導体基板5と、半導体基板上に形成された第1のゲート絶縁膜51と、半導体基板上に形成された第2のゲート絶縁膜52と、第1のゲート絶縁膜上に形成され、フルシリサイド化された第1のゲート電極11と、第2のゲート絶縁膜上に形成され、フルシリサイド化された第2のゲート電極12であって、半導体基板の表面を占める面積が第1のゲート電極よりも大きく、なおかつ、第1のゲート電極よりも厚みが薄い第2のゲート電極12とを備えている。

(もっと読む)

表示装置用基板とその製造方法、及びこの表示装置用基板を用いた表示装置

【課題】 所要の膜厚で均一な膜厚の薄膜配線をインクジェット方式で形成した表示装置用基板を得る。

【解決手段】 基板に形成したゲート配線パターン80とゲート電極部パターン80aに倣って形成された溝4にインクジェット装置のノズルから配線材料インク3を滴下する。配線材料インク3は幅広部81の溝4に滴下する。配線材料インク3は未だ滴下した後の低粘度状態にあり、滴下された配線材料インク3は隣接するインク滴と連結すると共に、矢印で示したように、溝4の中をゲート配線パターン80では相互に連結し、かつゲート電極部パターン80aに漸次濡れ広がり、溝4の中を満たして連続した状態となる。溝4に滴下する配線材料インク3の量は、ゲート配線パターン80とゲート電極部パターン80aとなる薄膜の膜厚を満足する量になるように決める。

(もっと読む)

半導体装置を製造する方法

基板を用意する工程であって、この基板に形成される誘電体層と、この誘電体層に形成され金属含有ゲート電極層と、を有するゲートスタックを含む当該基板を用意する工程;プラズマ中でプロセスガスから低エネルギー励起ドーパント種を生成する工程;および、前記ゲートスタックにドーパントを取り込むため、前記ゲートスタックを前記励起ドーパント種に晒す工程;を含む、半導体装置の製造工程におけるゲートスタックを処理する方法。この方法は、ゲートスタックの仕事関数を調整するために利用することができる。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】 トランジスタを形成する際に、そのトランジスタの下方に形成されている膜が受ける熱的ダメージを低減することができる半導体装置とその製造方法を提供すること。

【解決手段】 第1絶縁膜37の上に遮蔽膜38を形成する工程と、遮蔽膜38の上に第2絶縁膜39と非晶質半導体膜40とを順に形成する工程と、非晶質半導体膜40にエネルギービームを照射し、少なくとも薄膜トランジスタのチャネルとなる部分の非晶質半導体膜40を溶融して多結晶半導体膜41にする工程と、上記チャネルの上の多結晶半導体膜41上にゲート絶縁膜43aとゲート電極44aとを順に形成する工程と、ゲート電極44aの横の多結晶半導体膜41にソース/ドレイン領域41aを形成し、該ソース/ドレイン領域41a、ゲート絶縁膜43a、及びゲート電極44aでTFT60を構成する工程と、を有する半導体装置の製造方法による。

(もっと読む)

デバイス性能を改善するためのデュアル・シリサイド・プロセス

【課題】 nFETデバイス及びpFETデバイスの両方に接触するための低減された抵抗率を有する半導体コンタクト構造体、及び、その形成方法を提供すること。

【解決手段】 半導体構造体及びその形成方法は、p型デバイス領域(20)及びn型デバイス領域(10)を有する基板と、n型デバイス領域(10)への第1型シリサイド・コンタクト(30)と、p型デバイス領域(20)への第2型シリサイド・コンタクト(35)と、を含み、第1シリサイドはn型デバイス領域の伝導帯と実質的に合わせられた仕事関数を有し、第2シリサイドはp型デバイス領域の価電子帯と実質的に合わせられた仕事関数を有する。本発明はまた、シリサイド・コンタクト材料及びシリサイド・コンタクト加工条件がpFETデバイス及びnFETデバイに歪みに基づくデバイスの改善を与えるように選択された、半導体構造体及びその形成方法を提供する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】二酸化シリコン換算膜厚が5nm未満の極薄ゲート絶縁膜上にメタルゲート電極を形成したMISFETにおいて、メタルゲート電極を酸化させることなくゲート絶縁膜の欠陥を修復する。

【解決手段】単結晶シリコン基板1の主面上に形成した二酸化シリコン換算膜厚が5nm未満のゲート絶縁膜9A上にゲート電極材料であるW膜11Aを形成した後、水分/水素分圧比がW膜11Aを実質的に酸化せず、シリコンを酸化するような割合に設定された水分+水素混合ガス雰囲気中でシリコン基板1を熱処理することにより、W膜11A直下のゲート絶縁膜9Aの欠陥を修復する。

(もっと読む)

CMOSプロセス用金属ゲート・トランジスタ及びその製造方法

半導体装置(100)を形成する方法は、第一領域(104)を備える半導体基板と、第一領域上にゲート誘電体(108)を形成するステップと、ゲート誘電体上に導電性金属酸化物(110)を形成するステップと、導電性金属酸化物上に耐酸化バリア層(111)を形成するステップと、耐酸化バリア層上にキャッピング層(116)を形成するステップとを含む。一実施形態において、導電性金属酸化物はIrO2,MoO2及びRuO2であり、耐酸化バリア層はTiNを含む。  (もっと読む)

(もっと読む)

ゲート誘電体上にゲート金属または他の導体材料または半導体材料を電着するための方法(ゲート誘電体貫通電流を用いた電気化学処理によるゲート・スタック技術)

【課題】 ゲート誘電体等の誘電体の上に直接ゲート金属または他の導体材料または半導体材料を電気めっきするための方法を提供する。

【解決手段】 この方法は、基板、誘電体の層、および電解液または溶融物を選択することを含み、基板、誘電体層、および電解液または溶融物の組み合わせによって、基板から誘電体層を介して電解液または溶融物へと電気化学電流を流すことができる。また、誘電体貫通電流を用いて誘電体の電気化学的な変更を行うための方法も提供する。

(もっと読む)

Al配線を備えた透明導電膜積層基板及びその製造方法。

【課題】 特定の金属を含有する透明導電材料を透明導電膜に使用することにより、Al配線を設けた積層基板の製造方法を簡略化する。

【解決手段】 透明基板と、前記透明基板上に設けられたAl配線と、酸化亜鉛を主成分とする導電性酸化物からなり、前記Al配線に直接接合する透明導電膜と、を含むことを特徴とするAl配線を備えた透明導電膜積層基板である。バリヤーメタルを間に設けず、直接Al配線と透明導電膜が直接接合しているので、製造工程を簡略化することができる。

(もっと読む)

半導体装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】粗面を有する層を形成し、粗面上に導電性材料を含む組成物に対するぬれ性の低い領域と、組成物に対するぬれ性の高い領域を形成し、ぬれ性の高い領域に前記組成物を用いて導電層を形成する。ぬれ性が大きく異なる領域(ぬれ性に大きく差を有する領域)を形成できるので、液状の導電性材料又は絶縁性材料が、被形成領域のみに正確に付着する。よって、所望のパターンに正確に導電層、絶縁層を形成することができる

(もっと読む)

細線状MOSFETを含む半導体装置

【課題】 簡単な構成を採ることで、細線状素子領域に於けるソース領域及びドレイン領域からチャネル領域に向かって機械的な応力を効率良く印加し、キャリヤ移動度を向上させようとする。

【解決手段】 細線状チャネル領域4を挟んで細線状ソース領域8及び細線状ドレイン領域9が配設された細線状素子領域と、細線状ソース領域8及び細線状ドレイン領域9それぞれの少なくとも側面を覆う圧縮或いは引張の応力を発生する応力発生膜11或いは12とを備える。

(もっと読む)

配線パターンを有する基板及びそれを用いた液晶表示装置

【課題】配線パターンを有する基板及びそれを用いた液晶表示装置において、配線パターンの多層金属構造を最適化し、インクジェット塗布等の液体プロセスにより主金属と副金属の配線パターンを形成することで、生産工程を簡素化する。

【解決手段】絶縁基板51上に形成した主金属のみのゲート電極11及び走査配線101と、これらの上に形成したゲート絶縁膜53と、このゲート絶縁膜上に形成した、走査配線と直交して主金属のみのソース電極12に接続する主金属のみのデータ配線201と、主金属のドレイン電極13と、ソース電極とドレイン電極とにそれぞれ接続する半導体層54,55と、このドレイン電極上に形成した副金属のキャップメタル67と、このキャップメタルとコンタクトホール59を介して接続する画素電極21とを備えた画素部300をマトリクス状に配置する。

(もっと読む)

複層構造のゲート電極を有する薄膜トランジスタ及びその製造方法

【課題】熱処理過程でのゲート電極下部のシリコン層の損傷を防止した薄膜トランジスタ及びその製造方法を提供する。

【解決手段】シリコン層22の両側をドーピングして形成されたソース28とドレイン29、シリコン層22の上面中心に部分的に形成された絶縁層25、及び絶縁層25上に形成されたゲート電極26を含む薄膜トランジスタにおいて、ゲート電極26は、耐熱性材料よりなる第1ゲート電極26aと第1ゲート電極26a上に形成され、光反射性金属よりなる第2ゲート電極26bで構成された複層構造の電極である。

(もっと読む)

CMOSFET内の歪みを最適化するための構造体及び方法

【課題】 CMOSFET内の歪みを最適化するための構造体及び方法を提供すること。

【解決手段】 MOSFET内の歪みを最適化し、より具体的には、1つの種類(P又はN)のMOSFET内の歪みを最大にし、かつ、別の種類(N又はP)のMOSFET内の歪みを最小にし緩和する、PMOSFET及びNMOSFETの両方を含む歪みMOSFETの半導体構造体、及び歪みMOSFETを製造する方法が開示される。元の完全な厚さを有する歪み誘起CA窒化物コーティングが、PMOSFET及びNMOSFETの両方の上に形成され、この歪み誘起コーティングは、1つの種類の半導体デバイス内に最適化された十分な歪みをもたらし、別の種類の半導体デバイスの性能を劣化させる。歪み誘起CA窒化物コーティングは、別の種類の半導体デバイスの上で減少した厚さまでエッチングされ、減少した厚さの歪み誘起コーティングは、他方のMOSFET内でより少ない歪みを緩和し、他方のMOSFET内により少ない歪みをもたらす。

(もっと読む)

半導体装置とその製造方法

【課題】

フィン型構造を持つ電界効果トランジスタのソース/ドレインのコンタクト抵抗を低減する。

【解決手段】

半導体装置の製造方法は、第1の高さのフィン型半導体領域うえに、第1の高さより高い第2の高さの絶縁ゲート電極構造を形成し、サイドウォール絶縁膜をフィン型半導体領域の側面からは完全に異方性エッチングで除去し、フィン型半導体領域近傍のゲート電極両側面ではフィン型半導体領域の上面、側面をサイドウォール絶縁膜が囲むように、ゲート電極両側面上下部を残して上部上からエッチング除去し、フィン型半導体領域の少なくとも露出している両側面に上端から下端までシリサイド層を形成する。層間絶縁膜形成後、フィン型半導体領域の両側面のシリサイド層を露出するコンタクトホールを形成し、導電性プラグを埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイド化されたゲート電極(フルシリサイドゲート電極)を有する半導体装置であっても、接合リーク電流増大の問題なく、ソースドレイン領域に形成された金属シリサイド膜の膜厚を厚く形成することが可能であり、かつ一回のシリサイド形成工程でフルシリサイドゲート電極及び金属シリサイド膜を形成可能な半導体装置及びその製造方法を提供する。

【解決手段】上主面が半導体基板1より高くなるように金属シリサイド膜11を形成する。金属シリサイド膜11と半導体基板1からなる界面Aと、ソースドレイン拡散層8と半導体基板1からなる界面Bとの距離が十分確保できるように、金属シリサイド膜11の膜厚を厚く形成できる。その結果、フルシリサイドゲート電極10を形成した場合であっても、接合リーク電流の増大を回避しつつ、金属シリサイド層11の膜厚を厚くできる。

(もっと読む)

有機電界効果トランジスタ及び半導体装置

【課題】導電層と半導体層との界面のエネルギー障壁を低減できる電極を有する有機電界効果トランジスタ及び有機電界効果トランジスタを有する半導体装置を提供することを課題とする。

【解決手段】有機電界効果トランジスタ用の電極、すなわち有機電界効果トランジスタにおけるソース電極及びドレイン電極の少なくとも一方の一部に、有機化合物と金属酸化物とを含む複合層を用いる。または、さらにアルカリ金属等を含む層を設けた電極とする。

(もっと読む)

薄膜トランジスタ及びこれを用いた液晶表示装置

【課題】生産工程が単純化された薄膜トランジスタ及びそれを用いた液晶表示装置

【解決手段】絶縁基板11上の光透過型感光性樹脂12の開口部に形成されたゲート電極13と、光透過型感光性樹脂及びゲート電極上に形成されたゲート絶縁膜14と、

ゲート絶縁膜の一部の上に形成された半導体層15、オーミックコンタクト層16及び保護膜17と、ゲート絶縁膜、半導体層、オーミックコンタクト層及び保護膜上の光透過型感光性樹脂18の2つの開口部に形成されたソース・ドレイン電極19とを備え、前記ゲート電極及びソース・ドレイン電極が、金属微粒子を含有するインクを用いたインクジェット塗布により形成された電極であることを特徴とする薄膜トランジスタ

(もっと読む)

CMOSデバイスの自己形成金属シリサイド化ゲート

【課題】 CMOSデバイスの自己形成金属シリサイド化ゲートを提供すること。

【解決手段】 シリサイドが自己形成され(すなわち、別個の金属/シリコン反応ステップを必要とせずに形成され)、シリコン材料のCMP又はエッチ・バックを必要としない、金属シリサイド・ゲートをFETデバイスに形成するためのプロセス。第1のシリコン材料層(3)(ポリシリコン又はアモルファス・シリコン)が、ゲート誘電体(2)の上に形成され、次いで、金属層(4)が第1のシリコン材料層(3)の上に形成され、金属層(4)の上に第2のシリコン材料層(5)が形成される。その後、ソース/ドレイン活性化アニールのような高温(700℃より高い)処理ステップが実施され、このステップは、金属層(4)の金属を第1のシリコン材料層(13)におけるシリコン材料と反応させることにより、ゲート誘電体(2)の上にシリサイド層(30)を形成するのに有効である。第2の高温処理ステップ(ソース/ドレインのシリサイド化のような)を実施することができ、これは第2のシリコン材料層(5)におけるシリコン材料から第2のシリサイド層(50)を形成するのに有効である。シリサイド層の厚さは、高温処理において、第1のシリコン材料層の実質的にすべて及び第2のシリコン材料層の少なくとも一部が、シリサイド材料で置き換えられるような厚さである。従って、完全シリサイド化ゲート構造体を生成することができる。

(もっと読む)

n−FET用途のためのHfSiN金属を形成する方法

【課題】 高k誘電体及び界面層を含むゲート・スタック上に、熱的に安定した新しい金属化合物を提供すること。

【解決手段】 高k誘電体及び界面層を含むゲート・スタック上に、約4.0eVから約4.5eVまで、好ましくは約4.3eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む金属化合物である。さらに、(約1000℃のオーダーの)高温でHfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価酸化物厚(伝統的には、12Å)をもたらす。

(もっと読む)

2,161 - 2,180 / 2,474

[ Back to top ]