Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

2,301 - 2,320 / 2,474

アクティブマトリクス基板の製造方法及び電気光学装置並びに電子機器

【課題】着弾した液滴を確実に溝内に塗れ拡がらせて細線化を可能にする

【解決手段】基板上にゲート配線を形成する第1の工程と、ゲート配線上にゲート絶縁膜を形成する第2の工程と、ゲート絶縁膜を介して半導体層を積層する第3の工程と、ゲート絶縁層の上にソース電極及びドレイン電極を形成する第4の工程と、ソース電極及び前記ドレイン電極上に絶縁材料を配置する第5の工程と、絶縁材料を配置した上に画素電極を形成する第6の工程と、を有し、第1の工程及び第4の工程及び第6の工程の少なくとも一つの工程では、機能液32が塗布される被塗布領域31と、被塗布領域31を囲んで形成されたバンクBとを有し、被塗布領域に対する機能液の接触角と、バンクに対する機能液の接触角との差が40°以上であり、バンク間の溝幅Wが、吐出された機能液の液滴の直径Dよりも小さい基板Pに対して機能液を吐出する。

(もっと読む)

誘電体層表面処理を有する電子デバイスの製造方法

(a)(i)モノマーを含む前駆物質をプラズマ重合すること、および(ii)モノマーのインターポリマー化単位のポリマーを1つ以上含むターゲットからスパッタリングすることからなる群から選択されたプラズマによる堆積技術を用いて、実質的にフッ素化されていないポリマー層を誘電体層上に堆積する工程であって、前記モノマーが芳香族モノマー、実質的に炭化水素のモノマー、およびそれらの組合せからなる群から選択される工程と、(b)有機半導体層を前記ポリマー層に隣接して堆積する工程とによる、電子デバイスの製造方法。  (もっと読む)

(もっと読む)

低圧冷間溶接によるデバイス製造方法

パターン形成されたスタンプ、好ましくは柔らかいエラストマースタンプから基板に金属および/または有機層を転写する方法が提供される。 このパターン形成された金属または有機層は例えば広範囲の電子デバイスで使用することができる。 この方法は、有機電子構成部品のナノスケールパターン形成に特に適している。  (もっと読む)

(もっと読む)

薄膜トランジスタの製造方法

【課題】 段差のある部位に電極又は配線等を形成する工程を含む薄膜トランジスタの製造方法において、該段差部位に簡便且つ確実に積層膜或いは連結膜を形成することが可能な方法を提供する。

【解決手段】 本発明の製造方法は、半導体層84上であって当該半導体層84の略中央部に位置する第1バンク部31bと、半導体層84の周縁であって、該半導体層84を取り囲む形にて形成される薄膜部32と該薄膜部32を取り囲む形にて形成される厚膜部33とを有する第2バンク部31aと、を含むバンクを形成する工程と、薄膜部32と第1バンク部31bとに取り囲まれた領域内に、導電材料を含む第1機能液60を、半導体層84を覆う形にて配置する工程と、該第1機能液を乾燥させて第1導電膜を得る工程とを含み、その後、薄膜部32を除去して、該除去領域に第2導電膜を形成することを特徴とする。

(もっと読む)

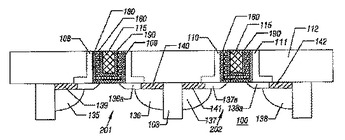

横型MOSトランジスタ

【課題】 配線抵抗及び配線容量を低減するとともに、チップ面積を削減する。

【解決手段】 SOI基板30は、シリコン基板31の上にシリコン酸化膜32が形成され、このシリコン酸化膜32の上にN−型シリコン層33が形成されて構成される。ドレイン領域35は、シリコン層33の表面からシリコン酸化膜32まで到達して形成される。ドレイン電極42は、SOI基板30の裏面に電気的接触して形成される。導電体プラグ41は、ドレイン領域35の表面からドレイン領域35およびシリコン酸化膜32を貫通してシリコン基板31中に延在して、ドレイン領域35およびシリコン基板31に電気的接触して形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 界面抵抗Rcが小さいSchottky−S/D構造を含むMOSトランジスタを提供すること。

【解決手段】 チャネル型が第1導電型であるMOSトランジスタは、第1および第2のチャネル領域CHを含む第1導電型半導体領域1と、第1および第2のチャネル領域CH上に設けられたゲート絶縁膜2と、ゲート絶縁膜2上に設けられたゲート電極3と、第1および第2のチャネル領域CHを挟むように設けられ、かつ、第1導電型半導体領域1とショットキー接合する、互いに離間した第1および第2のソース/ドレイン領域4を備えている。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】 金属ゲート電極、金属ソース領域および金属ドレイン領域を備え、電流駆動能力を高めた電界効果型トランジスタおよびその製造方法を提供することである。

【解決手段】 ソース領域26、ドレイン領域28、およびゲート電極31n、31pをシリサイド等の金属材料により構成し、nチャネルMISFET24nでは、ゲート電極31nの仕事関数Wgとソース領域26の仕事関数Wsとの関係がWg<Wsであり、pチャネルMISFET24nでは、ゲート電極31pの仕事関数Wgとソース領域26の仕事関数Wsとの関係がWg>Wsであるように金属材料を選択する。

【効果】 ソース領域26とチャネル領域29との界面のバリア高さが低下し、チャネル領域29のキャリア濃度が向上し電流駆動能力が向上する。

(もっと読む)

表示デバイスおよびその製法、ならびにスパッタリングターゲット

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】ガラス基板上に配置された薄膜トランジスタと、透明電極によって形成された画素電極と、これら薄膜トランジスタと画素電極を電気的に接続するアルミニウム合金膜によって形成された接続配線部を主たる構成要素として備えた表示デバイスとその製法を開示する。

(もっと読む)

半導体装置の製造方法、電極膜、MOSトランジスタ、及び半導体装置

【課題】

容易に膜厚が制御され、かつ結晶性が良好であり、低抵抗率や良好なエッチング選択性等といった、良好な特性を示すシリサイド膜およびその作製手段を提供する。

【解決手段】

本発明では、半導体基板上に電極膜を成膜する時、基板温度を400℃から900℃まで加熱しながら、成膜速度を極めて遅くして(1〜1000Å/min)堆積させる。また、電極膜を成膜する前に、ArイオンやGeイオンやXeイオンによって表面を非晶質化するためのイオン注入をおこなってもよい。また、電極膜を成膜中にSiが電極膜中に拡散するための時間およびシリサイド化反応が進む時間が、成膜時間だけでは足らない場合は、数原子層成膜した後、Siが拡散してシリサイド化反応が進むまで成膜を止めて、適切な時間が経過した後、再び電極膜を成膜する、多段階成膜法をおこなっても良い。

(もっと読む)

液晶表示装置の製造方法

【課題】液晶表示装置の低抵抗配線を作製するにあたって、ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止し、かつスパッタ時のダスト発生を抑制する。

【解決手段】Al合金配線を有する液晶表示装置を製造するにあたって、Y、Sc、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Th、Sr、Ti、Zr、V、Nb、Ta、Cr、Mo、W、Mn、Tc、Re、Fe、Co、Ni、Pd、Ir、Pt、Cu、Ag、Au、Cd、Si、PbおよびBから選ばれる第1の元素を0.001〜30原子%の範囲で含み、残部が実質的にAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、O、NおよびHから選ばれる第2の元素を含むガスを使用し、得られたインゴットまたは焼結体を加工してスパッタターゲットを作製する。このスパッタターゲットをスパッタして形成したAl合金膜にエッチング処理を施してAl合金配線を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 微粒子とこの微粒子に結合した有機半導体分子とによって導電路が形成され、その導電性が電界によって制御されるように構成された半導体装置及びその製造方法であって、デバイス構造を工夫することによって性能が向上した半導体装置及びその製造方法を提供することにある。

【解決手段】 金などの微粒子10と、この微粒子に結合した有機半導体分子13との結合体を電極2の上に層状に形成し、電極2の反対側の結合体層の面上に電極6を設け、電極2と電極6との間の結合体層の膜厚方向に形成された導電路の導電性を、ゲート電極4を通じて制御する縦型電界効果トランジスタを形成する。上記結合体層では微粒子10と有機半導体分子13とが交互に結合したネットワーク型の導電路が形成される。この導電路では、有機半導体分子内の導電路が微粒子内の導電路によって連結され、有機半導体分子内の移動度を最大限に利用することができる。

(もっと読む)

液晶表示装置の製造方法およびTFT基板

【課題】液晶表示装置製造の費用減少、生産性向上。

【解決手段】TFT部及びゲート−パッド連結部に第1及び第2金属膜を蒸着しそれら金属膜をパターニングしゲート電極及びゲートパッドを形成する段階、全面に絶縁膜を形成する段階、第1及び第2非晶質シリコン膜パターンをTFT部の絶縁膜上に形成する段階であって第2非晶質シリコン膜全体の下部表面が第1非晶質シリコン膜表面と当接するようそれらのパターンを形成する段階、ソース及びドレイン電極をTFT部上に形成しソース及びドレイン電極間の第2非晶質シリコン膜を除去する段階、ドレイン電極及びゲートパッドの一部が露出されるよう保護膜を形成しゲートパッドの一部上の絶縁膜を除去する段階、第1及び第2画素電極パターンを形成する段階を含み、第1金属膜はCr、Mo、Ta及びTiのうち1つの金属膜であり、第2金属膜はAl又はAl合金である。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

無線チップ及びその作製方法

【課題】本発明は、無線チップのコストを下げることを課題とする。また、無線チップの大量生産を可能として、無線チップのコストを下げることを課題とする。さらに、小型・軽量な無線チップを提供することを課題とする。

【解決手段】本発明は、ガラス基板や石英基板から剥離された薄膜集積回路が第1の基体と第2の基体に設けられた無線チップを提供する。本発明の無線チップは、シリコン基板からなる無線チップと比較して、小型、薄型、軽量を実現する。本発明の無線チップが含む薄膜集積回路は、少なくとも、LDD(Lightly Doped drain)構造のN型の薄膜トランジスタと、シングルドレイン構造のP型の薄膜トランジスタと、アンテナとして機能する導電層とを有することを特徴とする。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタシート及びこれらの製造方法

【課題】 基板への接着性が良好で、且つ、良好に駆動可能な有機薄膜トランジスタ、該有機薄膜トランジスタを設けた有機薄膜トランジスタシート及びこれらの製造方法の提供。

【解決手段】 支持体と金属箔とをラミネートする接着層を支持体上に有し、前記支持体と前記金属箔とが前記接着層によりラミネートされ、前記支持体上にラミネートされた前記金属箔表面が研磨されたものであることを特徴とする有機薄膜トランジスタ。

(もっと読む)

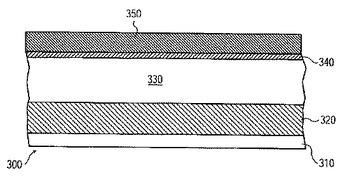

リンが注入されたポリシリコンのシート抵抗の減少

リンが注入されたポリシリコンのシート抵抗を減少するプロセスが存在する。一実施の形態において、MOSトランジスタ構造(300)が存在する。構造は、ゲート領域、ドレイン領域及びソース領域を有する。ゲート領域のシート抵抗を減少する方法(220)は、予め決定された温度で真性アモルファスシリコンをゲート領域に堆積する(221)。アモルファス化の種が、真性アモルファスシリコンに注入される(222)。その後、リンの種が、MOSトランジスタ構造のゲート領域に注入される(223)。この実施の形態の特徴は、アモルファス化の種としてのAr+の使用を含む。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 製造工程を単純化し、製造費用を最少化でき、かつ安定した特性を確保できる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタ表示板は、画素部と駆動部を有する絶縁基板、絶縁基板上に形成され、ソース領域及びドレイン領域、チャンネル領域及び低濃度ドーピング領域を有する多結晶シリコン層、多結晶シリコン層を覆うゲート絶縁膜、ゲート絶縁膜を介在してチャンネル領域と重畳し、不純物がドーピングされているケイ素を有する不純物層、不純物層上部に形成されているゲート電極、ゲート電極を覆い、各々ソース領域及びドレイン領域を露出させる第1及び第2コンタクトホールを有する層間絶縁膜、層間絶縁膜上に形成され、第1コンタクトホールを介してソース領域と接続されるソース電極、層間絶縁膜上に形成され、第2コンタクトホールを介してドレイン領域と接続されるドレイン電極を有する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

【解決手段】基板101上に第1の膜102を形成する工程と、前記第1の膜102上にマスク材料を含有する溶液を吐出して前記第1の膜102上にマスク103を形成する工程と、前記マスク103を用いて前記第1の膜102をパターニングして前記基板101上に塗れ性の低い領域104と塗れ性の高い領域105を形成する工程と、前記マスク103を除去する工程と、前記塗れ性の低い領域104に挟まれた前記塗れ性の高い領域105に、絶縁膜、半導体膜又は導電膜材料を含有する溶液106を吐出して絶縁膜、半導体膜又は導電膜のパターンを形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

金属層を有する半導体素子の形成方法

半導体基板(12)上に形成された金属酸化物(14)上に金属層(24)を形成する。金属層の所定の限界寸法を決定する。第1エッチングにより金属層を下方へと金属酸化物に至るまでエッチングし、金属層の側壁にフーティング(26)を形成する。金属酸化物に対し選択的である第2エッチングにより、所定の限界寸法を狙ってフーティングを除去する。一実施形態において、金属層上に導電層(22)を形成する。金属層と接触している部分を残存させつつ、導電層の大部分をエッチングする。次に、金属層と接触している残余部分を、金属層に対して選択的な化学物質を用いてエッチングする。  (もっと読む)

(もっと読む)

2,301 - 2,320 / 2,474

[ Back to top ]