Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

2,441 - 2,460 / 2,474

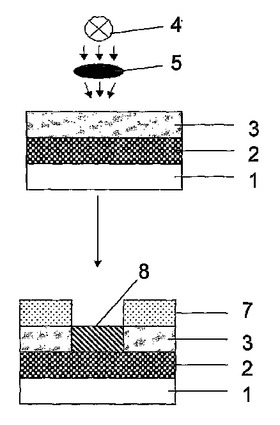

金属被着

レーザによりパターン化された基板上に金属を無電解メッキする方法。基板上に熱画像形成層および触媒層がともに被着される。レーザ・ビームで露光すると、熱画像形成層において十分なレベルの放射が熱に変換され、それによって、隣接する触媒層の露光領域が不活性になる。次いで、レーザによりパターン化された基板を反応溶液に暴露し、それによって、触媒層の非露光領域上で金属被膜の成長が開始される。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

本発明は、基板110、基板上に形成されているゲート電極124、基板及びゲート電極を覆っているゲート絶縁膜140、ゲート絶縁膜上に形成されているソース電極173及びドレイン電極175、ゲート絶縁膜、ソース電極、及びドレイン電極上に形成されている半導体層150、半導体層、ソース電極、ドレイン電極及びゲート絶縁膜を覆っている保護膜180を含み、ゲート絶縁膜及び保護膜はパリレンからなる薄膜トランジスタ表示板を提供する。  (もっと読む)

(もっと読む)

ダマシンプロセスにより形成されるトライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の第1端部に隣接するソース領域(210)、フィン(205)の第2端部に隣接するドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上にダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、絶縁層(605)中にトレンチ(705)を形成するように、ダミーゲート(505)を除去するステップと、トレンチ(705)中に金属ゲート(905)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

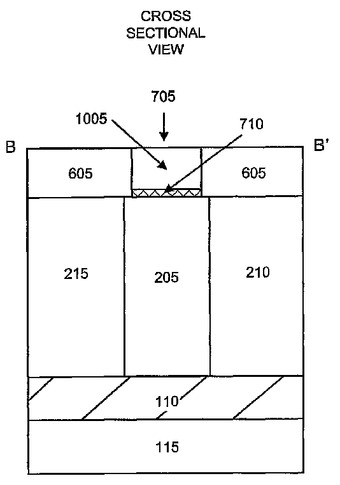

細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の一端上にソース領域(210)、このフィン(205)の他端上にドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上に、第1パターンで、第1半導体材料のダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、第1パターンに対応する絶縁層(605)中にトレンチ(705)を残すように、第1半導体材料を除去するステップと、トレンチ(705)内に露出したフィン(205)の部分を細型化するするステップと、トレンチ(705)内に金属ゲート(1005)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

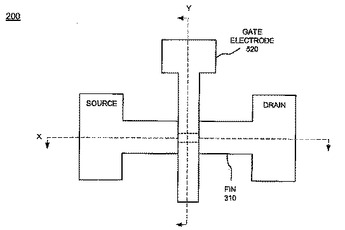

セルフアラインされたダマシンゲート

基板上のフィン領域、ソース領域、およびドレイン領域をパターン化するステップと、フィン領域中にフィン(310)を形成するステップと、フィン領域中にマスク(320)を形成するステップと、を含む、MOS電界効果トランジスタ(MOSFET)(200)を形成する方法である。この方法は、MOSFETのチャネル領域(330)を露出するように、マスク(320)をエッチングするステップと、チャネル領域(330)中のフィン(310)の幅を薄くするようにフィン(310)をエッチングするステップと、フィン(310)上にゲートを形成するステップと、ゲート、ソース領域およびドレイン領域に対するコンタクトを形成するステップと、をさらに含む。  (もっと読む)

(もっと読む)

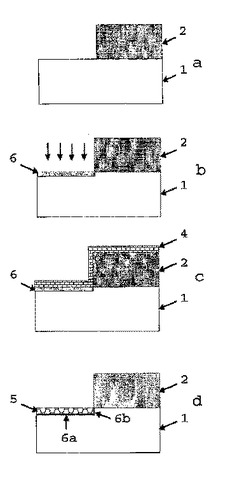

少なくとも一つの電気的コンポーネントを有するフィルム及びその生産プロセス

【課題】

本発明は、少なくとも一つの電気的コンポーネントを有するフィルムと、そのようなフィルムの生産プロセスと、に関するものである。

【解決手段】

放射架橋性接着剤を備えた接着剤層はベースフィルム(61)に塗布される。接着剤層はベースフィルムへパターン形状に塗布され、及び/または、接着剤層がパターン形状に構造化して硬化するようにパターン形状に放射線照射される。キャリアフィルムと電気的機能層とを備えたトランスファーフィルム(41)が接着剤層に塗布される。キャリアフィルム(41)は、ベースフィルム、接着剤層、及び電気的機能層を含むフィルム体から剥がされ、そこではパターン形状に構造化された第一領域では電気的機能層はベースフィルム(61)に残り、パターン形状に構造化された第二領域では電気的機能層は前記キャリアフィルム(45)に残り、ベースフィルム(61)からキャリアフィルムとともに取り除かれる。

(もっと読む)

(もっと読む)

感熱性中規模デポジションのレーザ処理

マスクなし中規模材料デポジション(Maskless Mesoscale Material Deposition, M3DTM)処理のための方法および装置が開示され、これはエアロゾルを作るのに好ましくは超音波トランスデューサまたは圧縮空気噴霧器(22)を用い、このエアロゾルは流入口(20)を経由してフローヘッド(12)に入り、その際に随意的に、ガス量を低減するため事実上のインパクタ(24)ならびに溶剤を除去するまたは粘度を調整するためヒータアセンブリ(18)の両方を、あるいはそのいずれかを経由するようにしてもよい。機械的シャッター(28)のついた材料シャッターアセンブリ(26)が好ましくはフローヘッドの出口についており、鞘状のガスが流入口(18)を通って入り、エアロゾルがフローヘッドから出る前にそれを囲む。熱に弱いターゲットの上のエアロゾルデポジット材料は好ましくはレーザモジュール(10)からのビームで処理し、これによってそのターゲットを損傷閾値以上に加熱することなく、たとえば化学分解、焼結、重合などにより希望の状態を得るためにデポジットした材料を加熱する。1ミクロンの線幅の形状をデポジットすることができる。 (もっと読む)

半導体装置とこの種の半導体装置の製造方法

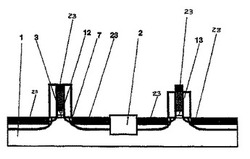

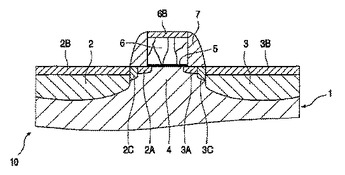

この発明は、基板と半導体本体(1)とを有する半導体装置(10)に関し、半導体本体(1)がソース(2)及びドレイン(3)を有する第一のFET(3)を備え、ソース(2)及びドレイン(3)は、金属シリサイドを含む接続領域(2B,3B)が設けられ、そして、ゲート(6)下部のチャネル領域(4)と境界を成し且つソース(2)及びドレイン(3)より厚みが薄く且つドーピング濃度が低いソース及びドレイン領域拡張部(2A,3A)に接続されている。ソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)とは、第一の導電型で且つ厚み及びドーピング濃度がソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)との間の中間領域(2C,3C)により互いに接続されている。このようにして、接続領域(2B,3B)と基板と間にリーク電流並びに短絡が起きるのが抑制され、一方で、ソース及びドレイン領域拡張部(2A,3A)を用いることの効果が維持される。好ましくは、中間領域(2C,3C)がゲート(6)直近のスペーサ(7)下部に位置し、好ましくは、これらは、なるべく傾けられたイオン注入により形成される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

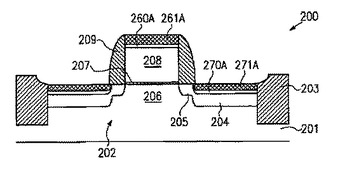

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

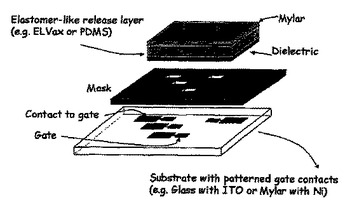

マスクを通した積層

本発明はドナー基板からレシーバ基板に材料のパターンを積層によって転写する方法である。転写された材料のパターンは、積層の際にドナーとレシーバとの間に挿入されたマスクの開口によって画定される。この技法は可撓性ポリマーレシーバ基板に適合しており、可撓性表示装置用の薄膜トランジスタを作製するのに有用である。

(もっと読む)

(もっと読む)

CMOS電界効果トランジスタを製造するための方法及び装置

【課題】 集積回路の製造におけるCMOS電界効果トランジスタを製造するための改善された方法、及び、トランジスタの金属ゲートの仕事関数を制御するための改善された方法を提供すること。

【解決手段】 トランジスタのゲート電極を含むポリシリコン材料を選択的にドープするステップと、完全にシリサイド化するステップとを含む、相補型金属酸化膜半導体(CMOS)電界効果トランジスタを製造する方法である。一実施形態において、シリサイド化する前に、ポリシリコンがアモルファス化される。更に別の実施形態において、シリサイド化が、低い基板温度で実行される。

(もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

高解像度構造を有する有機電子部品及びその生産方法

【課題】本発明は、高解像度構造を有する有機電子部品、特に低ソースドレーン間の距離を有する有機電界効果トランジスタ(OFET)及びその生産方法に関する。

【解決手段】有機電子部品は、生産中レーザーを用いて作られた凹部及び/又は修正された区域を有し、その中には、例えば、金属の導体トラック/電極が配置される。

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

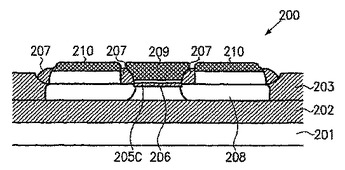

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

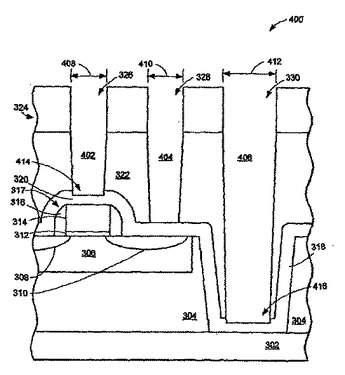

集積回路におけるコンタクトサイズをサイジングすることによって多層コンタクトを製造するための方法

集積回路を形成するための方法(600)は、第1半導体基板(202)上の半導体デバイス(317)表面上の誘電材(322)における第1深さに第1開口部(228)、(338)、(402)をエッチングし、第1半導体基板(202)表面上の誘電材(322)において第2深さに第2開口部(230)、(340)、(404)をエッチングする。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、エッチングラグに起因してほぼ同時に第1及び第2深さにエッチングするためにそれぞれ異なってサイズされる。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、導電材で充填される。  (もっと読む)

(もっと読む)

2,441 - 2,460 / 2,474

[ Back to top ]