Fターム[4M104CC05]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574) | MISゲート電極 (3,643)

Fターム[4M104CC05]に分類される特許

2,001 - 2,020 / 3,643

トレンチゲートの形成方法

【課題】セルコンタクトのショート等の問題がなく、またゲートトレンチ内にシリコン基板材料によるバリが残らず、良好な特性を有するトレンチゲートの形成方法を提供する。

【解決手段】まずシリコン基板10上にゲートトレンチ10aを形成し、次いでゲートトレンチ10aが形成されたシリコン基板10上に素子分離領域16aを形成する。そのため、ゲートトレンチ10a内にシリコン基板材料のバリが発生することがなく、理想的なトレンチ形状を得ることができる。

(もっと読む)

FINFETデバイスのフィンの上に完全にシリサイド化されたデュアル・ゲートを形成する方法

【課題】 FinFetデバイスのフィンの上に完全にシリサイド化されたデュアル・ゲートを形成する方法を提供すること。

【解決手段】 FinFetデバイスのフィンの上に完全にシリサイド化されたゲートを形成する方法が開示される。本開示は、ポリシリコン層及びポリシリコン・ゲルマニウム層から各々のフィンの上のゲート・スタックをパターン形成し、次に、フィンの一方の上のポリシリコン・ゲルマニウム層を除去する方法を提供する。本開示は、さらに、両方のフィンの上に金属層を形成することと、FinFetデバイスをアニールして、FinFetデバイスの各々のフィンの上に完全にシリサイド化されたゲートを形成することとを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】混晶層中のGe濃度およびC濃度の許容範囲内で、チャネル領域に十分に応力を印加することが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】Si基板1上にダミーゲート電極3を形成する。次に、ダミーゲート電極3をマスクにしたリセスエッチングにより、リセス領域7を形成する。次いで、リセス領域7の表面に、SiGe層からなる混晶層8をエピタキシャル成長させる。続いて、ダミーゲート電極3を覆う状態で、混晶層8上に、層間絶縁膜12を形成し、ダミーゲート電極3の表面が露出するまで、層間絶縁膜12を除去する。ダミーゲート電極3を除去することで、層間絶縁膜12にSi基板1を露出する凹部13を形成する。その後、凹部13内にゲート絶縁膜14を介してゲート電極15を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】特性のばらつきや劣化を低減できる半導体装置の製造方法を提供する。

【解決手段】オフセットスペーサ用材料として、HfSiOを堆積した後に、表面を窒化させることで、シリコン基板10およびゲート構造を覆うようなHfSiON膜15を形成する。次に、HfSiON膜15に、異方性ドライエッチングを行うことにより、シリコン基板10およびゲート電極層14の上面に沿った領域のみにダメージを大きく与える。次に、濃度が5%程度のフッ酸水溶液で90秒程度の洗浄を行うことにより、HfSiON膜15のうちダメージが大きく与えられた領域のみが選択的にウェットエッチング除去される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造の小型化に対応しやすく、製造が容易な3次元構造のゲート絶縁膜を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、半導体基板に3次元構造のゲート絶縁膜が形成され、ゲート絶縁膜に接するゲート電極が半導体基板上に突出形成され、ゲート絶縁膜の周囲の半導体基板に該半導体基板の拡散層領域を介してソース電極およびドレイン電極が形成され、ゲート電極周囲の半導体基板上面が、半導体基板上に突出形成されたゲート電極の側面を覆う保護絶縁膜で覆われ、この保護絶縁膜の上に層間絶縁膜が積層されてなる。

(もっと読む)

不揮発性記憶素子及び半導体集積回路装置

【課題】電荷保持膜を有する不揮発性記憶素子のトンネル消去を可能とする。

【解決手段】半導体基板上に第1絶縁膜(42)を形成し、その上に、ソース領域(8)、ドレイン領域(7)、及びそれらの間にチャネル領域(9)を形成する半導体領域(1)を設け、チャネル領域上に第2絶縁膜(2)、その上に電荷保持膜(4)、更にその上にゲート電極(6)を設ける。半導体基板内に形成される共通ソース配線領域(54)は接続孔(53H)を介してソース領域に接続される。接続孔は、第1絶縁膜をゲート電極の側壁に形成されたサイドウォールスペーサ(52)に対して自己整合的に除去することで形成される。接続孔にソース領域と共通ソース配線領域が接続されるプラグ(37)が形成される。電荷保持膜が保持する電子を放出する動作をトンネルによって行っても第2絶縁膜に電子が残存する事態を阻止できる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】 本発明は、基板との密着性が高い酸化被膜を形成して、配線材料等の酸化を防止できると共に、導電率が高い配線、電極又は端子電極を備えた液晶表示装置及びその製造方法を提供することにある。

【解決手段】 本発明では、TFT型液晶表示装置のTFT側基板の上に形成されたゲート配線あるいはゲート電極であって、配線あるいは電極は、二つの異なる絶縁層あるいは絶縁物に挟持された構造を有し、これらは銅を主成分とした第一の層と、当該第一の層の外周部を被覆する酸化物からなる第二の層からなり、さらに第二の層の組成式が、CuXMnYSiZO(0<X<Y,0<Z<Y)であること、を特徴とする。

(もっと読む)

電子デバイスおよびその製造プロセス

【課題】金属酸化物半導体電界効果トランジスタのような金属絶縁体デバイスおよび/または金属絶縁体金属キャパシタを提供する。

【解決手段】装置は、

炭化タンタル、炭窒化タンタル、炭化ハフニウム、および炭窒化ハフニウムからなる組から選択される金属化合物を含む電極と、

窒素とシリコンを含む酸化ハフニウムからなるhigh−k誘電体層であって、少なくとも4.0のk値を有するhigh−k誘電体層と、

電極とhigh−k誘電体層との間に配置された窒素および/またはシリコンおよび/または炭素のバリア層とを含み、

窒素および/またはシリコンおよび/または炭素のバリア層は、1またはそれ以上の金属酸化物を含み、金属酸化物の金属はランタニド、アルミニウム、およびハフニウムからなる組から選択される。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイド構造を有する半導体装置において、接合リーク特性を劣化させずにゲート細線抵抗を向上することができる半導体装置を得ること。

【解決手段】シリコン基板1上にゲート絶縁膜12を介して形成されたポリシリコン膜14およびシリサイド膜15からなるゲート電極13と、ゲート電極13の下部のチャネル領域を挟んで形成された所定の導電型の不純物イオンが拡散された拡散層17、および拡散層17の表面に形成されるシリサイド膜18からなるソース/ドレイン領域と、を有する半導体装置において、ゲート電極13のシリサイド膜15の膜厚が、拡散層17上のシリサイド膜18の膜厚よりも厚い。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート構造の半導体装置及びその製造方法の提供を課題とする。

【解決手段】本発明の半導体装置は、半導体基板に形成された溝内にゲート絶縁膜を介し形成されたゲート電極と、ゲート電極の近傍の半導体基板にゲート絶縁膜を介して配置されたソース領域及びドレイン領域とを具備してなるトレンチゲートトランジスタを備え、ゲート電極が溝の内側から溝の外側まで突出形成され、ゲート電極が溝の内側と外側とで幅方向に位置ずれ部を形成した目ずれ形状に形成されてなり、ゲート電極の目ずれ部分が溝の開口周縁部より上方に配置されてなる。

(もっと読む)

半導体装置及びその作製方法

【課題】SOI基板を用いて作製した半導体装置において、島状に設けられたシリコン層の端部に起因する不良を防止し、信頼性の向上した半導体装置及びその作製方法を提供する。

【解決手段】支持基板上に絶縁層、島状のシリコン層が順に積層されたSOI基板と、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層と、ゲート絶縁層を介して島状のシリコン層上に設けられたゲート電極と、を有する構造とする。このとき、ゲート絶縁層は、島状のシリコン層の一表面上と比較して、島状のシリコン層の側面と接する領域の誘電率を小さくする。

(もっと読む)

Cu合金配線膜とそのCu合金配線膜を用いたフラットパネルディスプレイ用TFT素子、及びそのCu合金配線膜を作製するためのCu合金スパッタリングターゲット

【課題】電気抵抗率の低いCuを配線材料として使用できるばかりか、ガラス基板への密着性が高く剥離の危険性がないCu合金配線膜と、そのCu合金配線膜を用いて作製されるフラットパネルディスプレイ用TFT素子と、そのCu合金配線膜の作製に用いられるCu合金スパッタリングターゲットを提供することを課題とする。

【解決手段】フラットパネルディスプレイ用のTFT素子1を構成する配線膜2とその膜を作製するためのスパッタリングターゲットであって、Cuを主成分とし、Pt、Ir、Pd、Smの少なくとも一種を合計0.01〜0.5原子%含有する。ガラス基板3上に前記配線膜2を積層し、更にその上に絶縁膜4を介して透明導電膜5を積層する。

(もっと読む)

ゲート電極中のドーパンの相互拡散バリア構造及びその製造方法

【課題】ゲート電極中のドーパンの相互拡散バリア構造及びその製造方法を提供する。

【解決手段】半導体デバイスにおいてゲートのNFET側からゲートのPFET側への拡散を低減する又は防止さえする構造、同様にその製造方法が開示される。拡散バリアは、NFETとPFETとの間のN/P境界のところの共有ゲート中に形成される。拡散バリアは、1又は複数の種類のイオン、例えば、酸素、窒素、フッ素、シリコン、ゲルマニウム、又はキセノン・イオン(しかし、これらに限定されない)でドープされる。本明細書中で開示されるような拡散バリアを使用することによって、CMOS技術半導体デバイス・ノードにおけるNFET側からPFET側への共通ゲートを通してのイオンの拡散は、大いに低減されることができる又は完全に防止することさえもできる。これは、さらにNFET/PFET対の相対的により高い性能をもたらすことができる。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】半導体素子は、第1導電型の半導体基板(n型基板50)と、前記半導体基板(50)に形成された第2導電型のベース領域(p型ベース領域54)と、前記ベース領域(54)内に形成され、前記基板(50)の反対面に形成された高濃度第1導電型のソース領域(n型ソース領域56)と、前記ソース領域(56)とベース領域(54)を貫通して形成され、相違する幅と形状に形成される第1トレンチT1、第2トレンチT2と、を含む。

(もっと読む)

多重拡散防止膜を備える半導体素子

【課題】ゲートスタックのシート抵抗及びコンタクト抵抗が小さいながらも、不純物の外部拡散を効果的に抑制することのできる拡散防止膜を備える半導体素子を提供すること。

【解決手段】第1導電層(211)と、第1導電層(211)上に形成され、且つ金属シリサイド膜(212A)及び窒素含有の金属膜(212B)の順に積層された第1拡散防止膜と、該第1拡散防止膜上の少なくとも窒素含有の金属シリサイド膜(212D)を含む第2拡散防止膜と、該第2拡散防止膜上の第2導電層(213)とを備える。

(もっと読む)

ゲート構造を有する半導体素子及びその製造方法

【課題】ゲートコンタクト抵抗値及びシート抵抗値を同時に低くし得る中間構造物を有するゲート構造及びゲート構造を有する半導体素子、並びにそれらの製造方法を提供すること。

【解決手段】本発明の半導体素子は、上面及び下面を有する基板21と、基板21の上面近くに形成され、ゲート絶縁膜22、ゲート絶縁膜22上に形成された第1電極23、第1電極23上に形成された中間構造物24、及び中間構造物24上に形成された第2電極25を含むゲート構造とを備え、中間構造物24が、チタン(Ti)を含む第1Ti膜101と、タングステン及びシリコンを含み、第1Ti膜上に形成された第2W膜24Dとを備えることを特徴とする。

(もっと読む)

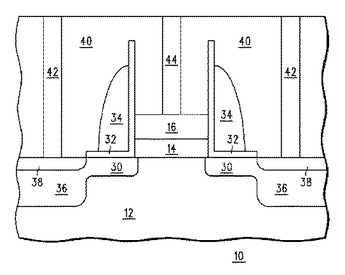

金属電極を有する半導体素子の形成、及び半導体素子の構造

半導体素子(10)を形成する方法は、ゲート誘電体(14)を基板(12)の上に形成する工程と、金属電極(16)をゲート誘電体(14)の上に形成する工程と、ポリシリコンまたは金属を含む第1犠牲層(18)を金属電極の上に形成する工程と、第1犠牲層(17)を除去する工程と、そしてゲート電極コンタクト(44)を金属電極(16)の上に位置し、かつ金属電極(16)に接続されるように形成する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

半導体装置は、第1の導電型の半導体層と、その上に形成された第2の導電型の半導体層とを含む。該半導体装置はまた、第2の導電型の半導体層内に第1の所定の距離だけ延在するボディ層と、第2の導電型の半導体層内に第2の所定の距離だけ延在する1対のトレンチとを含む。1対のトレンチのそれぞれは、基本的にその中に配置された誘電体材料から成り、第2の導電型の半導体層内に存在する不純物のドープ濃度、および1対のトレンチ間の距離は、半導体装置の電気的特性を画定する。該半導体装置は、第2の導電型の半導体層に結合された制御ゲートと、第2の導電型の半導体層に結合されたソース領域とをさらに含む。  (もっと読む)

(もっと読む)

ランディングプラグコンタクトを備える半導体素子の製造方法

【課題】オートアライメントコンタクトを利用したコンタクト形成の際、高い縦横比によるエッチングターゲットの増加を防止でき、オートアライメントコンタクトエッチングに用いるハードマスクによる段差を克服し、後続のパターニングを容易に行い、かつ、処理を単純化させることができる半導体素子の製造方法を提供すること。

【解決手段】パターン22〜24が形成された半導体基板21上にエッチングバリア膜25を形成するステップ、エッチングバリア膜上に層間絶縁膜26Bを形成するステップ、層間絶縁膜を平坦化するステップ、層間絶縁膜をリセスさせるステップ、層間絶縁膜上にハードマスクパターン200Bを形成するステップ、層間絶縁膜をエッチングしてコンタクトホール201を形成するステップ、コンタクトホールの底のエッチングバリア膜をエッチングするステップ、及び、コンタクトホール内にプラグコンタクトを形成するステップを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】製造時に電荷蓄積層に電荷が蓄積されてしまうことを抑制することが可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、半導体基板10上に設けられた電荷蓄積層20と、電荷蓄積層20に電荷をプログラムする際に用いられるゲート電極22と、ゲート電極22と接続するヒューズ56と、を有し、ヒューズ56は、ゲート電極22に電圧が印加される際は電気的に切断されている半導体装置およびその製造方法である。

(もっと読む)

2,001 - 2,020 / 3,643

[ Back to top ]