Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

201 - 220 / 293

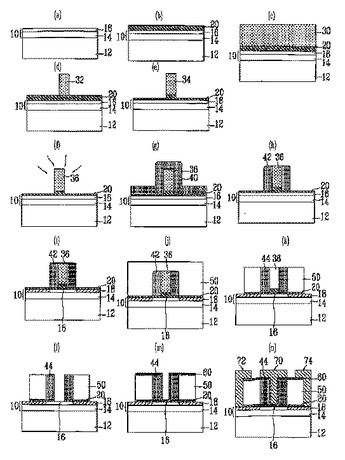

ショットキー障壁トンネルトランジスタ及びその製造方法

【課題】半導体と金属との接合時に自然に形成されるショットキートンネル障壁をトンネル障壁として用いたショットキー障壁トンネルトランジスタのゲート側壁の損傷によるリーク電流を最小化するショットキー障壁トンネルトランジスタ及びその製造方法を提供する。

【解決手段】本発明に係るショットキー障壁トンネルトランジスタの製造方法は、絶縁体基板上に半導体チャネル層を形成する工程と、半導体チャネル層にダミーゲートを形成する工程と、絶縁体基板上のダミーゲートの両側に各々当接する位置にソース及びドレインを形成する工程と、ダミーゲートを除去する工程と、ダミーゲートが除去された側壁に絶縁膜を形成する工程と、ダミーゲートが除去された空間にアクチュアルゲートを形成する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを用いた半導体装置の製造方法において、RPTの短縮、ゲート寸法の加工精度の向上を図る半導体装置の製造方法を提供する。

【解決手段】半導体基板上にダミーゲートを形成する工程、前記ダミーゲートをマスクとして前記半導体基板に不純物を導入して、ソース・ドレイン拡散領域を形成する工程、前記ダミーゲートの周囲に絶縁膜を形成する工程、前記ダミーゲートを除去して開口部を形成する工程、及び前記開口部にゲート絶縁膜を介してゲート電極を形成する工程を具備する方法である。前記ダミーゲートは、前記半導体基板上に、炭素と水素との原子比(C/H)が1以上であり、かつ炭素の絶対量が50%以上である炭素過剰の組成のポリマーを塗布してポリマー膜を形成する工程、前記ポリマー膜上にフォトレジストパターンを形成する工程、及び前記フォトレジストパターンを前記ポリマー膜に転写する工程により形成されることを特徴とする。

(もっと読む)

半導体素子の製造方法

本発明は、リソグラフィ工程を経たフォトレジストの特性を変化させてダミー構造物を形成し、これをゲート電極形成工程に適用した半導体素子の製造方法に関することで、半導体基板上の最上部にバッファー層を形成するステップと、前記バッファー層の上部に無機物フォトレジストを塗布してリソグラフィを通じてフォトレジストパターンを形成するステップと、前記形成されたパターンに特定ガスを使用して熱処理を行うステップと、前記熱処理された構造物の上部に均一な厚さの絶縁膜を蒸着した後に前記パターンが露出されるように前記蒸着された膜をエッチングするステップと、前記工程を経た構造物に絶縁膜を蒸着し、前記パターンが露出されるように前記絶縁膜をエッチングするステップと、前記露出されたパターンを除去するステップと、前記パターンが除去された位置にゲート酸化膜を形成するステップと、前記形成されたゲート酸化膜の上部にゲート電極を形成するステップと、を含む。本発明によれば、ナノ素子を製作するための構造を形成する時、リソグラフィを通じて形成された膜の特性が後続熱処理を通じて改善されるので、多様な素子を製作するための構造を容易に形成することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】不純物拡散領域の侵食等を生ぜしめることなく接合リーク電流の増大を抑制して不純物拡散領域の抵抗値を十分に低減し、更なる微細化・高集積化を実現して、低消費電力で高速動作を可能とする。

【解決手段】STI素子分離構造5を形成する際に、これをその上部が基板1面から通常のSTI法の場合よりも突出するように形成し、ゲート電極の形成部位にダミー電極パターン7を形成する。空隙部11に整合してソース/ドレイン8を形成した後、Wで空隙部11を充填してなる導電層14を形成し、ダミー電極パターン7を除去してゲート絶縁膜21及びゲート電極22を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜中の電場を緩和するとともに素子の電流駆動力を高め、高速動作を可能にし、且つ高信頼性、高性能の半導体装置を提供する。

【解決手段】基板に設けられた半導体領域3と、それぞれの端部が互いに向かい合うように離間して半導体領域に設けられたソースおよびドレイン領域4a、4bと、ソースおよびドレイン領域上とソース領域およびドレイン領域間の領域上とに設けられた半導体層5と、半導体層を介してソース領域およびドレイン領域間の領域上に設けられたゲート絶縁膜7と、ゲート絶縁膜上に設けられたゲート電極8と、を備えている。

(もっと読む)

表示装置とその製造方法

【課題】TFT基板に形成する薄膜トランジスタのゲート絶縁膜を高誘電率材料を用いた厚膜とし、かつ十分なイオンをドーピングする。

【解決手段】膜厚が厚い高誘電率材料からなるゲート絶縁膜3にコンタクトホール7aを形成した後でイオンドーピングしてn+領域7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート開口部へのメタルゲート電極の埋め込み性を改善することができる半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成された金属を含むメタルゲート電極4と、メタルゲート電極4の側壁に形成されたサイドウォール絶縁膜5とを有する。サイドウォール絶縁膜5は、メタルゲート電極4の下層部の側壁に形成された第1絶縁膜6と、第1絶縁膜6の外側であって、メタルゲート電極4の側壁全体に形成された第2絶縁膜7とを有する。メタルゲート電極4の上層部の幅は、メタルゲート電極4の下層部の幅に比べて広い。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲート電極をメタルの凝集なく仕事関数変調により形成する。

【解決手段】本発明の例に関わる半導体装置の製造方法は、半導体基板100上にゲート絶縁層102を形成する工程と、ゲート絶縁層102上に第1メタル層103を形成する工程と、第1メタル層103上に第2メタル層104を形成する工程と、第2メタル層104上に第2メタル層104よりも高い融点を持つ材料からなるキャップ層105を形成する工程と、熱処理により第2メタル層104内の元素をゲート絶縁層102と第1メタル層103との界面に析出させて析出層107を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート空乏化の抑制および低抵抗化を図った半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極4とを有し、ゲート電極4は、ゲート絶縁膜3上に形成されたシリサイド層5と、シリサイド層5上に形成された金属層6とを有する。

(もっと読む)

ゲート酸化物の漏れを抑えたリプレースメントゲートトランジスタ

ゲート酸化物層(12)とメタルゲート電極(60)との間に保護層(70)を形成することによって、リプレースメントゲートトランジスタに対してリーク電流を抑えた実効的なゲート酸化膜厚を得ることができ、これにより、応力を減らすことができる。実施形態においては、金属ゲート電極(60)から保護層を通じてゲート酸化物層(12)に向かうに従って濃度が低下する金属炭化物を含む非晶質炭素層(70)の保護層が形成される。方法の実施形態では、リムーバブルゲートを除去するステップ、ゲート酸化物層へ非晶質炭素層を蒸着するステップ、メタルゲート電極(60)を形成するステップ、を含み、さらにその後、メタルゲートからの金属を非晶質炭素層に拡散して金属炭化物を形成するように、高温に加熱するステップ、を含む。さらに、一実施形態では、高誘電定数を有するゲート酸化物層(82)と、金属ゲート電極(100)と基板(10)との界面において高濃度のシリコンと、を含むメタルゲートトランジスタが含まれる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の動作不良発生を防止できるとともに、電極間絶縁膜によって相互に隣接するコントロールゲート電極間での寄生容量が大きくなることを回避可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1を含む。トンネル絶縁膜3は、半導体基板上に設けられる。フローティングゲート電極11は、トンネル絶縁膜上に設けられる。電極間絶縁膜12は、フローティングゲート電極上に設けられる。コントロールゲート電極13は、電極間絶縁膜上に設けられ、電極間絶縁膜上の第1部分と第1部分上に設けられ且つチャネル長方向に関し第1部分より大きな幅を有する第2部分とを含む。ソース/ドレイン拡散領域15は、半導体基板の表面に形成され、フローティングゲート電極下方のチャネル領域を挟む。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン拡散層からゲート電極までの距離を長くすることなく、半導体基板上に高誘電体材料から成るゲート絶縁膜および金属から成るゲート電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10に達しかつ側壁がシリコン窒化膜60から成るトレンチ80を半導体基板上の層間絶縁膜70に形成し、シリコン窒化膜上にHfSiO膜を堆積することなく、トレンチの底面に露出した前記半導体基板上にHfSiO膜を堆積するように、200℃〜260℃のもとでHfSiO膜から成るゲート絶縁膜90を堆積し、トレンチ内に金属から成るゲート電極95を充填することを具備する。

(もっと読む)

半導体素子の形成方法

【目的】レジストパターンの寸法および形状の変動と、チャージアップダメージとを同時に解決する。

【解決手段】レジストパターン形成時に、コンタクトホール用のパターン37を画成する、矩形枠状のダミーコンタクトホール用のパターン35をチップ分離領域17の脇に沿って形成する。これにより、ウエハ単位でのパターン付き第1のレジスト層30の収縮が、チップ単位での収縮に低減される。また、このダミーコンタクトホール用のパターンから形成されるダミーコンタクトにより、導電体層を除去する際に発生する電荷を、チップ単位で基板へ逃がすことができる。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド膜からなるゲート電極を有するMISFETの製造工程において、歩留まりを向上させることのできる技術を提供する。

【解決手段】半導体基板1上にゲート絶縁膜5を形成し、このゲート絶縁膜5上にポリシリコン膜よりなるシリコンゲート電極6a、6bを形成する。そして、シリコンゲート電極6a、6bを覆うように酸化シリコン膜12を形成した後、酸化シリコン膜12の表面をCMP法で研磨することにより、シリコンゲート電極6a、6bの表面を露出する。続いて、酸化シリコン膜12上にパターニングした絶縁膜13を形成する。その後、酸化シリコン膜12および絶縁膜13上に密着膜14を形成する。次に、密着膜14上にニッケル膜15を形成する。そして、密着膜14を介してシリコンゲート電極6aとニッケル膜15とをシリサイド反応させる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長が異なる複数のゲート電極に、ゲート長に依存することなく均一な組成を持つFUSI構造を得られるようにする。

【解決手段】半導体装置は、それぞれが金属によりフルシリサイド化され、ゲート長が互いに異なる第1のゲート電極14T1及び第2のゲート電極14T2を有している。第1のゲート電極14T1及び第2のゲート電極14T2の少なくとも一方の上部には、周縁部が高く且つゲート長方向の中央部が低い凹状溝が形成されている。凹状溝は、ゲート電極14T1、14T2のゲート長に依存した幅寸法を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】チャンネル領域に応力を与えて表層部において高いキャリアの移動度を得られるようにする。

【解決手段】シリコン基板2のソース/ドレイン領域4の形成領域をエッチングで除去し、SiGe層を選択的に形成する。チャンネル領域3はSiGeによる応力を受けて圧縮歪を生ずる。チャンネル領域3の上部にあらかじめ形成したダミーゲート11を除去して応力を開放することでチャンネル領域3の表層部に大きい歪を生じさせる。この後、シリコン窒化膜7、ゲート絶縁膜5、ゲート電極6を形成する。

(もっと読む)

膜パターンの形成方法、デバイスの製造方法

【課題】 基板面内で均一な膜厚のパターンを形成することが可能な膜パターンの形成方法を提供する。

【解決手段】 本発明の膜パターンの形成方法は、機能性材料を溶媒に溶解ないし分散させてなる機能液Lを基体P上に配置し、前記機能液Lを乾燥することにより、前記機能性材料からなる膜パターンFを形成する方法であって、前記膜パターンFが形成される前記基体Pの有効領域TEに前記機能液Lを配置する工程と、前記有効領域TEの周囲の非有効領域TDに前記機能液L又は前記溶媒を配置する工程と、前記有効領域TE及び前記非有効領域TDに配置された前記機能液L又は前記溶媒を乾燥する工程とを有し、前記乾燥の開始から終了までの期間において、前記非有効領域TDに配置された前記溶媒の表面積SDが、前記有効領域TEに配置された前記溶媒の表面積SEに対して、SE≦SDを満たすように乾燥を行なうことを特徴とする。

(もっと読む)

ミラー容量低下及び駆動電流改善のための単一ゲート上の複数の低及び高Kゲート酸化物

【課題】 本発明は、ミラー容量、すなわち、オーバーラップ容量が低減され、駆動電流が改善された少なくとも1つのCMOSデバイスを有する半導体構造体を提供する。

【解決手段】 本発明の構造体は、少なくとも1つの重層ゲート導電体を備える半導体基板であって、少なくとも1つの重層ゲート導電体のそれぞれが垂直縁部を有する半導体基板と、少なくとも1つの重層ゲート導電体の下に位置する第1のゲート酸化物であって、少なくとも1つの重層ゲート導電体の垂直縁部を超えて延長しない第1のゲート酸化物と、少なくとも1つの重層ゲート誘電体の少なくとも一部の下に位置する第2のゲート酸化物とを備える。本発明によると、第1のゲート酸化物及び第2のゲート酸化物は、第1のゲート酸化物が高kであるとき第2のゲート酸化物は低kであり、あるいは前記第1のゲート酸化物が低kであるとき前記第2のゲート酸化物は低kであるという条件で、高k酸化物含有材料及び低k酸化物含有材料から選択される。

(もっと読む)

半導体装置およびその製造方法

【課題】ロールオフ特性の改善および接合リークの抑制を図った半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、半導体基板1に形成され、活性領域を区画する素子分離絶縁膜10と、活性領域における半導体基板1上にゲート絶縁膜2を介して形成されたゲート電極3と、ゲート電極3の両側における半導体基板1上に積層された2つのエクステンション層5と、ゲート電極3の側壁およびエクステンション層5の一部を覆うサイドウォール絶縁膜SWと、エクステンション層5上に積層された2つのソース・ドレイン層6と、ソース・ドレイン層6に形成されたシリサイド層7と、素子分離絶縁膜2の端部に生じた窪み部10aを埋めるように形成された埋め込み絶縁膜8bとを有する。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】短チャネル効果を抑制しつつ、一層の高速動作が可能な絶縁ゲート電界効果トランジスタ及びその製造方法の提供を目的とする。

【解決手段】チャネルが形成される半導体基板の領域と、当該領域にそれぞれ接し互いに離れて前記半導体基板上に形成されている一対のエクステンション部4と、前記一対のエクステンション部4の対向端から互いに離反する向きにさらに離れて前記エクステンション部4上に形成されている一対のソース・ドレイン領域5,6と、前記ソース・ドレイン領域5,6の間のチャネルが形成される半導体基板上において前記エクステンション部4の端部にかかる位置まで形成されているゲート絶縁膜5と前記ゲート絶縁膜5上に形成されたゲート電極Gと、少なくとも前記ゲート電極Gから前記一対のエクステンション部4にかかる領域までを被覆するように形成された応力調整層8と、を有する絶縁ゲート電解効果トランジスタ1。

(もっと読む)

201 - 220 / 293

[ Back to top ]