Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

161 - 180 / 293

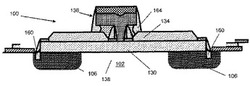

単結晶ベースを有するヘテロ接合バイポーラ・トランジスタ及び関連する方法

【課題】 単結晶ベースを有するヘテロ構造バイポーラ・トランジスタ及びこれに関連する方法を提供すること。

【解決手段】 ヘテロ構造バイポーラ・トランジスタ(HBT)及び関連する方法が開示される。一実施形態において、HBTは、基板と、基板の上のポリシリコン・エミッタと、基板内のコレクタと、コレクタに隣接した少なくとも1つの分離領域と、各分離領域の上に延びる単結晶シリコン・ゲルマニウムを含む真性ベースと、単結晶外部ベースとを含む。1つの方法は、分離領域の形成を、後で誘電体に変換される注入された多孔質シリコンの形成と置き換えるステップを含む。結果的に、分離領域の上に横方向の寸法が拡張された単結晶シリコン・ゲルマニウム・ベース・プロファイル層を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極を好適な仕事関数を有する導電材料から構成することができ、ゲート電極の構成材料と層間絶縁層のエッチング条件との関係を考慮する必要のない半導体装置を提供する。

【解決手段】NMISFET及びPMISFETを含む半導体装置であって、各ゲート電極32A,32Bは、層間絶縁層の下層部28Aに設けられたゲート電極形成用開口部に埋め込まれており、NMISFETのゲート電極32Aの少なくとも底面部と側面部は第1の導電材料33Aから構成されており、PMISFETのゲート電極32Bの少なくとも底面部と側面部は第1の導電材料とは異なる第2の導電材料33Bから構成されており、各ゲート電極32A,32Bの頂面上には、導電性を有する保護層35A,35Bが形成されており、各ゲート電極用コンタクトプラグ44A,44Bは、保護層35A,35Bを介して、各ゲート電極32A,32Bの頂面に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ダマシンゲート技術等を用いてゲート電極が作製される半導体装置において、半導体装置の微細化等を可能にする。

【解決手段】 N型MISトランジスタ及びP型MISトランジスタそれぞれのゲート電極が半導体基板に形成された凹部内にゲート絶縁膜を介して形成されている半導体装置であって、N型MISトランジスタ及びP型MISトランジスタの一方のゲート電極は第1の金属含有膜F1及び第1の金属含有膜上の第2の金属含有膜F2の積層構造によって構成され、N型MISトランジスタ及びP型MISトランジスタの他方のゲート電極は第3の金属含有膜F3及び第3の金属含有膜上の第2の金属含有膜F2の積層構造によって構成されている。

(もっと読む)

半導体装置の製造方法

【課題】素子構造部にダメージを与えずに側壁スペーサ膜等を除去し、高集積化された高性能な半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】被処理基体上にGeCOHまたはGeCHからなる第1の薄膜を形成すると、この第1の薄膜の一部を除去する工程と、第1の薄膜の除去された部位を介して被処理基体に所定の処理を施す処理工程と、第1の薄膜を除去する工程とを備えたことを特徴とする。GeCOHまたはGeCHからなる側壁スペーサ膜30を用い、ソース、ドレイン領域形成処理を行った後、これを除去する。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】GaN層3上に形成された第1の半導体層4上の一部の領域に無機膜5を形成すると共に、無機膜5を介して相互に対向する領域に電極6及び7を形成する。第1の半導体層4はAlGaN層とする。次に、第1の半導体層4上における無機膜5と電極6とに挟まれた領域、及び無機膜5と電極7とに挟まれた領域の各々に、第2の半導体層8を形成する。第2の半導体層8としては、MOCVD法によりAlGaN層を形成する。その後、無機膜5を除去し、凹み9を形成する。次に、絶縁膜10を形成し、凹み9内に電極11を形成する。これにより、半導体装置19が作製される。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート長の異なるMISFET間のしきい値のばらつきを抑制した半導体装置及びその製造方法を提供すること。

【解決手段】 半導体基板100の第一及び第二領域112、113上にゲート絶縁膜103及びダミー層111を形成し、ダミー層111を加工して第一のダミーゲート114と第一のダミーゲート114よりゲート長の長い第二のダミーゲート115を形成。第一及び第二のダミーゲート114、115を利用してダミー絶縁層116を形成し、第一及び第二のダミーゲート114、115を除去してダミー絶縁層116に第一と第二の開口部117、118を形成し、第一の開口部117全体及び第二の開口部118の一部に第一の導電膜107を形成し、第二の開口部118に第一の導電膜107とは異なる仕事関数の第二の導電膜108を、第一領域112上に第一のMISFET105、第二領域113上に第二のMISFET106とを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】セル面積の縮小化とともに、シェアードコンタクト形成時のゲート電極側部に形成されたサイドウォールの膜減りによる半導体基板への突き抜けを防止する。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極13が形成され、その両側にサイドウォール15,16が形成され、ゲート電極13両側の半導体基板にソース・ドレイン17,18が形成されている半導体基板上に、ゲート電極13、ソース・ドレイン17,18等を被覆する犠牲膜23を形成する工程と、犠牲膜23にゲート電極13上から一方側のソース・ドレイン18上を開口するシェアードコンタクト24を形成する工程と、シェアードコンタクト24の内部にゲート電極13と一方側のソース・ドレイン18に接続する導電性プラグ26を形成する工程と、犠牲膜23を除去する工程とを備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】同一基板上において誘電率の異なる複数種類のゲート絶縁膜を必要性に応じて使い分けた半導体装置の構造、及び当該構造を実現する簡便な製造方法を提供する。

【解決手段】基板1の活性領域1a上に高誘電率ゲート絶縁膜4を介してゲート電極7Aが形成されている。基板1の活性領域1b上にゲート酸化膜6を介してゲート電極7Bが形成されている。ゲート電極7A及び7Bのそれぞれの側面に同一構造の絶縁性サイドウォールスペーサ8A及び8Bが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】FUSI電極を備え、歩留まり良く製造できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、ゲート長方向に所定の間隔で配置され、全体がシリサイド化されたゲート電極41aと、素子分離領域2上に設けられ、ゲート長方向に間隔Cを空けて配置され、間隔Bを空けてゲート電極41aに隣接する配線4aとを備えている。間隔Bおよび間隔Cは間隔A以下となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイド化されたゲート電極を有する半導体装置の製造方法において、活性領域と素子分離領域との段差による影響を受けることなく、活性領域上と素子分離領域上とに形成されたそれぞれのゲート電極形成膜及びゲート配線形成膜の露出を精度良う。

【解決手段】活性領域11を囲む素子分離領域12が形成された半導体基板10の上に形成された保護膜15a及び保護膜15bを覆うように下地保護膜19及び層間絶縁膜20を形成した後、化学機械研磨(CMP)法により、保護膜15aの上面が露出するまで、層間絶縁膜20、下地保護膜19及び保護膜15bを研磨除去する。

(もっと読む)

パターン形成装置および有機薄膜トランジスタの製造方法ならびに有機薄膜トランジスタ

【課題】基板上に形成された濡れパターンの検査を、簡易にかつ確実に実行する。

【解決手段】パターン形成装置は、同一のゲート電極パターンが多数規則的に形成された透明な基板にパターンを形成する。液膜塗布手段は、基板16に感光性撥液膜18を塗布可能である。露光装置10は、基板の裏面側に配置され基板上に塗布された撥液膜をゲート電極13に応じたパターンに形成する。滴下装置55は、露光手段が形成した撥液膜パターンを有する基板表面に検査液を滴下する。計測手段58は、滴下装置が滴下した液滴を検出する。検出手段が検出した液滴に応じて露光装置の形成した撥液膜パターンの良否を判断手段が判断する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】 窒化物半導体層に形成される制御電極のショットキ特性の向上、高耐圧化、周波数分散の抑制を可能とし、スレッショホールド電圧の制御が容易なノーマリーオフ動作を実現できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】 基板上に、第1の窒化物半導体層と微結晶構造からなる第2の窒化物半導体層を形成し、制御電極形成領域にマスク膜を形成する。マスク膜を用いて露出する第1の窒化物半導体層上に、第3の窒化物半導体層と微結晶構造からなる第4の窒化物半導体層を形成する。マスク膜を除去し、第2の窒化物半導体層上に制御電極を形成する。

(もっと読む)

半導体デバイス製造中の交互に行うスペーサ堆積を用いたピッチ縮小技術およびそれを含むシステム

一連の自己整合スペーサを用いて、最初のパターン層の上に形成されたフィーチャの密度を増加させる、層をパターンする方法。エッチング予定層が設けられ、その後、例えば光学的リソグラフィを用いて形成される最初の犠牲パターン層がエッチング予定層の上に形成される。実施形態に応じて、パターン層がトリミングされてもよく、その後一連のスペーサ層が形成され、エッチングされる。スペーサ層の数とその目標とする寸法は、フィーチャ密度の所望される増加率による。製造中の半導体デバイスと電子システムもまた説明される。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極を埋め込み形成する際の埋め込み特性を改善する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2を介して、第1ゲート電極層3aと第2ゲート電極層3bとをこの順に積層してなるゲート電極3を形成する半導体装置の製造方法であって、まず、半導体基板1上に、ゲート絶縁膜2と、ゲート電極3の仕事関数を規定する金属含有材料からなる第1ゲート電極層3aとをこの順に積層する工程を行う。次に、第1ゲート電極層3a上に、第1ゲート電極層3aに達する凹部8を有する絶縁層7を形成する工程を行う。次いで、凹部8に、第1ゲート電極層3aよりも抵抗値の低い金属含有材料からなる第2ゲート電極層3bを埋め込む工程を行う。その後、第2ゲート電極層3bをマスクとして、第1ゲート電極層3aをパターンニングする工程を行うことを特徴とする半導体装置の製造方法と半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CVD法により上部電極を成膜する際の下地層へのダメージを防止する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板11上の層間絶縁膜16に設けられた凹部17の内壁を覆う状態で、層間絶縁膜16上にゲート絶縁膜18を形成する工程と、ゲート絶縁膜18上に、仕事関数を制御する第1ゲート電極層19aを形成する第1工程と、第1ゲート電極層19a上に、下地層へのバリア性を有する第2ゲート電極層19bを形成する第2工程と、第2ゲート電極層19bが設けられた凹部17を埋め込む状態で、第2ゲート電極層19b上に、化学的気相成長法により、第1ゲート電極層19aよりも抵抗の低い第3ゲート電極層19cを形成する第3工程とを行うことを特徴とする半導体装置の製造方法と半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】キャリアの移動度に優れ、且つ、微細化への適用に優れた構造を有する半導体装置を提供する。

【解決手段】半導体装置は、素子分離領域11によって囲まれた第1の活性領域10aと、第1の活性領域10a上に形成され、且つ、素子分離領域11上に突き出している突き出し部を有する第1のゲート電極13aと、第1の側壁絶縁膜15a,16aと、第1のゲート電極13aの突き出し部とゲート幅方向に間隔をおいて形成された補助パターン13bと、第2の側壁絶縁膜15a,16aと、内部応力を持つ応力絶縁膜19とを備える。第1のゲート電極13aと補助パターン13bとの間隔は、第1の側壁絶縁膜15a,16aの膜厚と第2の側壁絶縁膜15a,16aの膜厚との和と、応力絶縁膜19の膜厚の2倍の値との合計値よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】不純物濃度を抑えることなくエピタキシャル成長層の端面での垂直成長面の発生を防止でき、これにより特性の優れた半導体装置を得ることが可能な製造方法を提供する。

【解決手段】ゲート電極脇の半導体基板上にエピタキシャル成長層からなるソース・ドレインを備えた半導体装置の製造方法であって、シリコンからなる半導体基板1上にゲート絶縁膜2aを介してゲート電極3aを形成し、ゲート絶縁膜2aおよびゲート電極3aの側壁にTEOSサイドウォール5を形成する。ゲート電極3aおよびTEOSサイドウォール5から露出された半導体基板1の表面層に対して、フッ酸ガスとアンモニアガスとを供給する処理とその後の熱処理とを行う表面ガスエッチング反応による前処理を行い、自然酸化膜6を除去する。その後、前処理された半導体基板1の露出表面上に、ソース・ドレインのエクステンション領域7をエピタキシャル成長させる。

(もっと読む)

半導体素子、半導体装置及びそれらの製造方法

【課題】チャネル領域の電位に対するゲート電極の制御性を向上させ、且つ電流駆動力が高くすることを可能にする。

【解決手段】半導体基板1に形成された、特定の導電型の不純物を含む半導体領域3と、半導体領域中に相互に向かい合う様に形成され、金属または金属と半導体領域をなす半導体との化合物を含むソースおよびドレイン領域4a、4bと、ソースおよびドレイン領域と、ソース領域とドレイン領域との間の半導体領域を覆うとともにソースおよびドレイン領域のそれぞれの一部を覆うように形成された絶縁膜5と、絶縁膜上に形成されたゲート電極6と、を有し、ソースおよびドレイン領域間の半導体領域の少なくとも一部の領域上に於ける絶縁膜とゲート電極との界面は、ソースおよびドレイン領域と半導体領域との接合部の上に於ける絶縁膜とゲート電極との界面よりも半導体領域側に存在する。

(もっと読む)

フィンを有する半導体デバイスの形成方法及びその構造

半導体デバイスの形成方法は、半導体層(12)を提供する工程、側壁を備える開口部(24)を有するパッシベーション層(20)を前記半導体層の上に形成する工程、前記半導体層の上にフィン(16)を形成し、前記パッシベーション層の形成後に前記フィンを前記開口部内に配置する工程、及び、前記開口部内にゲートの一部分を形成する工程を含む。一実施形態において、ダミーゲート(52)が用いられる。一実施形態において、スペーサ(28,56)が前記パッシベーション層の開口部内に形成される。更にその構造が説明される。  (もっと読む)

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、半導体基板の主表面側の下地領域 350に形成された凹部351内全体にシリコン窒化膜352を形成する工程と、前記シリコン窒化膜352を酸化して該シリコン窒化膜352をシリコン酸化膜353に変換することにより、前記凹部内全体に絶縁領域を形成する工程とを有することを特徴とする。

(もっと読む)

161 - 180 / 293

[ Back to top ]