Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

81 - 100 / 293

半導体装置の製造方法および半導体装置

【課題】製造安定性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板13上にゲート絶縁膜21を設ける工程、ゲート絶縁膜21のnMOSトランジスタ形成領域を除いた領域にTa等を主成分とする第一の金属膜22を形成する工程、ゲート絶縁膜21、第一の金属膜22を覆うようにポリシリコン膜を形成する工程、ゲート絶縁膜21、ポリシリコン膜をエッチングにより選択的に除去し第一のダミーゲート電極を形成し、ゲート絶縁膜21、第一の金属膜22、ポリシリコン膜を選択的に除去し第二のダミーゲート電極を形成する。各ダミーゲート電極を、側壁絶縁膜で埋め込み、各ダミーゲートの上部のポリシリコン膜を除去し、絶縁層に凹部を形成した後、凹部内に第二の金属膜を積層し、CMOSのゲート電極とする。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化された構造においても効果を発揮する歪みシリコン技術を適用した半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板中の前記ゲート絶縁膜下に形成されたチャネル領域と、前記チャネル領域の両側に形成された第1の層、および前記第1の層の下層に位置し、ゲート電極中央側の端部の位置が前記第1の層よりも前記ゲート電極中央に近い第2の層を含み、前記チャネル領域に歪みを発生させる歪み付与層と、前記チャネル領域の両側に、少なくとも一部が前記歪み付与層と重なるように形成されたソース・ドレイン領域と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】

歪み技術を用いたMOSトランジスタにおいて、リーク電流を抑える。

【解決手段】

半導体装置は、第1の格子定数を有する第1の半導体で形成された半導体基板に形成され、活性領域を画定する素子分離領域と、活性領域の中間位置を横断して、半導体基板上方にゲート絶縁膜を介して形成されたゲート電極と、ゲート電極側壁上に形成されたサイドウォールスペーサとを含むゲート電極構造と、ゲート電極構造両側の活性領域と素子分離領域との界面が半導体基板の表面に表出した境界の一部を覆って半導体基板の表面上方に配置された他のゲート電極構造であって、他のゲート電極と該他のゲート電極の側壁上に形成された他のサイドウォールスペーサとを含む他のゲート電極構造と、ゲート電極構造と他のゲート電極構造の間の活性領域をエッチして形成されたリセスと、リセスを埋めてエピタキシャル成長され、第1の格子定数と異なる第2の格子定数を有する第2の半導体で形成された半導体層と、を有する。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置の製造方法

【課題】チャネル領域のゲート幅方向に与える応力を移動度が向上する方向に働かすとともに、ソース・ドレイン領域表面にシリサイド層を形成した際のリークを防止する。

【解決手段】半導体基板11に素子形成領域12を挟み、半導体基板11に埋め込まれるように素子分離領域13を形成する工程と、素子形成領域12上にそれを横切るようにダミーゲート52を形成する工程と、ダミーゲート52の両側の素子形成領域12にソース・ドレイン領域の接合位置が素子分離領域13の表面より深い位置にしてソース・ドレイン領域27、28を形成する工程と、半導体基板11上にダミーゲート52の表面を露出させて第1層間絶縁膜42を形成する工程と、ダミーゲート52を除去して溝29を形成する工程と、溝29内の素子分離領域13の上部を除去する工程と、溝29内の半導体基板11上にゲート絶縁膜21を介してゲート電極22を形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】MISトランジスタを有する半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面上に半導体層を積み上げて形成された一対のソース・ドレイン領域sdn,sdpと、その側壁を覆う側壁絶縁膜ISと、側壁絶縁膜ISに平面的に挟まれた位置のシリコン基板1の主面上に、ゲート絶縁膜IGを隔てて配置されたゲート電極GEと、ゲート電極GEの側方下部からソース・ドレイン領域sdn,sdpの側方下部に渡って形成されたエクステンション領域exn,expとを有する半導体装置であって、ソース・ドレイン領域sdn,sdpの側壁は順テーパ状の傾斜を有しており、側壁絶縁膜ISの側壁のうち、ゲート絶縁膜IGおよびゲート電極GEと隣り合う方の側壁は、順テーパ状の傾斜を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

二重仕事関数半導体デバイスの製造方法及びそのデバイス

【課題】金属ゲート電極を有する二重仕事関数半導体デバイスの製造方法を提供する。

【解決手段】該製造方法は、第1領域101及び第2領域102を有する基板100を設けること、第1領域に第1半導体トランジスタ107を作製すること、第2領域に第2半導体トランジスタ108を作製すること、第1サーマルバジェットを第1半導体トランジスタに備わる少なくとも第1ゲート誘電体キャッピング層114aに作用し、第2サーマルバジェットを第2半導体トランジスタに備わる少なくとも第2ゲート誘電体キャッピング層114bに作用すること、を備える。

(もっと読む)

半導体装置、およびその製造方法

【課題】良好な形状のキャップ層を形成して、容易に適した仕事関数に制御することができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、high−k膜2および第1のゲート電極膜3が積層したゲートパターンが形成されるとともに、ゲートパターンをマスクとして、第1導電型および第2導電型のソース・ドレイン領域12を形成する。次に、ゲートパターンの周囲を含む全面に層間絶縁膜14を形成する。次に、第1導電型のMISFET形成領域8の第1のゲート電極膜を除去して溝部20aを形成する。次に、溝部20aの底面および側面を含む全面に積層するようにキャップ層15を形成する。次に、溝部20aを埋め込むように第2のゲート電極膜16を形成する。次に、第2導電型のMISFET形成領域9の第1のゲート電極膜3の表面が露出するように除去しキャップ層15を拡散する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、ゲート構造の劣化を抑制した半導体装置の製造方法および半導体装置を提供することを目的とする。

【解決手段】本発明の一実施形態による半導体装置の製造方法は、Si基板1上にゲート絶縁膜3およびSiN4を積層して仮ゲートパターンを形成し、Si基板1に一部が埋め込まれたソース5およびドレイン5を仮ゲートパターンを挟んで離間して形成し、ソース5、ドレイン5、およびSiN4上にSiO24を形成し、SiO24を平坦化しSiN4を除去して形成されたゲート開口部の側面にSiN8を形成し、ゲート開口部にゲート電極材料9を埋め込むことを特徴とする。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

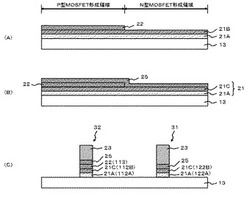

半導体装置の製造方法および半導体装置

【課題】半導体装置の製造安定性を向上させる。

【解決手段】半導体装置100においては、シリコン基板101にメモリ領域とロジック領域が混載されている。メモリ領域においてシリコン基板101に溝部111が設けられ、メモリ領域にメモリセルトランジスタ120が設けられるとともにロジック領域にロジックトランジスタ130が設けられる。メモリセルトランジスタ120は金属材料により構成された第一ゲート電極115を含む。第一ゲート電極115は溝部111に埋設されるとともに溝部111の外部に突出して設けられる。ロジックトランジスタ130は第一ゲート電極115と同一材料により構成された第二ゲート電極127を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】精度良く形成された第1,第2のゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現する。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート電極脇の材料層の後退が防止され、これによって特性の向上が図られた半導体装置を提供する。

【解決手段】半導体基板1上に溝パターンaを有して設けられた絶縁膜100と、溝パターンaの内壁を覆う状態で設けられたゲート絶縁膜9と、ゲート絶縁膜9を介して溝パターンa内を埋め込むと共に、絶縁膜100上における溝パターンaの両側に溝パターンaよりも幅広に張り出して形成されたゲート電極101とを備えたことを特徴とする半導体装置104。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗をさらに低減する疑似SOI構造の半導体装置の提供。

【解決手段】第1および第2のゲート側壁絶縁膜23WA〜23WDをマスクに、前記側壁絶縁膜のそれぞれ外側に、第1および第2の凹部21TA〜21TDを形成する工程と、前記側壁絶縁膜のそれぞれ外側に、第1および第2のダミー側壁膜を形成する工程と、前記ダミー側壁膜23DA〜23DDをマスクに、前記シリコン基板のうち、前記凹部における露出部分を酸化し、それぞれ第1および第2のシリコン酸化膜を形成する工程と、前記凹部に第1および第2のシリコン膜を充填する工程と、前記シリコン膜上に金属膜を堆積し、熱処理することにより、シリサイド領域が側壁絶縁膜の外端を超えて、前記ゲート電極23A,23B直下の領域近傍にまで到達するようにシリサイド領域を形成する工程と、を含む。

(もっと読む)

固体撮像装置およびその製造方法

【課題】画素アレイ部のトランジスタの領域にシリサイドを形成しない場合においてゲート電極の抵抗を低減する。

【解決手段】周辺回路部11を構成するトランジスタの領域にはシリサイド層140を形成する。画素アレイ部10のフォトダイオードおよびトランジスタの領域にはシリサイド層140を形成しないが、トランジスタのゲート電極122_10 は金属材で形成する。その製法としては、画素アレイ部10および周辺回路部11にフォトダイオードやトランジスタを形成した後、画素アレイ部のトランジスタの領域にはシリサイドが形成されないように窒化シリコンなどで覆って、周辺回路部11を構成するトランジスタの領域にシリサイド層140を形成する。その後、画素アレイ部10のトランジスタのゲート電極122_10 部分に存在していた電極材を金属材に置換する。

(もっと読む)

半導体装置

【課題】MIS型半導体装置やMS型半導体装置において、簡便な手法により半導体層の界面準位を所望のエネルギー準位に設定することが可能な半導体装置を提供する。

【解決手段】導電体と、ソース領域とドレイン領域とを有する半導体と、前記ソース領域と前記ドレイン領域との間において、前記導電体と前記半導体とにそれぞれ接して前記導電体と前記半導体との間に設けられた単分子層と、を備え、前記半導体と前記単分子層との界面において、前記単分子層を構成する分子の電子準位が前記半導体のバンドギャップ内に状態密度の極大を形成してなることを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】組成の安定したゲート電極を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11に、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、ストッパ膜25、及びシリコン材料膜23bを順に有する第1の積層膜を備えたpMOS領域1、離間して、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、及びシリコン材料膜23bを順に有する第2の積層膜を備えたnMOS領域2を形成し、第1及び第2の積層膜の側壁にオフセット膜33、サイドウォール35の形成、及びソース・ドレイン領域15の形成を行い、pMOS領域1のシリコン材料膜23b及びストッパ膜25を除去し、シリコン材料膜23a上、及びnMOS領域2のシリコン材料膜23b上にNiを堆積し、pMOS領域1にNi3Siを形成し、nMOS領域2にNiSi2を形成する。

(もっと読む)

ダミーゲートパターンを備える半導体装置

【課題】ダミーゲートパターンを用いてゲートパターンの寸法精度の向上を図り、かつ回路動作の高速化が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板上に形成された拡散層10と、拡散層10の上部に配置され、MOSトランジスタのゲート電極として機能するゲートパターン11と、拡散層10の上部においてゲートパターン11と一定の間隔で隣接して配置されゲート電極として機能しないダミーゲートパターン13とを備え、ゲートパターンの疎密の程度が均一に保たれる。ダミーゲートパターン13は、拡散層10の上部におけるゲート幅方向の所定位置で切断され、切断部13aの直下で抵抗を低減して高速なMOSトランジスタの動作を実現する。

(もっと読む)

81 - 100 / 293

[ Back to top ]