Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

21 - 40 / 293

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

金属ゲート電極を有する半導体素子の製造方法

【課題】 収率が低下することなくCMOS集積回路の特性を最適可能な半導体素子の製造方法を提供する。

【解決手段】 半導体基板1の上の第1領域A内及び第2領域B内に各々形成された第1グルーブ15a及び第2グルーブ15bを有する層間絶縁膜15を形成する。次に、半導体基板1上に積層金属膜22を形成し、積層金属膜22上に非感光性を有する平坦化膜23を第1グルーブ15a及び第2グルーブ15bを充填するように形成する。第1領域A内の平坦化膜23を乾式エッチングによって選択的に除去し、第1領域A内の積層金属膜22を露出させ、第2領域B内の積層金属膜22を覆う平坦化膜パターン23pを形成する。これにより、第1領域A内の最上部金属膜を容易に除去することができるので、収率が低下することなく異なる仕事関数を有する第1金属ゲート電極及び第2金属ゲート電極を形成できる。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

半導体装置の製造方法

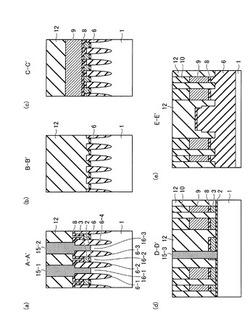

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11上に、ダミーゲート電極及びダミーコンタクトプラグの側面を覆う層間絶縁膜16を形成後、ダミーゲート電極、ダミーコンタクトプラグを選択的に除去して、ゲート電極形成用溝17及びコンタクト孔18を同時に形成し、次いで、ゲート電極形成用溝17内、コンタクト孔18内、及び層間絶縁膜16の上面を覆う高誘電率絶縁膜42を成膜し、次いで、斜めイオン注入法により、ゲート電極形成用溝17の下部17Aに形成された高誘電率絶縁膜42にイオン注入しないように、高誘電率絶縁膜42を介して、半導体基板に不純物拡散領域15を形成し、次いで、イオン注入された高誘電率絶縁膜42を選択的に除去することで、ゲート電極形成用溝の下部にゲート絶縁膜を形成し、かつコンタクト孔から不純物拡散領域15の上面を露出させる。

(もっと読む)

半導体装置及びその製造方法

【課題】接続不良の発生を抑制することのできる、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、所定ピッチで所定の幅の素子領域が形成された半導体基板と、半導体基板上に積層された層間絶縁膜と、層間絶縁膜の上面から半導体基板の素子領域にかけて設けられ素子領域に接続される第1コンタクトとを備える。第1コンタクトは、素子領域上の層間絶縁膜に形成された素子領域の幅よりも大きい径を有するコンタクトホールと、コンタクトホールの底部に設けられ、素子領域に達する開口を有するスペーサ膜と、スペーサ膜の開口を介して素子領域に接続されるようにコンタクトホール内に埋め込まれたコンタクトプラグとを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電材料のゲートトレンチへの埋め込みが容易な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上の絶縁膜と、絶縁膜に設けられた凹部と、凹部の底部であって半導体基板上に設けられたゲート絶縁膜とを形成する工程と、凹部の内壁面上と絶縁膜の上面上に、第1金属を含む導電材料で第1ゲート電極膜を形成する工程と、第1ゲート電極膜上に、凹部の側面部分の一部は覆わないように、導電材料の融点よりも高い融点を持つ材料でカバー膜を形成する工程と、カバー膜が形成された状態で、熱処理を行って、第1ゲート電極膜をリフローさせる工程とを有する。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

21 - 40 / 293

[ Back to top ]