Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

141 - 160 / 293

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

半導体装置の製造方法

【課題】被覆率としては従来と変わることなく、かつシリコン酸化膜との間で選択比の取れるシリコン窒化膜を有する半導体装置の製造方法を提供することにある。

【解決手段】半導体基板の主表面上に層間絶縁膜を形成する工程と、前記層間絶縁膜に前記半導体基板の主表面に達するコンタクトホールを形成する工程と、前記側壁にシリコン窒化膜が形成されたコンタクトホール内にTi層およびTiN層を有するバリアメタル層を形成する工程と、前記バリアメタル層が形成されたコンタクトホール内に導電層を形成する工程と、SinCl2n+2とNH3との混合ガス、またはSinCl2n−2−xとNH3との混合ガスを用い(nは2以上の自然数、xは2n+2以下の自然数)、700℃以下の成膜温度で、前記コンタクトホール内の導電層上に塩素を含有するシリコン窒化膜を形成する工程とを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

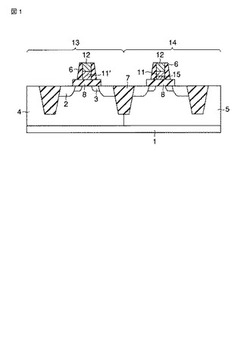

【課題】ダマシン型ゲートあるいはリプレース型ゲートを有する半導体装置において、ゲートパターン密度の偏りを小さくし、ダミーゲートの上面を露出させるCMP工程において、ディッシングが発生しないようにする。

【解決手段】ダマシン型ゲートあるいはリプレース型ゲートを有する半導体装置において、ゲート形成位置以外の位置14に、ダミーゲート12aを追加して配置することにより、ゲートパターン密度の偏りを小さくする。あるいはダミーゲート12aの代わりにインターフェーストランジスタ、あるいはアナログ回路用容量の電極を配置することにより、ゲートパターン密度の偏りを小さくする。

(もっと読む)

半導体装置

【課題】トランジスタのサイズによらない普遍的な引っ張り歪みをnチャネル型MOSトランジスタに印加できる半導体装置を提供する。

【解決手段】nチャネル型MOSトランジスタのゲート絶縁膜として、高誘電率絶縁膜を使用し、この高誘電率絶縁膜を半導体基板上に界面層を介さず直接形成することにより、チャネル領域に引張り歪を与える。チャネル領域に圧縮歪を有するpチャネル型MOSトランジスタと組み合わせることにより、相補型の高性能半導体装置を構成できる。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート電極の上方にコンタクトプラグを形成するときに、ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13及びチャネル形成領域12、ゲート電極23、並びに、ゲート絶縁膜30を備えており、ゲート絶縁膜30は、ゲート電極23とチャネル形成領域12との間に形成されたゲート絶縁膜本体部30A、及び、ゲート絶縁膜本体部30Aからゲート電極23の側面部23Aの途中まで延在するゲート絶縁膜延在部30Bから構成されており、チャネル形成領域12の表面を基準としたゲート電極23の高さをHGate、ゲート絶縁膜延在部30Aの高さをHInsとしたとき、HIns<HGateを満足する。

(もっと読む)

半導体装置およびその製造方法

【課題】金属とシリコンおよび/またはゲルマニウムを必須として含む金属半導体化合物をゲート電極とする金属絶縁膜半導体電界効果トランジスタを利用した半導体装置において、ゲート絶縁膜やチャネル等によらずに複数の閾値電圧を設定する。

【解決手段】半導体装置が、MAxで表される組成を有する第1のゲート電極を含む第1のトランジスタと、MAyで表される組成を有する第2のゲート電極を含む第2のトランジスタを少なくとも含むMIS電界効果トランジスタを含む(式中、MはW、Mo、Ni、Pt、Ta、Pd、Co、およびTiからなる群より選択される少なくとも1種の金属元素であり、Aはシリコンおよび/またはゲルマニウムであり、0<x≦3、および0<y≦3であり、xとyは異なる)。

(もっと読む)

半導体装置の製造方法

【課題】フルシリサイドゲート電極を有し、電気特性に優れたCMOSデバイスを容易に製造することが可能な半導体装置の製造方法を得る。

【解決手段】半導体基板における第1の導電型の領域上の高誘電率ゲート絶縁膜上に第1のポリシリコンゲート電極を、第2の導電型の領域上の高誘電率ゲート絶縁膜上に第2のポリシリコンゲート電極を形成する工程と、シリサイド化反応を抑制するシリサイド化反応抑制金属の元素を第2のポリシリコンゲート電極には注入せずに第1のポリシリコンゲート電極に注入する工程と、シリサイド化反応抑制金属の元素の注入後に、シリサイド化する金属の膜を少なくとも第1および第2のポリシリコンゲート電極上に形成する工程と、金属の膜を形成した半導体基板を熱処理して第1および第2のポリシリコンゲート電極をシリサイド化させてそれぞれをフルシリサイド電極とする熱処理工程と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】研磨工程などを削減するとともに素子分離領域の上に微細なゲートスペースパターンを有する。

【解決手段】半導体装置は、半導体基板100と、素子分離絶縁膜101と、第1および第2電極107a,107bと、ゲート絶縁膜パターン104と、側壁絶縁膜108とを備えている。素子分離絶縁膜101は半導体基板100の上に設けられており、第1および第2電極107a,107bはゲート絶縁膜パターン104を挟むようにして素子分離絶縁膜101の上に設けられている。側壁絶縁膜108は、第1および第2電極107a,107bの側面のうちゲート絶縁膜パターン104に接している部分以外の部分に設けられている。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置及びその製造方法

【課題】安定した特性が得られる半導体装置及びその製造方法を提供する。

【解決手段】シリコン酸化膜と、前記シリコン酸化膜の上に設けられ、前記シリコン酸化膜よりも誘電率が高い金属シリケート絶縁膜と、前記金属シリケート絶縁膜の上に設けられたゲート電極と、を備え、前記金属シリケート絶縁膜における、前記ゲート電極と接する側の金属元素の組成比率が、前記シリコン酸化膜と接する側の金属元素の組成比率よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】基板1の表面の全面には、エピタキシャル結晶成長層2が配置されている。エピタキシャル結晶成長層2内においては、表面付近の一部の領域に第2導電型領域3が配置されている。第2導電型領域3内においては、表面付近の一部の領域に第1導電型領域4が配置されている。エピタキシャル結晶成長層2において、ゲート電極7が配置されている領域の一部は、表面にバンチングステップが形成されない平滑な第1領域となっており、ゲート電極7が配置されていない領域の全部は、表面にバンチングステップが形成された第2領域となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】シリコンゲート電極のシリサイド化に際し、電極の体積膨張に起因するゲートの側壁絶縁膜の破壊を防止する。

【解決手段】電極シリコン層のパターニング、ゲート電極のための第1及び第2側壁絶縁膜210、220の形成、及び、電極シリコン層及び側壁絶縁膜210、220と自己整合的なソース・ドレイン拡散領域103へのイオン注入を行った後に、電極シリコン層に接する第1の側壁絶縁膜210を、底部付近の一部を残してエッチング除去して、電極シリコン層の側面に空隙211を形成する。その後、金属層を堆積し、電極シリコン層のシリサイド化を行って、電極シリサイド層121を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板とは格子定数の異なる半導体層からチャネル部に対して効果的に応力を印加することが可能でこれによりキャリア移動度の向上を図り高機能化の達成が可能な半導体装置を提供する。

【解決手段】半導体基板3上にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇において半導体基板3の表面を掘り下げた部分にエピタキシャル成長によって形成された半導体層(応力印加層)9とを備えた半導体装置1において、半導体層9は、半導体基板3とは格子定数の異なる層であり、ゲート絶縁膜5およびゲート電極7は、半導体層9間において半導体基板3の表面を掘り下げた部分を埋め込む状態で設けられている。半導体基板3の表面に対するゲート絶縁膜5の深さ位置d2は、半導体層9の深さ位置d1よりも浅いこととする。

(もっと読む)

半導体装置の製造方法

【課題】特定の領域毎に同一材料を用いて異なる品質の半導体要素を作り分ける。

【解決手段】素子分離2及びウェル3,4が形成されたシリコン基板1表面にゲート酸化膜5を形成し、ゲート酸化膜5上にゲート電極7を形成する。ゲート電極7を挟むシリコン基板1上層に、エクステンション用の浅い拡散層8を形成する。NMOS領域を覆うように反射膜28を形成した後、光源から可視光を照射することにより、PMOS領域にソース/ドレイン領域10aを形成する。反射膜28を除去した後、光源から可視光を再度照射することにより、ソース/ドレイン領域10aとは異なる品質のソース/ドレイン領域がNMOS領域に形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】簡便かつ低コストにプレーナ領域と混載することが可能なフィン型電界効果トランジスタを含んだ半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板10の主表面にライン状の絶縁膜を形成し、絶縁膜をマスクに基板をエッチングして絶縁膜の両側に第1の溝を形成し、第1の溝それぞれの側壁に側壁絶縁膜を形成し、絶縁膜及び側壁絶縁膜をマスクに基板をエッチングして第1の溝の底部それぞれに第2の溝を形成し、絶縁膜及び側壁絶縁膜を耐酸化性マスクとして基板を酸化して第2の溝の基板を挟んで隣接する側壁それぞれに形成される酸化領域16を互いに接触させ、絶縁膜及び側壁絶縁膜を除去し、除去によって露出した基板の半導体領域18の表面にゲート絶縁膜21を、その上にゲート電極24を形成し、半導体領域をライン状のフィンとするフィン型電界効果トランジスタを形成する工程を含む。

(もっと読む)

半導体装置の製造方法及びトランジスタの製造方法

【課題】溝の埋め込み性を改善することと、溝の埋め込み高さを確保することを両立させることができる半導体装置の製造方法を実現する。

【解決手段】半導体装置の製造方法として、半導体基板1上の層間膜2に幅の異なる溝3,4を形成する工程と、溝3,4が形成された層間膜2上にバリアメタル層5を形成する工程と、バリアメタル層5を覆いかつ溝3,4の形成部位に開口部を有するレジストマスク7を形成する工程と、レジストマスク7を用いてバリアメタル層5をエッチングすることによりオーバーハング部6を除去する工程と、レジストマスク7を除去した後、半導体基板1上で溝3,4に配線材料を埋め込む工程と、半導体基板1上で配線材料とバリアメタル層5の余剰部を研磨により除去する工程とによって溝配線を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】混晶層中のGe濃度およびC濃度の許容範囲内で、チャネル領域に十分に応力を印加することが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】Si基板1上にダミーゲート電極3を形成する。次に、ダミーゲート電極3をマスクにしたリセスエッチングにより、リセス領域7を形成する。次いで、リセス領域7の表面に、SiGe層からなる混晶層8をエピタキシャル成長させる。続いて、ダミーゲート電極3を覆う状態で、混晶層8上に、層間絶縁膜12を形成し、ダミーゲート電極3の表面が露出するまで、層間絶縁膜12を除去する。ダミーゲート電極3を除去することで、層間絶縁膜12にSi基板1を露出する凹部13を形成する。その後、凹部13内にゲート絶縁膜14を介してゲート電極15を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】特性のばらつきや劣化を低減できる半導体装置の製造方法を提供する。

【解決手段】オフセットスペーサ用材料として、HfSiOを堆積した後に、表面を窒化させることで、シリコン基板10およびゲート構造を覆うようなHfSiON膜15を形成する。次に、HfSiON膜15に、異方性ドライエッチングを行うことにより、シリコン基板10およびゲート電極層14の上面に沿った領域のみにダメージを大きく与える。次に、濃度が5%程度のフッ酸水溶液で90秒程度の洗浄を行うことにより、HfSiON膜15のうちダメージが大きく与えられた領域のみが選択的にウェットエッチング除去される。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上に、ゲート絶縁膜及びゲート電極を設け、それらの側面にダミー側壁を形成し、その周囲を層間絶縁膜で囲み、前記ゲート電極及びダミー側壁の上面が露出する構造を提供する工程と、

前記ダミー側壁を除去して空洞を形成する工程と、

前記空洞内を側壁材料で埋め、側壁を形成する工程と

を具備する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上にダミーゲート層を形成する工程と、前記ダミーゲート層の側面に、ダミーゲート層を構成する材料との間で、エッチング選択性を有する側壁絶縁膜を形成する工程と、全面に層間絶縁膜を堆積する工程と、前記層間絶縁膜を、前記ダミーゲート層の上面が露出するまで除去する工程と、前記ダミーゲート層を除去し、溝を形成する工程と、前記溝の底面にゲート絶縁膜を形成する工程と、底面にゲート絶縁膜が形成された前記溝内にゲート電極を形成する工程とを具備することを特徴とする。

(もっと読む)

141 - 160 / 293

[ Back to top ]