Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

61 - 80 / 293

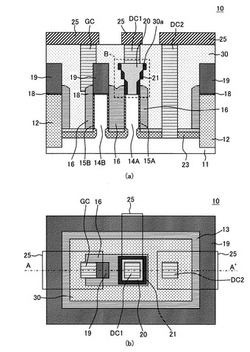

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

製造制御装置及び製造制御方法

【課題】膜厚変動を抑制することにより、トランジスタ特性のばらつきを低減できる製造制御装置及び製造制御方法を提供する。

【解決手段】第1半導体ウェハ上に絶縁膜を堆積する成膜装置30を制御する制御パラメータ(堆積時間ttarget)を算出する製造制御装置20であって、第2半導体ウェハの第2ウェハ表面積L1が大きいほど、成膜装置30に絶縁膜を厚く堆積させる制御パラメータ(堆積時間ttarget)を算出する。また、製造制御装置20は、第2ウェハ表面積L1が大きいほど堆積時間ttargetが長くなるように堆積時間ttargetを算出する堆積時間算出部116を備えてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

半導体装置

【課題】半導体デバイスに対する多様な要求に対し、柔軟に対応することができる半導体デバイスを提供する。

【解決手段】基板(2)と、ゲート絶縁膜(6)を介して基板(2)の上に設けられるゲート電極(3)と、ゲート電極(3)に隣接して配置されるサイドウォール(5)とを具備する半導体装置(1)を構成する。ゲート電極(3)は、引き出し電極部分(3−2)と実効ゲート電極部分(3−1)とを備えることが好ましい。また、引き出し電極部分(3−2)は、第1方向に沿って延伸する素子分離(9)の上に形成され、第1方向に沿った第1側面(16)(17)を有する部分とする。実効ゲート電極部分(3−1)は、素子分離(9)で分離される領域の上に形成され、第1側面(16)(17)を含む面に交差する面に沿った第2側面を有する部分とする。サイドウォール(5)は、第1側面(16)(17)を覆うことなく第2側面を覆うものとする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】n型MOSトランジスタ、p型MOSトランジスタにおいて共通のゲート絶縁膜構造及びゲート電極材料を用いながら、各々のトランジスタのしきい値電圧を適正な値へ設定し、且つゲート絶縁膜における酸素欠損に伴う移動度の低下を抑制する。

【解決手段】メタルゲート電極及び高誘電率ゲート絶縁膜を用いた半導体装置の製造方法であって、n型半導体領域200及びp型半導体領域300上にそれぞれ、シリコン酸化物からなる第1のゲート絶縁膜、La,Al,Oを含む第2のゲート絶縁膜、Hfを含む第3のゲート絶縁膜を積層し、その上に金属膜からなるゲート電極を形成し、次いでp型半導体領域300上の、第1のゲート絶縁膜,第2のゲート絶縁膜,第3のゲート絶縁膜,及びゲート電極の積層構造を、水素拡散防止膜350で被覆した後、水素雰囲気で熱処理を施す。

(もっと読む)

二回のカット工程によって多結晶シリコンのライン端部短縮の問題を解決する方法

【課題】ゲートストリップを二回のカット工程によって端部を改善する製造方法の提供。

【解決手段】第1アクティブ領域40と、第2アクティブ領域42とを有する基板を提供するステップと、基板にゲート電極層を形成するステップと、第1ゲートストリップ60と、第1ゲートストリップに実質的に平行する第2ゲートストリップ62と、第1アクティブ領域と第2アクティブ領域の間に位置して、第1ゲートストリップと第2ゲートストリップに平行していないが、互いに接続する犠牲ストリップ66とを残すように、ゲート電極層をエッチングするステップと、第1ゲートストリップと第2ゲートストリップの一部を覆い、犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部を開口部に露出させる遮蔽部を形成するステップと、開口部に露出される犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部をエッチングするステップを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

電界効果型トランジスタを有する半導体装置

【課題】良好な絶縁性を確保しつつ極めて高い誘電率を有するゲート絶縁膜の機能と、空乏層が形成されることのない金属性のゲート電極の機能とを備え、ゲート電圧のチャネル領域への静電的支配力を可及的に大きくすることのできる半導体装置を提供することを可能にする。

【解決手段】第1導電型の第1半導体層12に離間して設けられた第2導電型の第1ソース領域12aおよび第1ドレイン領域12bと、第1ソース領域と第1ドレイン領域との間の第1半導体層に設けられる第1チャネル領域12cと、第1チャネル領域上に設けられたハーフメタル強磁性金属の第1ゲート電極60と、第1ソース領域に接続するように設けられたハーフメタル強磁性金属の第1ソース電極50aと、を備え、第1ゲート電極の磁化64cの向きが、第1ソース電極の磁化64aの向きと略反平行である。

(もっと読む)

半導体装置の製造方法

【課題】デュアルメタルゲート構造を有する半導体装置において、ゲート電極除去する工程において、ゲート絶縁膜に与える損傷を抑える。

【解決手段】 第1のトランジスタと第2のトランジスタとを備える半導体装置において、第1のトランジスタは、第1の仕事関数を有する第1の材料からなる第1のゲート電極と、第1のゲート絶縁膜とを含む。また、第2のトランジスタは、第2の仕事関数を有する第2の材料からなる第2のゲート電極と、第2のゲート絶縁膜とを含む。ここで、第1のゲート絶縁膜は、高誘電率膜と、第1の高誘電率膜上に形成された第1の絶縁膜とを含むものとする。第2のゲート絶縁膜においては、高誘電率膜上部に形成した第1の絶縁膜を、第1のゲート電極を除去した後に除去する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを高選択的に除去することのできる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造工程において、シリコン基板2上にゲート絶縁膜8を形成し、このゲート絶縁膜8上にダミーゲート32を形成する。ダミーゲート32の側面には、サイドウォール10を形成する。サイドウォール10の形成後、ダミーゲート32を被覆する第1絶縁層17を形成し、第1絶縁層17の表面がダミーゲート32の表面と面一となるように加工する。第1絶縁層17の加工後、ダミーゲート32に、ダミーゲート32とサイドウォール10とのエッチング選択比を確保可能なエッチング液を供給することにより、ダミーゲート32をウェットエッチングする。そして、ダミーゲート32のエッチングにより現れるゲート絶縁膜8上に、金属材料からなるゲート電極9を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

半導体装置の製造方法

【課題】加工精度を改善し、かつ厚い配線を得るための半導体装置の製造方法を提供することを課題とする。

【解決手段】絶縁性基板上に形成された導電性膜上に配線形成領域を覆う第1のフォトレジストパターンを形成する工程と、前記第1のフォトレジストパターンをマスクとする異方性エッチングにより前記導電性膜の上部を除去することで第1溝を形成する工程と、前記第1のフォトレジストパターンを除去した後、前記第1溝の底部の少なくとも一部が露出した開口を有する第2のフォトレジストパターンを形成する工程と、前記第2のフォトレジストパターンをマスクとする異方性エッチングにより前記第1溝の底部に露出する前記導電性膜の下部を少なくとも除去することで第2溝を形成する工程を備えることで、前記第1溝と第2溝に由来する配線分離溝と、前記配線分離溝により分離された配線とを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】複数のライン状のパターンの端部におけるレジストパターン倒れ等の加工プロセスの問題を回避する。

【解決手段】 半導体基板上に被パターニング部材を形成した後に、被パターニング部材をパターニングして、複数のライン状のパターンを並列に形成するとともにライン状のパターンの端部から所定間隔をもってライン状のパターンの長手方向と垂直な方向にダミーパターンを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置の性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11と、このSiC基板11上に形成されたAlGaN層13と、このAlGaN層13上にそれぞれ離間して形成されたソース電極15及びドレイン電極14と、これらのソース電極15、ドレイン電極14間に形成され、ソース電極15及びドレイン電極14に対して平行な開口部16を有する第1の絶縁膜17と、この第1の絶縁膜17の開口部16に形成されたゲート電極18と、このゲート電極18が形成された第1の絶縁膜17上に形成された第2の絶縁膜19と、この第2の絶縁膜19及びソース電極15上に形成され、ドレイン電極14側の端部201が、第2の絶縁膜19と離間したソースフィールドプレート電極20と、を具備する半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートラストプロセスの適用に際して、トランジスタのフリンジ容量及びゲート抵抗の低減と、実効的なゲート長の短縮を実現する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4を順に積層して形成する工程と、それらをパターン加工するとともに、第1のダミーゲート部3をゲート長方向Xで第2のダミーゲート部4よりも後退させることにより、ノッチ部6を形成する工程と、ゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4の側方に絶縁材料からなる側壁7を形成し、かつ当該絶縁材料でノッチ部6を埋め込む工程と、第1,第2のダミーゲート部3,4を除去して、当該除去部分の底部にゲート絶縁膜2及びノッチ部6を残す工程と、除去部分を導電材料で埋め込むことによりゲート電極を形成する工程とを有する。

(もっと読む)

61 - 80 / 293

[ Back to top ]