Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

41 - 60 / 293

半導体装置の製造方法

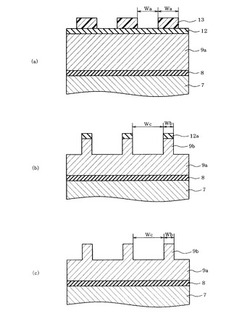

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】チップサイズを縮小化すること。

【解決手段】第1領域に形成される活性領域1と第2領域に形成されるウェル領域2とトランジスタゲート電極3とダミーゲート電極5と、コンタクト8とを備えている。活性領域1とトランジスタゲート電極3とは、トランジスタを形成している。トランジスタゲート電極3とダミーゲート電極5とは、互いに平行である複数の直線にそれぞれ沿うように形成されている。ダミーゲート電極5は、その第2領域とその第1領域との両方に配置されるように形成されている。コンタクト8は、その第2領域に形成され、ウェル領域2に同電位である配線層6にダミーゲート電極5を電気的に接続している。このような装置は、活性領域1とウェル領域2とが配置される領域のレイアウトサイズを小さくすることができ、その結果、チップサイズを縮小化することができる。

(もっと読む)

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

半導体装置、半導体チップ及び半導体装置の製造方法

【課題】製造工程中にピラー径の変動が小さいピラー型MOSトランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板対して垂直に立設する第1のピラー及び第2のピラーの側面にゲート絶縁膜を介して形成されたゲート電極と、第1のピラーの先端部及び基端周囲領域に形成された上部拡散層及び下部拡散層と、を備え、第2のピラーのゲート電極と隣接する第1のピラーのゲート電極とは接続されており、第1のピラーのゲート電極には第2のピラーのゲート電極を介して電位が供給され、第1のピラーと、該第1のピラーに隣接する第2のピラーの少なくとも一部とは平面視して、第1のピラー及び第2のピラーの側面を構成する面のうち、熱酸化速度及び/又はエッチング速度が最大の面に対して45°の方向に沿って配置されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

金属ゲートトランジスタ、集積回路、システム、およびその製造方法

【課題】金属ゲートトランジスタ、集積回路、システム、およびその製造方法を提供する。

【解決手段】半導体デバイスであって、第1MOS構造は、基板上に配置された第1ゲート誘電体、前記第1ゲート誘電体上に配置された第1仕事関数金属層、および前記第1仕事関数金属層上に配置された第1ケイ化物を含み、且つ第2MOS構造は、前記基板上に配置された第2ゲート誘電体、前記第2ゲート誘電体上に配置された第2仕事関数金属層、および前記第2仕事関数金属層上に配置された第2ケイ化物を含む半導体デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デバイス特性の制御性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】本実施の形態の半導体装置は、シリコン基板101上にMOSトランジスタを備える半導体装置であって、MOSトランジスタは、シリコン基板101上にゲート絶縁膜203を介して設けられたゲート電極(メタル電極206)と、ゲート電極(メタル電極206)の両脇の前記シリコン基板の表面近傍に設けられソース領域106およびドレイン領域109と、ソース領域106およびドレイン領域109に接するように、ゲート電極直下のシリコン基板101中に設けられた、チャネル領域(ゲルマニウム・カーボン単結晶膜202)と、を備え、チャネル領域が、シリコンと異なる異種半導体(ゲルマニウム)を含むものである。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置の製造方法

【課題】チャネルに大きな歪を生じさせることができ、制御を容易に行うことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、絶縁膜3、多結晶シリコン膜4及びアモルファスシリコン膜5を含む積層体を、ゲート電極の平面形状に形成する。多結晶シリコン膜4及びアモルファスシリコン膜5の側方にサイドウォール6を形成する。サイドウォール6をマスクとして半導体基板1の表面にp型不純物を導入して不純物導入領域7を形成する。サイドウォール6をマスクとして不純物導入領域7の表面に溝8を形成する。溝8内にSiGe層9を選択成長させる。アモルファスシリコン膜5を選択的に除去して、多結晶シリコン膜4を露出する。多結晶シリコン膜4上に導電層11を形成する。

(もっと読む)

置換ゲート構造体を有するFET及びその製造方法

【課題】 マルチゲート型FETの置換ゲート構造体及びマルチゲート型FETの置換ゲート構造体の製造方法を提供する。

【解決手段】 MUGFET及びMUGFETを製造する方法が示される。MUGFETを製造する方法は、複数の活性領域の周りに一時的スペーサ・ゲート(図3の16)を形成することと、複数の活性領域の間を含む、一時的スペーサ・ゲートの上に誘電体材料(18a及び空間20内)を堆積させることとを含む。この方法は、誘電体材料(空間20内)の部分をエッチングして一時的スペーサ・ゲート(16)を露出させることと、一時的スペーサ・ゲートを除去して、活性領域と誘電体材料の残りの部分(18a)との間に空間を残すこととをさらに含む。この方法はさらに、活性領域と誘電体材料の残りの部分(18a)との間の空間(22)及び誘電体材料の残りの部分の上方をゲート材料で充填することを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

41 - 60 / 293

[ Back to top ]