Fターム[4M104DD03]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | ダミーパターンの利用 (293)

Fターム[4M104DD03]に分類される特許

101 - 120 / 293

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲートラストプロセスで形成されたゲート構造において、ソース・ドレイン領域に接続するコンタクトとゲート電極とのショートを防ぐ。

【解決手段】半導体装置100は、ゲートラストプロセスで形成された第1のゲート210を含む。第1のゲート210は、絶縁膜中に形成された第1の凹部内の底面に形成されたゲート絶縁膜、当該第1の凹部内のゲート絶縁膜上に形成されたゲート電極、および当該第1の凹部内のゲート電極上に形成された保護絶縁膜140を含む。また、半導体装置100は、第1のゲート210の両側方のN型不純物拡散領域116aに接続され、第1の凹部よりも径が大きい第2の凹部内に埋め込まれたコンタクト134を含む。

(もっと読む)

半導体装置の製造方法

【課題】 金属ゲート電極への熱負荷を低減可能であるとともに、高誘電率ゲート絶縁膜に対する高温での熱処理が可能である半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に高誘電率ゲート絶縁膜及びダミーゲート電極を形成する工程と、少なくとも高誘電率ゲート絶縁膜及びダミーゲート電極をマスクとして半導体基板上にソース及びドレイン領域を形成する工程と、半導体基板上に層間絶縁膜を形成してその一部を除去することでダミーゲート電極上方を露出させる工程と、高誘電率ゲート絶縁膜上のダミーゲート電極を除去して溝を形成する工程と、溝の内部を被覆又は埋め込むように高誘電率ゲート絶縁膜上に金属ゲート電極を形成する工程と、を有する。

(もっと読む)

半導体素子及びその製造方法

【課題】LDD領域がゲート電極の下部とオーバーラップするのを防止し、素子のパフォーマンスを向上させるようにした半導体素子及びその製造方法を提供する。

【解決手段】STI領域及びゲート領域が定義された下部構造物において、前記STI領域の内部に素子隔離膜を、前記ゲート領域の内部に犠牲層を形成する段階と、前記素子隔離膜及び前記犠牲層をバリア(barrier)とし、前記素子隔離膜と前記犠牲層との間にLDD領域を形成する段階と、前記ゲート領域の内部に形成された前記犠牲層を選択的に除去する段階と、前記犠牲層が除去された前記ゲート領域の内部側壁にスペーサを形成する段階と、前記犠牲層が除去された前記ゲート領域の内部下側にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜の上部にゲート電極を形成する段階と、前記LDD領域の上部に接合領域を形成する段階と、前記LDD領域を前記ゲート領域の下部両側端まで拡散させる段階と、を含む。

(もっと読む)

導電体およびその製造方法

【課題】導電性および柔軟性の高い導電体及びその製造法の提供。

【解決手段】導電体100は、金属および導電性金属酸化物の少なくとも一方を含む第1導電層10と、第1導電層10の表面の少なくとも一部を覆う第2導電層20と、を有し、第2導電層20は、導電性高分子を含む。導電体100の製造方法は、凹凸パターンを有する版の凸部に、被転写層を形成する工程と、前記被転写層を基板に転写する工程と、を有し、前記被転写層を形成する工程は、前記版の凸部の上に導電性高分子を含む第1前駆体層を形成する工程と、前記第1前駆体層の上に、金属の前駆体および導電性金属酸化物の前駆体の少なくとも一方を含む第2前駆体層を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法、電子機器の製造方法、半導体装置および電子機器

【課題】半導体装置の特性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、第1基板(S1)上に、ゲート電極(15)を形成する工程と、第2基板(S2)の上部にソース、ドレイン電極(25s,25d)を形成する工程と、前記第1基板と第2基板とを絶縁材料よりなる接着材(35)を介して貼り合わせる工程であって、前記ゲート電極およびソース、ドレイン電極が、前記接着材中に埋め込まれるよう貼り合わせる接着工程と、前記第2基板を剥離することにより前記ソース、ドレイン電極および前記接着材表面を露出させる工程と、前記ソース、ドレイン電極および前記接着材表面上に有機半導体膜(45)を形成する工程と、を有する。かかる方法によれば、接着材等の表面の平坦性が向上し、有機半導体膜の成膜性を向上できる。また、ゲート絶縁膜となる前記接着材と有機半導体膜との界面が良好となる。

(もっと読む)

半導体装置の製造方法

【課題】いかなる位置に形成されたトランジスタに対してもダミーパターンを形成することを可能にして、トランジスタ特性の変動を抑制することを可能にする。

【解決手段】半導体基板11のアクティブ領域12上にゲート絶縁膜14を介して形成された複数のゲート電極15と、前記アクティブ領域12上の少なくとも前記ゲート電極15間の一部に形成されたダミーパターン16とを有し、前記ゲート電極15同士が隣接するゲート電極15−1、15−2間の間隔、および前記ダミーパターン16−1とそれと隣接する前記ゲート電極15−2、15−3との間隔が所定の範囲内となるように前記ダミーパターン16−1が形成されていることを特徴とする。

(もっと読む)

デバイスのパターニング

【課題】有機スイッチングデバイスまたは部分有機スイッチングデバイスを形成する方法である。

【解決手段】前記方法は、少なくとも1つのパターニング層を含む電気デバイスを基板上に形成する方法であって、前記基板上の第1の材料層を光ビームに露光して、前記第1の層の物理的特性を改変するように、前記第1の層のパターニングを行う工程を含み、前記光ビームの一部は、前記基板上の事前堆積されたパターンによってブロックまたは減衰され、これにより、前記光がブロックまたは減衰されない領域においてのみ前記基板上の第1の層を改変する、方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の注入量及びチャネル領域中の不純物濃度を容易に制御する。動作特性に優れたFin型電界効果型トランジスタを備えた半導体装置を提供する。

【解決手段】Fin状の半導体基板の部分に犠牲酸化膜を形成した後、マスクパターンをマスクに用いて半導体基板に不純物を注入する。この後、犠牲酸化膜を除去して、半導体基板を露出させた後、露出した半導体基板上にゲート絶縁膜を形成する。

(もっと読む)

相補型半導体装置及びその製造方法

【課題】 メタルゲート電極及び高誘電率ゲート絶縁膜を用いたn型MISトランジスタとp型MISトランジスタの双方において適正なしきい値電圧を得る。

【解決手段】 半導体基板30の表面部に形成された第1及び第2の半導体領域10,20と、第1の半導体領域10上に形成された、La及びAlを含む第1のゲート絶縁膜11及び第1のゲート電極12を有するn型MISトランジスタと、第2の半導体領域20上に形成された、La及びAlを含む第2のゲート絶縁膜21及び第2のゲート電極22を有するp型MISトランジスタと、を備えた相補型半導体装置であって、第2のゲート絶縁膜22における原子濃度比Al/Laが、第1のゲート絶縁膜11における原子濃度比Al/Laよりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソースドレイン部のシリサイド化およびゲート電極のフルシリサイド化を1回で行うとともに、CMP処理によるサイドウォールの後退を防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、SOI層3上にゲート絶縁膜4を介してゲート電極を形成し、ゲート電極両側のSOI層3上にエピタキシャル層9を形成する。ゲート電極を覆うCMPストッパ膜11を形成し、ゲート電極の側面においてCMPストッパ膜11上にサイドウォール12を形成する。エピタキシャル層9にソースドレイン部10,13を形成した後、これらの構造上にアモルファスシリコンからなる層間膜を形成し、CMPストッパ膜11表面に達するまで、CMP処理により層間膜を除去する。ポリシリコン膜の上部をエッチングした後、ゲート電極の全部と、ソースドレイン部10,13の上部とを同時にシリサイド化し、フルシリサイドゲート電極17を得る。

(もっと読む)

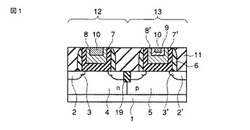

半導体装置

【課題】ゲート電極の形成後に酸化処理および酸化膜除去処理からなる洗浄処理が行われても、ゲート電極の表面が半導体層の表面よりも下がるのを防止することができる構造の半導体装置を提供する。

【解決手段】半導体装置1では、エピタキシャル層3の基層部がN−型領域4をなし、エピタキシャル層3には、そのN−型領域4に接して、P−型のボディ領域5が形成されている。ゲート絶縁膜7を介してゲート電極8が埋設されるトレンチ6は、エピタキシャル層3の表面から掘り下げて形成され、ボディ領域5を貫通して、その最深部がN−型領域4に達している。そして、ゲート電極8の表面は、耐酸化性のW膜28により被覆されている。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属元素を有する絶縁膜の界面特性を向上させる半導体装置の製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、下層、Ge層、Ge酸化物層、上層の順に積層された構造を形成する工程と、熱処理を用いてGe酸化物層及びGe層を除去して、上層と下層とを直接接合させる工程とを有し、上層及び下層の何れかは金属元素を有する絶縁物で形成されることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】コストを低減した半導体装置を提供する。

【解決手段】半導体基板100表面部にチャネル領域101を挟むように形成された拡散層102と、チャネル領域101上に形成されたゲート絶縁膜103を有し、N型MOSFETのゲート電極104は第1のニッケルシリサイド層104a及び第1のニッケルシリサイド層104a上に形成され第1のニッケルシリサイド層104aよりニッケル含有率が高い第2のニッケルシリサイド層104bからなり、P型MOSFETのゲート電極104は第2のニッケルシリサイド層104bよりニッケル含有率が高い第3のニッケルシリサイド層からなる。

(もっと読む)

半導体装置とその製造方法

【課題】絶縁膜を研磨せずに、該絶縁膜からゲート電極の上面を露出させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板1の上にゲート絶縁膜5を形成する工程と、ゲート絶縁膜5の上にゲート電極7aを形成する工程と、ゲート電極7aを覆うように液状の絶縁性材料20を塗布する工程と、絶縁性材料20に鋳型100を押し当てることにより、ゲート電極7aの上方の絶縁性材料20を押し流す工程と、絶縁性材料20を硬化して絶縁膜21にする工程と、硬化の後、ゲート電極7a上に高融点金属膜を形成する工程と、高融点金属膜をアニールすることにより、ゲート電極7aの全体をシリサイド化する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート形成溝内に埋め込んで形成される金属系ゲート電極を有するトランジスタ群と抵抗とを有する半導体装置で、抵抗値のばらつきをなくした抵抗形成を可能とする。

【解決手段】半導体基板11に、第1トランジスタ群と、これよりも低い動作電圧の第2トランジスタ群と、抵抗3とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介してシリコン系材料層71で形成された第1ゲート電極15を有し、第2トランジスタ群は、半導体基板11上の第1層間絶縁膜38に形成したゲート形成溝42内に第2ゲート絶縁膜43を介して金属系ゲート材料を埋め込むように形成された第2ゲート電極47、48を有し、抵抗3は、半導体基板11上に絶縁膜61を介してシリコン系材料層71と同一層で形成された抵抗本体部62と、この上部に形成された抵抗保護層63を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】異なる動作電圧のトランジスタ群を同一半導体基板に形成し、高電圧動作のトランジスタ群のゲート電極の低抵抗化を可能にし、低動作電圧のトランジスタ群の金属ゲート電極を形成するための導電膜の残査発生をなくすことを可能にする。

【解決手段】半導体基板11に、高動作電圧の第1トランジスタ群と、低動作電圧の第2トランジスタ群とを有し、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13、第1ゲート電極15、シリサイド層とが順に積層され、第2トランジスタ群は、半導体基板11上のダミーゲート18を除去してなるゲート形成溝42内に、第2ゲート絶縁膜と第2ゲート電極を有する半導体装置の製造方法において、第1ゲート電極15をダミーゲート電極16よりも低く形成してから上記シリサイド層を形成し、それらを被覆する層間絶縁膜を形成して表面を平坦化してから、ゲート形成溝を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】Pチャネル型トランジスタの閾値電圧を制御することができる半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】NTrとPTrとを含む半導体装置において、N型チャネル形成領域とP型チャネル形成領域とを有するN型半導体基板2上に絶縁膜Fが形成され、絶縁膜Fにゲート電極用溝A及びBとが形成され、ゲート電極用溝A及びBの内側表面上にゲート絶縁膜20が形成され、NTr領域におけるゲート絶縁膜20上にNTr仕事関数制御メタル膜21が形成され、NTr仕事関数制御メタル膜21及びゲート絶縁膜20上にフッ素がドープされたPTr仕事関数制御メタル膜23が形成され、PTr仕事関数制御メタル膜23の上層に、ゲート電極用溝に埋め込まれてゲート電極が形成されている構成とする。

(もっと読む)

101 - 120 / 293

[ Back to top ]