Fターム[4M104DD43]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | CVD (2,824)

Fターム[4M104DD43]の下位に属するFターム

Fターム[4M104DD43]に分類される特許

121 - 140 / 1,609

半導体装置の製造方法、基板処理装置、及び基板処理方法

【課題】形成する膜の仕事関数の値を、従来の技術を用いた場合よりも高くすることができる半導体装置の製造方法、基板処理装置、及び基板処理方法を提供する。

【解決手段】基板を収容した処理室に金属含有ガスを供給する工程と、処理室に窒素含有ガスを供給する工程と、処理室に酸素含有ガス又はハロゲン含有ガスを供給する工程と、を含むサイクルを複数回行うことで、基板に金属含有膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】高歩留まりの薄型半導体装置の製造方法を提供する。

【解決手段】まず、半導体ウェハ10の第1の主面S1に、複数の素子領域3およびこの素子領域3にコンタクトする端子電極5を形成し、こののち半導体ウェハ10の第1の主面S1と対向する第2の主面S2を、半導体ウェハ10の外周縁部を残して、所望の厚さとなるまで、薄肉化する。そして、薄肉化された半導体ウェハ10の前記第2の主面S2に、金属層6を形成し、こののち、金属層6上に絶縁被膜7を形成し、最後に、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得るものである。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備え、シード層3を形成する工程における下地の加熱温度を、アモルファスシリコン膜を形成する工程における前記下地の加熱温度よりも低くする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】ポリイミド膜に対して高い密着性を有するコバルト膜を成膜する方法を提供する。

【解決手段】成膜装置100の処理容器1内で、処理容器1内にCOガスを導入しながら、ポリイミド膜81が形成されたウエハWを110℃以上400℃以下の温度で加熱し、ポリイミド膜81を熱処理する。熱処理によって、ポリイミド膜81中の分子が熱分解し、膜密度が減少するとともに、表面粗度が大きくなる。その後、処理容器1内に成膜原料であるCo2(CO)8を導入してCVD法によりポリイミド膜81上にコバルト膜83を堆積させる。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてCo2(CO)8を用いてCo膜を成膜する場合に、段差被覆性が良好でかつ再現性高くCo膜を成膜することができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、成膜原料として固体原料であるCo2(CO)8を用い、これをCo2(CO)8の分解開始温度未満の温度で気化させて気体原料とし、これを基板Wに至るまでCo4(CO)12が生成されないようにして基板Wに供給し、前記基板上で熱分解によりCo膜を成膜する。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてCo2(CO)8を用いてCo膜を成膜する場合に、Co膜の針状の異常成長を抑制することができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、基板Wの温度を160〜300℃とし、処理容器1内に気体状のCo2(CO)8を供給し、基板W上でCo2(CO)8を熱分解させて基板W上にCo膜を成膜する。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

半導体装置およびその製造方法

【課題】より良質なゲート電極を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、ドレイン層と、前記ドレイン層の上に設けられたドリフト領域と、前記ドリフト領域の上に設けられたベース領域と、前記ベース領域の表面に選択的に設けられたソース領域と、前記ソース領域から前記ベース領域を貫通し、前記ドリフト領域に到達するトレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、前記ドレイン層に接続された第1主電極と、前記ソース領域および前記ベース領域に接続された第2主電極と、を備える。前記ゲート電極は、第1導電層と、前記第1導電層と前記ゲート絶縁膜との間に介在する第2導電層と、を含み、前記第2導電層の不純物濃度は、前記第1導電層の不純物濃度よりも低い。

(もっと読む)

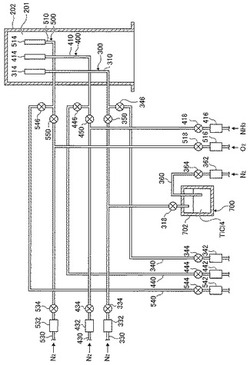

成膜方法、成膜装置、半導体装置及びその製造方法

【課題】めっき液への溶解性が低く、かつ単膜でCu拡散のバリア性にも優れたコバルト膜の成膜方法及び成膜装置を提供する。

【解決手段】炭素含有コバルト膜の成膜方法は、成膜装置100の処理容器1内にウエハWを搬入し、ステージ3上に配置する工程と、処理容器1内の圧力及びウエハWの温度を調節する工程と、処理容器1内にCo2(CO)8とアセチレンとをそれぞれ供給して処理容器1内で混合し、CVD法によりウエハWの表面に炭素含有コバルト膜を堆積させる工程と、成膜原料の供給を停止し、処理容器1内を真空引きする工程と、処理容器1内からウエハWを搬出する工程とを備えている。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、段差被覆性が良好でかつ再現性高くCo膜を成膜することができる成膜方法を提供すること。

【解決手段】処理容器1内に単一原料として気体状のCo4(CO)12を供給し、基板W上でCo4(CO)12を熱分解させて基板W上にCo膜を成膜する。このとき、成膜原料として固体原料であるCo2(CO)8を用い、これをCo2(CO)8の分解開始温度未満の温度で気化させ、これにより生成された気体状のCo2(CO)8をCo4(CO)12が安定に存在する温度にして気体状のCo4(CO)12に変化させ、処理容器1内に供給する。または、成膜原料として固体原料であるCo4(CO)12を用い、これを気化させて処理容器1内に供給する。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

電力用半導体装置

【課題】高温動作において配線の金属材料と半導体領域に接続する電極との反応が生じにくく、かつ、高温動作において歪みが生じにくい電力用半導体装置を実現する。

【解決手段】第1金属層14は、ゲート電極9とソース電極11との上に形成され、かつ、Pt,Ti,Mo,W,Taのうち少なくとも1種を含んでいる。第2金属層15は、第1金属層14上に形成され、かつ、Mo,W,Cuのうち少なくとも1種を含んでいる。層間絶縁膜10は、p型SiC領域13およびゲート絶縁膜8またはゲート電極9の表面上であってソース電極11が形成された領域以外の領域において形成されている。第1金属層14および第2金属層15は、層間絶縁膜10上に延在している。

(もっと読む)

121 - 140 / 1,609

[ Back to top ]