Fターム[4M104DD43]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | CVD (2,824)

Fターム[4M104DD43]の下位に属するFターム

Fターム[4M104DD43]に分類される特許

201 - 220 / 1,609

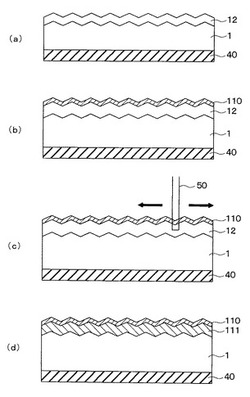

炭化珪素半導体装置の製造方法

【課題】不純物ドープを用いることなく、低温プロセスでオーミック電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bにアモルファス層12を形成する。そして、アモルファス層12が形成された裏面1b上に金属薄膜110を形成した後、n+型基板1の裏面1b側に光子エネルギーとレーザ出力の積が1000eV・mJ/cm2以上かつ8000eV・mJ/cm2以下となるような条件でレーザ光を照射することでシリサイド層111を含むドレイン電極11を形成する。これにより、n+型基板1に高温処理を行うことなく、n+型基板1にドレイン電極11にシリサイド層111を生成できる。したがって、不純物ドープ層を用いることなく、かつ低温プロセスによってドレイン電極11をオーミック電極にできる。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】緻密で原料起因の不純物濃度が低く抵抗率の低い金属膜を形成する半導体装置の製造方法及び基板処理装置を提供することである。

【解決手段】基板が収容された処理室に、第1の原料を供給して前記基板の表面に前記第1の原料を吸着させる第1の工程と、前記第1の原料が前記基板の表面で飽和吸着する前に、前記処理室に前記第1の原料とは異なる反応ガスを供給して、前記基板に吸着した第1の原料と反応させる第2の工程と、前記処理室内の雰囲気を除去する第3の工程と、前記処理室に前記第1の原料を改質する改質ガスを供給して、前記基板に吸着した前記第1の原料を改質する第4の工程と、を行うことで前記基板の表面に1原子層未満の膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

導電性酸化亜鉛膜および導電性酸化亜鉛膜を備えた光電変換素子

【課題】経時安定性の高い導電性酸化亜鉛膜を得る。

【解決手段】B、Al、GaおよびInからなる群から選ばれる1つ以上の元素をドーパントとして含む導電性酸化亜鉛膜において、膜中に水素を含むものとし、その水素の含有量を3×1021 atoms/cm3以下とする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】オーミックコンタクト層の膜厚やドライエッチング時のエッチングレートに依存せず所望のエッチングが可能となる薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性基板上に、ゲート電極と、ゲート電極を覆うように形成されたゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、を備える薄膜トランジスタの製造方法であって、絶縁性基板上に、ゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、がこの順に積層される積層ステップと、積層ステップによって積層されたソース・ドレイン電極とオーミックコンタクト層とがエッチングガスでエッチングされるエッチングステップと、オーミックコンタクト層がエッチングされてゲート絶縁膜が露出し始める点をエッチング終了ポイントとして検知するエッチング終了検知ステップと、を備える薄膜トランジスタの製造方法。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体製造装置に備わる真空室と装置外部との間のリークを早期に検知することにより、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】真空室において、高真空領域の圧力判定値と低真空領域の圧力判定値との間の圧力領域に任意の圧力値(例えば1Pa)を設定し、ウエハ搬送室の圧力が低真空側から高真空側へ通過する任意の圧力値を第1トリガポイントP1と設定し、次にウエハ搬送室の圧力が低真空側から高真空側へ通過する任意の圧力値を第2トリガポイントP2と設定する。第1トリガポイントP1と第2トリガポイントP2との間で、低真空側の最大圧力が低真空領域の圧力判定値に到達しているか否かの判定と高真空側の最小圧力が高真空領域の圧力判定値に到達しているか否かの判定を行う。

(もっと読む)

薄膜トランジスタとその製造方法、及びアクティブマトリックス基板

【課題】電極/配線の材料としてAl及び/又はその合金が用いられており、オフリーク電流が小さく良好な素子特性を有する薄膜トランジスタ(TFT)を提供する。

【解決手段】TFT101は、基板1上にゲート電極2とゲート絶縁膜3とチャネル層として機能する半導体膜4とを備え、半導体膜4上にソース電極6とドレイン電極7とが互いに離間して設けられたものであり、ソース電極6及びドレイン電極7は、アルミニウム及び/又はその合金を主成分とする少なくとも1層のアルミニウム(合金)膜を含む単層膜又は積層膜からなり、半導体膜4の表面のソース電極6及びドレイン電極7の間の領域8に、電気的に不活性な少なくとも1種のアルミニウム化合物9が形成されたものである。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

固体撮像素子とその製造方法

【課題】配線やコンタクトホールの寸法の微細化に際しても、コンタクト抵抗の低減を図ることが可能であり、且つ、暗電流の発生が少ない固体撮像素子およびその製造方法を提供する。

【解決手段】固体撮像素子1では、配線24と転送電極膜102とが、2層のコンタクトホールにより接続されている。下側のコンタクトホールAは、その底部にチタンシリサイド膜105が形成されている。そして、上側のコンタクトホールBは、チタンシリサイドを構成中に含まず、下側のコンタクトホールとの間が中間配線層としてのタングステン膜107により接続されている。ここで、上下の両コンタクトホールA,Bには、純粋なチタンは残っていない。また、撮像画素領域におけるフォトダイオード121の上方の層内レンズ膜127は、下方のコンタクトホールAに対して積層上方に選択的に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つチャネルの劣化を抑制可能なトレンチゲートを有する半導体装置を提供する。

【解決手段】n型のドレイン層11と、ドレイン層11の主面に配設され、ドレイン層11よりも不純物濃度が低いn型のドリフト層12と、ドリフト層12上に配設されたp型のベース層13と、ベース層13の表面領域に配設され、ドリフト層12よりも不純物濃度が高いn型のソース層14と、ソース層14及びベース層13を貫通し、ドリフト層12に達する深さを有して配設されたストライプ状のゲートトレンチ16と、ゲートトレンチ16を形成する側面及び底面に沿って配設されたトレンチ形状のゲート絶縁膜17と、ゲート絶縁膜17の開口幅の狭い対向する側面に設けられた触媒層18と、トレンチ形状のゲート絶縁膜17内に、触媒層18に接続されたカーボンナノチューブ19が配設されたゲート電極21とを備える。

(もっと読む)

金属アミジナートを用いる原子層の析出

【課題】特定の金属先駆物質を用いたALD法により、基板表面に、均一で共形的な厚さと平滑な表面とを有する金属含有皮膜を形成する方法を提供する。

【解決手段】加熱基板を、一種以上の揮発性金属(I)、(II)あるいは(III)アミジナート化合物又はそのオリゴマーの蒸気に、次いで、還元性ガス、窒素含有ガス又は酸素含有ガスあるいはそれらの蒸気に交互に暴露して、当該基板表面に金属皮膜、金属窒化物皮膜又は金属酸化物皮膜を形成させることを含んでなる、金属を含む薄膜の形成方法。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

201 - 220 / 1,609

[ Back to top ]