Fターム[4M104DD94]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 2種類以上の電極の同時形成 (126)

Fターム[4M104DD94]の下位に属するFターム

材料が異なる電極 (47)

Fターム[4M104DD94]に分類される特許

1 - 20 / 79

太陽電池電極用ペースト組成物

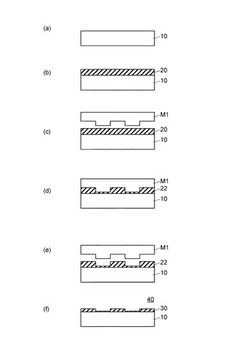

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】Ge基板上に形成されたPチャネル型MISFETの第1ソースおよび第1ドレインが、Ge原子とニッケル原子との化合物、Ge原子とコバルト原子との化合物またはGe原子とニッケル原子とコバルト原子との化合物からなり、III−V族化合物半導体からなる半導体結晶層に形成されたNチャネル型MISFETの第2ソースおよび第2ドレインが、III族原子およびV族原子とニッケル原子との化合物、III族原子およびV族原子とコバルト原子との化合物、または、III族原子およびV族原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタと回生素子とを含み、優れたリカバリ特性によりスイッチング損失が低減された半導体装置を提供すること。

【解決手段】電界効果型トランジスタと回生素子とを含み、前記電界効果型トランジスタは、第1の導電型を有する第1の半導体層と、前記第1の半導体層の表面に配置された第2導電型を有する第2の半導体層と、前記第2の半導体層の表面に配置された前記第1導電型を有する第3の半導体層と、前記第1の半導体層と前記第2の半導体層と前記第3の半導体層とに隣接するように配置された絶縁膜を介して配置されたゲート電極と、第1の金属層と、第2の金属層と、を備え、前記回生素子は、前記第1の金属層と電気的に接続されるアノード端子と、前記第2の金属層と電気的に接続されるカソード端子と、を備えることを特徴とする半導体装置。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】p型SiC領域と金属との低抵抗コンタクトの実現を可能とする半導体装置を提供する。

【解決手段】実施形態の半導体装置は、導電性材料を用いた電極240と、導電型がp型の炭化珪素(SiC)半導体部220と、を備えており、かかるp型のSiC半導体部220は、前記第1の電極240に接続され、マグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)、及びバリウム(Ba)のうちの少なくとも1種類の元素が前記電極との界面部に面密度がピークになるように含有されたことを特徴とする。

(もっと読む)

化合物半導体装置

【課題】電流コラプス現象が抑制され、且つフィールドプレート電極による電界集中を緩和する効果の低下が抑制された化合物半導体装置を提供する。

【解決手段】III族窒化物半導体層と、III族窒化物半導体層上に配置された絶縁膜7と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたドレイン電極4と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたソース電極3と、ドレイン電極とソース電極間においてIII族窒化物半導体層の上面から膜厚方向に第2の距離T3の位置に絶縁膜を介して配置されたゲート電極5と、ドレイン電極とゲート電極間においてIII族窒化物半導体層の上面から膜厚方向に第1の距離T1より短い第2の距離T2の位置に絶縁膜を介して配置されたフィールドプレート電極6とを備える。

(もっと読む)

半導体装置

【課題】ゲート抵抗の増大を抑制しつつ、外部ウェルがトレンチゲート電極によってセル領域のウェルから分断されてしまうことを抑制する。

【解決手段】埋込ゲート電極140のうち平面視でゲートコンタクト領域102と重なる方向に延伸している埋込ゲート電極142は、ゲート電極310と重ならないように、ゲート電極310の手前までしか延伸していない。また埋込ゲート電極142の相互間に位置するソースコンタクトは、図中上下方向において、埋込ゲート電極142よりも短く形成されている。そして埋込ゲート電極142のうちゲート電極310側の端部は、ゲート電極310の手前に設けられた接続用埋込電極141によって互いに接続されている。接続用埋込電極141は、半導体装置の長辺と平行な方向に延伸している。接続用埋込電極141は、埋込ゲート電極142の隣に位置する埋込ゲート電極144には接続していない。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

半導体装置及びその製造方法

【課題】低いチャネル抵抗を具現し、電界効果移動度が高くなる効果がある二重ゲートトランジスタを含む半導体装置及びその製造方法を提供する。

【解決手段】本発明による半導体装置は、下部ゲート電極と、前記下部ゲート電極上の上部ゲート電極と、前記下部ゲート電極と前記上部ゲート電極の間に介在され、前記下部ゲート電極と前記上部ゲート電極を連結するコンタクトプラグと、前記上部ゲート電極と同一の高さに前記上部ゲート電極から離隔して形成された機能電極と、を含む。本発明によれば、電界効果移動度が高い二重ゲートトランジスタを半導体装置に適用させることによって、半導体装置の特性を改善することができる。特に、本発明によれば、別途のマスク工程や蒸着工程を追加する必要がないので、工程コストの上昇や収率減少をもたらすことなく、大面積・高画質の半導体装置を大量生産することができる。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

1 - 20 / 79

[ Back to top ]