Fターム[4M104DD99]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | その他 (65)

Fターム[4M104DD99]に分類される特許

21 - 40 / 65

成膜方法

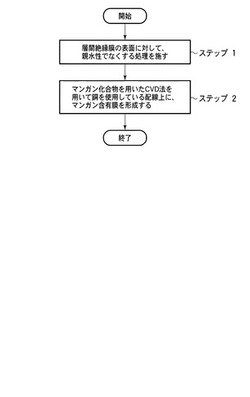

【課題】 キャップ膜、もしくはバリア膜として使用することが可能な膜を、形成するか形成しないかを選択することが可能となる成膜方法を提供すること。

【解決手段】 銅を使用している配線と絶縁膜とが表面に露出している基板に対してマンガン含有膜を成膜する成膜方法であって、銅を使用している配線上に、マンガン化合物を用いたCVD法を用いてマンガン含有膜を形成する工程(ステップ2)を備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極中の不純物がゲート絶縁膜を突き抜けてチャネル領域に拡

散するのを抑制し、ソース・ドレイン領域の不純物イオンが部分的にチャネル領

域方向に異常拡散するのを防ぐ。

【解決手段】ゲート絶縁膜3上に、ポリシリコン膜4を被着してゲート電極5

パターンにパターンニングした後、ソース・ドレイン領域9を形成する前に、窒

素を含む雰囲気中で窒化処理を行って、ゲート電極5端部付近のゲート絶縁膜3

中に新たに窒素を導入する。または、ゲート電極5のパターンニング後、ソース

・ドレイン領域9を形成する前に、酸化処理を行うことによってゲート電極5の

パターンニングの際に生じるダメージや汚染の一部を酸化膜中に取り込んで基板

から除去する。その後、窒化処理を行うことにより、酸化処理によってゲート電

極5端部付近に形成され、ダメージを含む酸化膜に積極的に窒素を導入する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線間リーク電流の増加を抑制できる配線構造を備えた半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられ、シリコン、酸素、炭素および水素を含む、配線溝5が形成された絶縁膜3,4と、配線溝5内に設けられた金属配線8と、金属配線8の上面に選択的に形成されたメタルキャップ10とを具備してなり、絶縁膜4は、その表面を含む第1の領域と、第1の領域下の第2の領域とを備えており、前記第1の領域の炭素濃度は前記表面から深くなるに従って減少し、前記第2の領域内の炭素濃度は、前記第1の領域との界面から一定距離の深さまでは深くなるに従って減少し、前記一定の距離減を越えると深くなるに従って増加し、前記表面における炭素濃度を超えることを特徴とする。

(もっと読む)

平坦な導電性膜の製造方法及び半導体装置の製造方法並びに半導体装置

【課題】半導体装置の消費電力を低減させることができる半導体装置の製造方法を提供する。

【解決手段】基板(S1)を準備する工程と、テンプレート(S2)を準備する工程と、前記テンプレート表面にゲート電極(10)を形成する工程と、前記基板およびテンプレートを貼り合わせる工程と、前記テンプレートから前記基板および前記ゲート電極を一体的に剥離して前記ゲート電極を前記テンプレートから前記基板に転写するする工程と、を有する。かかる方法によれば、ゲート電極の表面の平坦性が向上し、その上に形成されるゲート絶縁膜(12)の表面の平坦性も向上する。その結果、ゲート絶縁膜の薄膜化が容易となり、半導体装置の消費電力の低減ができる。

(もっと読む)

金属膜の膜厚測定方法及び基板処理方法及び装置

【課題】 インラインにおいても金属膜の実際の膜厚を測定することが可能な金属膜の膜厚測定方法を提供する。

【解決手段】 膜厚測定用の測定光を測定対象物11に照射する工程と、測定対象物11からの反射光からこの測定対象物11の反射率を検出する工程と、検出された測定対象物11の反射率から得た測定反射率データと、膜厚判断の基礎となる基礎反射率データとに基づいて、測定対象物11の膜厚を決定する工程と、を備え、測定対象物11が導電性を有する金属膜であり、金属膜の膜厚が、金属膜に透過した測定光がこの金属膜中で全て吸収されない膜厚以下である。

(もっと読む)

半導体装置の製造方法

【課題】加工精度を改善し、かつ厚い配線を得るための半導体装置の製造方法を提供することを課題とする。

【解決手段】絶縁性基板上に形成された導電性膜上に配線形成領域を覆う第1のフォトレジストパターンを形成する工程と、前記第1のフォトレジストパターンをマスクとする異方性エッチングにより前記導電性膜の上部を除去することで第1溝を形成する工程と、前記第1のフォトレジストパターンを除去した後、前記第1溝の底部の少なくとも一部が露出した開口を有する第2のフォトレジストパターンを形成する工程と、前記第2のフォトレジストパターンをマスクとする異方性エッチングにより前記第1溝の底部に露出する前記導電性膜の下部を少なくとも除去することで第2溝を形成する工程を備えることで、前記第1溝と第2溝に由来する配線分離溝と、前記配線分離溝により分離された配線とを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

基板洗浄及び無電解析出のプロセス及び溶液

【解決手段】本発明は、デバイスの製造に関する。一実施形態として、基板洗浄及び集積回路用のキャップ層の無電解析出の方法を提供する。この方法は、金属及び誘電体ダマシンメタライゼーション(金属化)層を含む表面を有する基板上で実行される。この方法は、基板の表面を洗浄するのに十分な洗浄溶液に基板の表面をさらす工程と、キャップ層を析出させるのに十分な無電解析出溶液に基板表面をさらす工程と、を備える。本発明の別の実施形態として、基板を洗浄するための溶液及び無電解析出を実現するための溶液を提供する。 (もっと読む)

金属薄膜パターンの形成方法および電気光学装置の製造方法

【課題】基板110上に形成したアルミニウムからなる金属薄膜130の上面にエッチン

グマスク140を形成し、そのエッチングマスクを介して上記金属薄膜をハロゲン系ガス

を含む混合ガスでドライエッチングして所定形状の金属薄膜パターン130を形成する金

属薄膜パターンの形成方法または電気光学装置の製造方法において、アフターコロージョ

ンの発生をより確実に防止できるようにする。

【解決手段】上記のような金属薄膜パターンの形成方法または電気光学装置の製造方法に

おいて、上記金属薄膜130をドライエッチングして所定形状の金属薄膜パターンを形成

する工程を経た後に、メタノールを単ガスで放電して前記ドライエッチング後に残留する

デポ物150を除去する工程と、酸素を単ガスで放電して酸素プラズマによるアッシング

処理で前記エッチングマスク140を除去する工程とを順に同一のチャンバー内で行うよ

うにしたことを特徴とする。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体装置100aの製造方法は、以下の工程を備えている。まず、炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の表面に、金属層が形成される。そして、金属層を熱処理することにより電極150が形成される。そして、電極150の表面の炭素を除去するためのエッチングが行なわれる。金属層を形成する工程では、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い金属層を形成する。

(もっと読む)

デバイスのパターニング

【課題】有機スイッチングデバイスまたは部分有機スイッチングデバイスを形成する方法である。

【解決手段】前記方法は、少なくとも1つのパターニング層を含む電気デバイスを基板上に形成する方法であって、前記基板上の第1の材料層を光ビームに露光して、前記第1の層の物理的特性を改変するように、前記第1の層のパターニングを行う工程を含み、前記光ビームの一部は、前記基板上の事前堆積されたパターンによってブロックまたは減衰され、これにより、前記光がブロックまたは減衰されない領域においてのみ前記基板上の第1の層を改変する、方法である。

(もっと読む)

半導体装置の製造方法

【課題】本発明の課題は、電極や配線の周囲に空間部を形成するに際し、電極材料や配線材料が耐フッ酸性がない材料であっても適用でき、かつ有機汚染の心配のない半導体装置の製造方法を提供することである。

【解決手段】本発明の半導体装置の製造方法は、ゲート電極21aの周囲を昇華性を有する材料としての塩化アルミニウム膜22aからなる犠牲膜で被覆し、その犠牲膜の周囲を外殻層としてのSiN膜23で被覆し、外殻層に設けた開口部24を通して犠牲膜をその昇華温度以上に加熱し除去して、ゲート電極21aの周囲に空間部25を形成する。

(もっと読む)

窒化物半導体装置とその製造方法

【課題】 p型の窒化物半導体層と、窒化物半導体層の表面を覆っているとともに貫通孔が形成されている絶縁膜と、貫通孔の底面に露出している窒化物半導体層の表面に接している金属膜を備えている窒化物半導体装置の製造方法において、良好なオーミック特性を実現できる製造方法を提供する。

【解決手段】 p型の窒化ガリウム層2の表面に酸化シリコン膜4を形成する。次に、酸化シリコン膜4の一部をエッチングし、窒化ガリウム層2の表面に達する貫通孔6を形成する。次に、窒化ガリウム層2の表面に付着したシリコン8を除去する。次に、窒化ガリウム層2の表面に接する金属膜を形成する。次に、窒化ガリウム層2と酸化シリコン膜4と金属膜を熱処理する。シリコン8を除去する工程と金属膜を形成する工程は、シリコンを含まない雰囲気下で行う。

(もっと読む)

金属コンタクト層を有するパワー半導体素子およびその製造方法

【課題】金属コンタクト層を有するパワー半導体素子およびその製造方法を提供する。

【解決手段】本発明は、基体と、少なくとも1つの接触面とを有するパワー半導体素子であって、この接触面の上に、第1材料の少なくとも1つの第1の薄い金属層が配置されたパワー半導体素子に関する。本発明によれば、第1の層に比べて厚い、第2材料のさらなる金属層が、その材料の加圧焼結接続によって、第1の層の上に配置される。関連の方法は、以下の本質的なステップを含む。ウェハ集合体内に複数のパワー半導体素子を製造するステップと、それぞれのパワー半導体素子の少なくとも1つの接触面の上に、少なくとも1つの第1の薄い金属層を施与するステップと、各パワー半導体素子ごとに、第1の金属層の少なくとも1つの上に、第2材料と溶媒とからなるペースト状の層を配置するステップと、ペースト状の層に圧力を印加するステップと、半導体素子を個別化するステップ。

(もっと読む)

パターン形成方法および半導体装置の製造方法ならびに半導体装置

【課題】第1版上に均一な膜厚の導電性薄膜を形成することが可能なパターン形成方法および半導体装置の製造方法ならびに半導体装置を提供する。

【解決手段】第1版10上に、脂肪酸または脂肪族アミンにて表面修飾された導電性粒子と溶媒とを含む液組成物を塗布することで、導電性膜Dを形成する第1工程と、表面側に凹凸パターンを有する第2版20を、第1版10の導電性膜Dの形成面側に押圧し、第2版20の凸部20aの頂面に、導電性膜の不要なパターン(第1のパターン)を転写して除去することで、第1版10上に導電性パターンD’(第2のパターン)を形成する第2工程と、第1版10の導電性パターンD’の形成面側を、被転写基板の表面に押圧することで、被転写基板の表面に導電性パターンD’を転写する第3工程とを有することを特徴とするパターン形成方法および半導体装置の製造方法ならびに半導体装置である。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】安定した特性を有する、ショットキ電極を備えた炭化珪素半導体装置の製造方法を得る。

【解決手段】ショットキ電極が形成されるN-低濃度層2の表面側が熱酸化膜5を介して熱処理装置のサセプタ11に接するように配置する。すなわち、熱酸化膜5の全表面をサセプタ11に接触させた状態で、N+高濃度基板1及びN-低濃度層2の積層構造を配置する。この配置状態で、N+高濃度基板1の裏面上に金属で形成されるオーミック電極7を形成する。

(もっと読む)

ナノギャップ電極の製造方法

【課題】金属細線の絶縁破壊を防止することを第1の課題とし、高い再現性でギャップ電極を製造することを第2の課題とする。

【解決手段】直流電圧VDCを発生させ、エレクトロマイグレーションを引き起こすパルス電圧Vpを所定の間隔で発生させ、直流電圧VDCとパルス電圧Vpとを重畳した電圧を金属細線14に印加する。

(もっと読む)

半導体装置、半導体装置の製造方法および電子機器

【課題】電極と、基板または絶縁層との密着性に優れる半導体装置、かかる半導体装置を簡便に製造する方法および信頼性の高い電子機器を提供すること。

【解決手段】半導体装置1は、有機半導体層7と、絶縁部6と、有機半導体層7に重なるゲート部3と、有機半導体層7と絶縁部6との間に位置するソース部4と、有機半導体層7と絶縁部6との間に位置するドレイン部5と、を備え、絶縁部6は、典型金属元素で構成される複合金属酸化物を含み、ソース部4とドレイン部5の少なくとも一つが、絶縁部6を構成する複合金属酸化物の一部が導体化されたものを含む。

(もっと読む)

半導体装置の製造方法

【課題】特定の領域毎に同一材料を用いて異なる品質の半導体要素を作り分ける。

【解決手段】素子分離2及びウェル3,4が形成されたシリコン基板1表面にゲート酸化膜5を形成し、ゲート酸化膜5上にゲート電極7を形成する。ゲート電極7を挟むシリコン基板1上層に、エクステンション用の浅い拡散層8を形成する。NMOS領域を覆うように反射膜28を形成した後、光源から可視光を照射することにより、PMOS領域にソース/ドレイン領域10aを形成する。反射膜28を除去した後、光源から可視光を再度照射することにより、ソース/ドレイン領域10aとは異なる品質のソース/ドレイン領域がNMOS領域に形成される。

(もっと読む)

半導体装置の製造方法

【課題】パワートランジスタを有する半導体装置の信頼性を向上させる技術を提供する。

【解決手段】素子を形成した半導体ウェハ1の主面に、素子と電気的に接続するように堆積した第1導体膜14および第2導体膜15に所望のパターンを形成する工程であり、まず、半導体ウェハ1を第1の回転速度で回転させた状態で、半導体ウェハ1の主面に対して薬液17を供給することにより、第2導体膜15に対してウェットエッチング処理を施す(工程100)。エッチング終了後、薬液17が半導体ウェハ1の主面に残るように、回転速度を第1の回転速度よりも遅い第2の回転速度に変更し、その状態で半導体ウェハに純水19を撒水することにより、純水19が半導体ウェハ1の主面に残されるようにした状態で薬液17を洗浄する(工程101)。続いて、第1導体膜14に対してドライエッチングを施す(工程102)。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】配線と半導体基板とを電気的に接続するコンタクトプラグを長方形に形成し、コンタクトプラグの電気的特性を向上させるフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板100の上に層間絶縁膜102と、第1,第2ハードマスク膜104,106、第1フォトレジストパターン108を順に形成する。第1フォトレジストパターンの周辺領域をシリコン含有物質層110に変換する。エッチングによりシリコン含有物質層の上部領域を除去すると同時に未変換のフォトレジストも除去しサイズとピッチの小さいシリコン含有物質層パターンを形成する。エッチングにより第2ハードマスク膜パターンを形成し、その上に一部領域が開放された第2フォトレジストパターンを形成する。エッチングにより長方形の第1ハードマスク膜パターンを形成する。これをマスクに層間絶縁膜をエッチングし、長方形のコンタクトホールを形成する。

(もっと読む)

21 - 40 / 65

[ Back to top ]