Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

781 - 800 / 992

半導体装置およびその製造方法

【課題】半導体装置を微細化するとともに、ゲート電極と不純物拡散領域とを接続する共通コンタクトにおける電流リークを抑制する。

【解決手段】半導体装置100は、第1のゲート電極108と、第4のソース・ドレイン領域114bと、これらを電気的に接続する共通コンタクト112と、を含む。ゲート長方向の断面において、第1のゲート電極108と第4のソース・ドレイン領域114bとが離間して設けられるとともにこれらの間の半導体基板160表面全面に素子分離絶縁膜102が形成され、第1のゲート電極108と第4のソース・ドレイン領域114bとの間の距離が、ゲート長方向の他の断面における第1のゲート電極108側壁に形成されたサイドウォールの幅と実質的に等しい。

(もっと読む)

半導体装置の製造方法

【課題】 コンタクトパッドを形成する半導体装置の製造方法において、隣接する半導体素子間のショートを防止する。

【解決手段】 シリコン基板11上に、それぞれが金属層15を含むゲート電極17とゲート電極17を覆うゲート側壁絶縁膜20とを有する複数のゲート電極構造体を形成する工程と、ゲート電極構造体を覆って全面にポリシリコン膜を堆積する工程と、ポリシリコン膜をパターニングし、隣接する2つのゲート電極構造体の間でシリコン基板11に接続するコンタクトパッド22を形成する工程(図3(g))と、ゲート側壁絶縁膜のくぼみ21に残留するポリシリコン24を酸化させて酸化シリコン25に形成する工程(図3(h))とをこの順に有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】均一なシリサイド相を有するFUSIゲート電極を含む半導体装置およびその製造方法を提供する。

【解決手段】シリコンゲート202を含む基板全面上にNi膜205を堆積後、CMP処理等によってシリコンゲート202の一部を除去し、上面が平坦で膜厚が均一なNi層206をシリコンゲート202の直上に残す。続いて、シリサイド反応を行わせることにより、均一なシリサイド相を有するゲート電極207を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程を複雑にすることなく、金属シリサイドよりなるゲート電極及びこのゲート電極を覆うストレッサ膜を形成しうる半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板10内にチャネル領域を挟んで形成されたソース/ドレイン領域38と、チャネル領域上にゲート絶縁膜12を介して形成された金属シリサイドよりなるゲート電極44とを有するN型MISFETと、ゲート電極44を内包するようにゲート電極44の側壁部から上面部に渡って形成され、1GPa〜2GPaの引張り応力を有し、チャネル領域に引っ張り応力を印加する絶縁膜46とを有する。

(もっと読む)

半導体装置の製造方法、薄膜トランジスタ及び表示装置

【課題】ソース領域及びドレイン領域における不純物の活性化及びコンタクト抵抗の低減を効率良く行うことができる、生産性に優れた半導体装置の製造方法を提供すること。

【解決手段】基板上に半導体膜を形成する工程、前記半導体膜を含む前記基板上にゲート絶縁膜を形成する工程、前記ゲート絶縁膜上にゲート電極を形成する工程、前記ゲート電極をマスクとして前記ゲート絶縁膜をエッチングし、前記半導体膜を露出する工程、全面に金属層を形成する工程、前記ゲート電極をマスクとして前記半導体膜に不純物を注入する工程、及び前記不純物注入領域に熱処理を施し、前記半導体膜中の不純物を活性化するとともに、前記半導体膜と金属層との界面に金属シリサイド層を形成する工程を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきを防止し、微細化に好適な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11の主面にゲート絶縁膜を介して上部の不純物濃度が下部より高く、且つ第1および第2の領域における導電型が互いに異なるゲート電極膜を形成する工程と、ゲート電極パターンを有する第1絶縁膜をマスクとして、第1および第2の領域のゲート電極膜の上部をエッチングして第1および第2ゲート電極の上部18a、23aを形成する工程と、第1および第2ゲート電極の上部18a、23aの側壁に第2絶縁膜を形成する工程と、第1および第2絶縁膜をマスクとして、第1および第2の領域のゲート電極膜の下部をエッチングして第1および第2ゲート電極の下部18b、23bを形成する工程を有する。

(もっと読む)

半導体装置とその製造方法

【課題】

nMOSFETのゲートとpMOSFETのゲートとが異なる低抵抗材料で形成された半導体装置とその製造方法を提供する。

【解決手段】

pMOSFETとnMOSFETとを有する半導体装置であって、pMOSFET及びnMOSFETのそれぞれは、シリコン基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極両側に形成されたソース/ドレイン領域と、を有し、pMOSFETのゲート電極及びソース/ドレイン領域と、nMOSFETのソース/ドレイン領域とは、金属リッチのシリサイドで形成され、nMOSFETのゲート電極は、置換アルミニウムで形成される。

(もっと読む)

半導体構造およびその処理方法

【課題】ボーダレス・コンタクトを有するデュアル・ワーク・ファンクション半導体構造およびその製造方法を提供する。

【解決手段】この構造は、実質的に無キャップのゲート108と、無キャップのゲートに隣接する拡散部116への導電コンタクト134,170とを備え、導電コンタクトは、ゲートに対しボーダレスである電界効果トランジスタ(FET)を含むことができる。この構造は、デュアル・ワーク・ファンクション構造であるため、導電コンタクトを、無キャップゲートに電気的に接続することなく、無キャップゲート上に延長させることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のより微細化に適し、しかも低コストである半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体シリコン基板表面上に形成されたポリシリコン膜からなるゲート電極構造とこれを覆う層間絶縁膜を有する半導体装置の製造方法において、層間絶縁膜形成後、層間絶縁膜を貫いてコンタクトホールを開口させて所望のコンタクト面を露出させる工程、少なくともコンタクトホール側壁部及びコンタクト面上に絶縁膜を堆積させる工程、絶縁膜をエッチバックすることによりコンタクトホール側壁部にサイドウォール状絶縁膜を形成することを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

MOSFETデバイスのシステムおよび方法

【課題】MISFEEDデバイスシステムおよびそれを製造する方法を開示する。

【解決手段】本発明は、MISFEEDデバイス構造のコンテクスト内でソース接続および/またはドレイン接続のためにショットキーバリア接触(301、302)を利用して、短チャネル効果を制御するためにハロー/ポケット注入および浅いソース/ドレイン拡張部の必要性を除去する。付け加えると、本発明は、MISFEED製造と関連した寄生バイポーラ利得を無条件に除去し、製造コストを減らし、デバイス性能パラメータを厳密に制御し、従来技術と比較して優れたデバイス特性を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 T字型又はΓ型のゲート電極を用いる場合に、耐湿性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】 半導体基板と、半導体基板上に離間して形成されたソース電極及びドレイン電極と、ソース電極とドレイン電極との間に配置され、半導体基板とショットキ接合されたT字型又はΓ型のゲート電極と、ゲート電極の下部の柱状部分を覆う酸化膜とを有し、酸化膜とソース電極及びドレイン電極とは離間している。

(もっと読む)

微小電気機械式装置の作製方法

【課題】微小構造を有するマイクロマシンの量産に際して、微小構造体と微小構造体を制御する半導体素子を同一基板上に形成し、コストを低減する方法を提供する。

【解決手段】マイクロマシンの作製に際して、膜のパターン形成を行うためのマスク材料を用いて犠牲層を形成し、半導体素子を形成する領域におけるマスクの除去と、微小構造体を形成する領域における犠牲層とマスクの除去を同一の工程にて行う。具体的には絶縁性基板上に選択的に犠牲層103を形成し、犠牲層を覆って半導体層104を形成し、半導体層上にマスク105を形成し、マスクを用いて半導体層をエッチングし、マスク及び犠牲層の除去を同時に行う微小電気機械式装置の作製方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極上にシリサイド膜を有し、従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極62及びLDD層63が形成された半導体基板60の上にシリサイドブロックとなるSiN膜64を形成し、このSiN膜64にゲート電極62に通じる開口部を設ける。この開口部を介してゲート電極66の表面をシリサイド化してシリサイド膜66を形成する。次に、SiO2からなる層間絶縁膜67を形成し、フォトリソグラフィ法により層間絶縁膜67の上面からLDD層63に到達するコンタクトホール67hを形成する。そして、このコンタクトホール67hを介してLDD層63に不純物を高濃度に導入して、ソース/ドレイン層63aを形成する。

(もっと読む)

デュアルゲート構造及びその製造方法、デュアルゲート構造を備える半導体素子及びその製造方法

【課題】デュアルゲート構造及びその製造方法、デュアルゲート構造を備える半導体素子及びその製造方法を提供する。

【解決手段】半導体素子は、基板上に形成された少なくとも2つのスタックゲート構造を備える。2つのスタックゲート構造は、各々半導体層及び半導体層上に形成された金属層を備える。基板上に形成された2つのスタックゲート構造は、相異なる中間層、すなわち、2つのスタックゲートのうち1つは、オーミック層を備え、2つのスタックゲートのうち他の1つは、オーミック層を備えないことにその特徴がある。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を使用したMISFETにおいて高誘電率ゲート絶縁膜を劣化させることなくMISFETの特性を向上させる。

【解決手段】 基板1の活性領域上に高誘電率ゲート絶縁膜4Aを介してゲート電極5が形成されている。ゲート電極5の側面には絶縁性のサイドウォール7が形成されている。高誘電率ゲート絶縁膜4Aはゲート電極5の下側からサイドウォール7の下側まで連続的に形成されている。高誘電率ゲート絶縁膜4Aにおけるサイドウォール7の下側領域の厚さは、高誘電率ゲート絶縁膜4Aにおけるゲート電極5の下側領域の厚さよりも小さい。

(もっと読む)

シリサイド化されたゲートの形成方法

【課題】シリサイド化されたゲートの形成方法を提供する。

【解決手段】ゲートは、ゲートの上部を通じたシリサイド化を制限しつつ、その側面を通じてシリサイド化される。ブロッキング膜は、ゲート膜上に形成され、ゲート膜の側壁は露出される。ゲートの側壁上に金属膜が形成され、熱処理されてゲート膜をシリサイド化する。ブロッキング膜上に形成されたシリサイド膜をエッチングマスクとして使用するエッチング工程を通じてゲートの側壁は露出される。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させずにメタルゲート構造の加工性を向上した、45nm世代以降のSoCデバイスの製造に対応可能な半導体装置の製造方法を得る。

【解決手段】半導体基板上に高誘電率材料層を形成する高誘電率材料層形成工程と、前記高誘電率材料層上に該高誘電率材料層に接するとともに金属、金属合金、またはこれらの化合物からなる金属層を形成した後、該金属層をパターニングすることにより金属ゲート電極層を形成するゲート電極層形成工程と、前記金属ゲート電極層の側壁部にウエットエッチング耐性を有する保護膜を形成する保護膜形成工程と、前記高誘電率材料層をウエットエッチングによりパターニングして高誘電率ゲート絶縁膜を形成する高誘電率ゲート絶縁膜形成工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート抵抗を十分に低抵抗化できると共に、高耐圧が得られる半導体装置を提供する。

【解決手段】p型半導体基板11上にはp型ボディ領域14が形成され、ボディ領域14の表面領域にはn+型ソース領域15が形成されている。半導体基板11上にはn+型ドレイン領域17が形成され、ソース領域15とドレイン領域17との間の半導体基板11の表面領域にはn-型ドリフト領域18が形成されている。ソース領域15とドリフト領域18との間のボディ領域14上及び半導体基板11上にはゲート絶縁膜19が形成され、ゲート絶縁膜19上にはゲート電極21が形成されている。ゲート電極21の上面全体、ソース領域15上及びドレイン領域17上にはシリサイド膜22が形成されている。さらに、ドリフト領域18上には保護絶縁膜20が形成され、ソース領域15側のゲート電極21の側面上にはゲート側壁絶縁膜23が形成されている。

(もっと読む)

半導体装置及びその製造方法

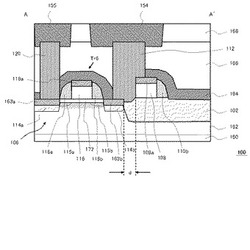

【課題】シェアードコンタクトを有し、且つ、リーク電流の低減が図れる半導体装置及びその製造方法を提供する。

【解決手段】シェアードコンタクト形成領域に位置するゲート電極配線14bの上面上及び側面上にはシリサイド層20dが形成されている。そして、層間絶縁膜22には、N型ソース・ドレイン領域19b上のシリサイド層20b及びゲート電極配線14b上のシリサイド層20dに接続するシェアードコンタクトとなるコンタクトプラグ24bが形成されている。これにより、層間絶縁膜22にコンタクトホール23bを形成した際、半導体基板11の表面を露出させることなく形成することができる。

(もっと読む)

781 - 800 / 992

[ Back to top ]