Fターム[4M104EE20]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | その他 (71)

Fターム[4M104EE20]に分類される特許

61 - 71 / 71

電界効果トランジスタ

【課題】出力特性劣化などの不具合の発生を抑え、良好な信頼性を得ることが可能な電界効果トランジスタを提供する。

【解決手段】化合物半導体基板11に形成される動作領域12、動作領域12上に形成されるゲート電極13と、動作領域12上にゲート電極13を挟んで交互に形成されるソース電極14及びドレイン電極15と、外部回路と接続されるためのボンディングパッド18、19と、ソース電極14又はドレイン電極15と接続される電極接続部20aと、ボンディングパッド18、19と接続されるパッド接続部20bと、電極接続部20a及びパッド接続部20b間を接続する空中配線部20cを有するエアブリッジ20を備え、夫々エアブリッジ20の幅方向の断面において、電極接続部20aの断面積が、空中配線部20cの断面積以下及び/又は電極接続部の幅が、空中配線部の幅より狭いことを特徴とする。

(もっと読む)

実効仕事関数を調整するための方法

【課題】本発明は、様々なトランジスタタイプの金属ゲート電極の実効仕事関数及び閾値電圧を、簡便で、再生可能でまた効率的な方法で制御することができるMOSFETデバイスを製造する方法を提供すること。

【解決手段】本発明は、MOSFET、FinFET、若しくはメモリーデバイスにおけるゲートを作製するにあたり、半導体基板上に、(予め)決定された移動度、リーク、及び/又はEOT(酸化膜換算膜厚)の仕様を満たす誘電体材料からなる少なくとも一層を成長させ、

上記ゲート電極を形成する前に、上記少なくとも一層の誘電体層とゲート電極との間の界面に、ランタンハフニウム酸化物材料を含む若しくはこれからなる、好ましくはLa2Hf2O7からなる界面層を成長させ、上記界面層に接触する誘電体材料からなる少なくとも一層を、上記界面層材料と相違させることを特徴とする。

金属ゲート電極、ゲート誘電体及び界面層を備える新たなMOSFETを開示している。その製造方法、及びその応用も提供する。

(もっと読む)

中間層を有する半導体素子の形成方法及びその構造

基板(10)上に位置するスタック(30)。スタックは、誘電体層(16)と金属層(26)との間に層(24)を有する。その層は、ハロゲン及び金属を含む。一実施形態において、ハロゲンはフッ素である。一実施形態において、スタックは、トランジスタ用の制御電極スタックである。一例において、制御電極スタックは、MOSFET用のゲートスタックである。一例において、層はフッ化アルミニウムを含む。  (もっと読む)

(もっと読む)

デバイス製造方法およびコンピュータプログラム

【課題】従来のリソグラフィ技法を用いて可能であるものより高い密度で、アレイを形成すること。

【解決手段】たとえばコンタクトホールを形成する方法では、まず第1ハードマスク層12の上に最終間隔の2倍の間隔でスタッド13のアレイを形成する。次に第2犠牲ハードマスク14をコンフォーマルに堆積し、最終アレイ配置にするために上記のスタッド13の各グループ間の中央部に方向性エッチングによる穴を交互配置する。さらに上記のスタッド13を除去する。その結果最初のスタッド13の2倍の密度の穴のアレイが得られる。最後に第1ハードマスク層12はエッチングされたコンフォーマルコーティング14’を介してエッチングされ所望の密度でアパーチャのアレイを有することができる。また、この方法を繰り返して、さらに高い密度でアレイを作成することができる。

(もっと読む)

異なった動作機能を示すゲートを有する2重ゲート半導体デバイスおよびその製造方法

2重ゲートFinFETおよびその製造方法を提供する。FinFETは、フィン(20)の各側面に隣接して第1および第2ゲート(72、74)を有し、第1ゲートのフィンに対面する少なくとも一部分を多結晶シリコンによって形成し、第2ゲートのフィンに対面する少なくとも一部分を金属シリサイド化合物によって形成する。2個のゲートの異なった組成は、それぞれ異なった動作機能を提供し、短チャンネル効果を減少させる。  (もっと読む)

(もっと読む)

ゲート酸化物の漏れを抑えたリプレースメントゲートトランジスタ

ゲート酸化物層(12)とメタルゲート電極(60)との間に保護層(70)を形成することによって、リプレースメントゲートトランジスタに対してリーク電流を抑えた実効的なゲート酸化膜厚を得ることができ、これにより、応力を減らすことができる。実施形態においては、金属ゲート電極(60)から保護層を通じてゲート酸化物層(12)に向かうに従って濃度が低下する金属炭化物を含む非晶質炭素層(70)の保護層が形成される。方法の実施形態では、リムーバブルゲートを除去するステップ、ゲート酸化物層へ非晶質炭素層を蒸着するステップ、メタルゲート電極(60)を形成するステップ、を含み、さらにその後、メタルゲートからの金属を非晶質炭素層に拡散して金属炭化物を形成するように、高温に加熱するステップ、を含む。さらに、一実施形態では、高誘電定数を有するゲート酸化物層(82)と、金属ゲート電極(100)と基板(10)との界面において高濃度のシリコンと、を含むメタルゲートトランジスタが含まれる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜のリーク電流の低減、誘電率の向上を図る半導体装置の製造方法を提供すること。

【解決手段】本発明の一形態の半導体装置の製造方法は、半導体基板(11)上にCVD法にて酸化物絶縁膜(20)を形成する際に、前記酸化物絶縁膜の原料ガスとH2とを同時に前記半導体基板に供給する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】絶縁性の基板20上に少なくとも下部電極21、ゲート絶縁膜22、上部電極23、半導体膜24を積層させた薄膜トランジスタの製造方法において、薄膜トランジスタにおける電極の微細パターンを形成し、且つゲート電極とソース・ドレイン電極の重なりを無くすことにより高速動作を可能であって、且つ電極の厚さを薄くすることが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】電極材料14を予め基材と異なるベースフィルム11上に形成した転写フィルム10とし、前記基板20上若しくは前記基板上に形成された半導体膜上に所定のパターンにて下部電極を前記転写フィルムから転写し、前記基板と転写フィルムとを再アライメントが可能なように剥離し、ゲート絶縁膜形成後に前記再アライメントが可能なように剥離した転写フィルムを基板上に密着させ、上部電極を転写することを特徴とする。

(もっと読む)

薄膜トランジスタ及びこれを用いた液晶表示装置

【課題】生産工程が単純化された薄膜トランジスタ及びそれを用いた液晶表示装置

【解決手段】絶縁基板11上の光透過型感光性樹脂12の開口部に形成されたゲート電極13と、光透過型感光性樹脂及びゲート電極上に形成されたゲート絶縁膜14と、

ゲート絶縁膜の一部の上に形成された半導体層15、オーミックコンタクト層16及び保護膜17と、ゲート絶縁膜、半導体層、オーミックコンタクト層及び保護膜上の光透過型感光性樹脂18の2つの開口部に形成されたソース・ドレイン電極19とを備え、前記ゲート電極及びソース・ドレイン電極が、金属微粒子を含有するインクを用いたインクジェット塗布により形成された電極であることを特徴とする薄膜トランジスタ

(もっと読む)

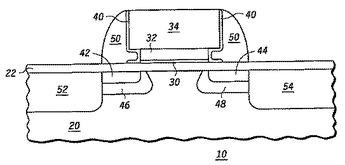

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

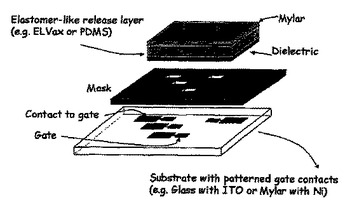

マスクを通した積層

本発明はドナー基板からレシーバ基板に材料のパターンを積層によって転写する方法である。転写された材料のパターンは、積層の際にドナーとレシーバとの間に挿入されたマスクの開口によって画定される。この技法は可撓性ポリマーレシーバ基板に適合しており、可撓性表示装置用の薄膜トランジスタを作製するのに有用である。

(もっと読む)

(もっと読む)

61 - 71 / 71

[ Back to top ]