Fターム[4M104EE20]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | その他 (71)

Fターム[4M104EE20]に分類される特許

41 - 60 / 71

ショットキーバリア量子井戸共振型トンネルトランジスタ

【課題】ショットキーバリア量子井戸のトンネルトランジスタを提供する。

【解決手段】素子構造は、一つ或は複数の導電ベースリージョン33、第一半導体バリアーリージョン、第二半導体バリアーリージョン、導電エミッタリージョン31、導電コレクタリージョン35などを含み、第一半導体バリアーリージョン或は第二半導体バリアーリージョンのサイズは100Åより小く、第一ショットキーバリアの接合を第一半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第二ショットキーバリアの接合を第二半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第三ショットキーバリアの接合を導電エミッタリージョンと第一半導体バリアーリージョンのインターフェイスで生じ、第四ショットキーバリアの接合を導電コレクタリージョンと第二半導体バリアーリージョンのインターフェイスで生じる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】良好な形状のsingle metal/dual high−k構造を形成し、nMOS、pMOSそれぞれに適したフラットバンド電圧を得ることができる半導体装置を得ること。

【解決手段】本発明の一実施形態における半導体装置100は、第1導電型のMOSFET10と、第2導電型のMOSFET20を有する。第1および第2導電型のMOSFET10,20は、半導体基板1上に形成された第1の絶縁膜2と、第1の絶縁膜2上に形成され、第1の絶縁膜2よりも誘電率の高い絶縁材料からなる第2の絶縁膜4と、第2の絶縁膜4上に形成され、第2の絶縁膜4に拡散して仕事関数を制御する材料を含むメタル層5を下層に有するゲート電極7と、を備える。また、第2導電型のMOSFET20は、第1の絶縁膜2と第2の絶縁膜4との間に形成され、仕事関数を制御する材料が第1の絶縁膜2界面に拡散するのを防止する拡散防止膜3をさらに備える。

(もっと読む)

半導体装置およびその製造方法

【課題】エレクトロマイグレイション耐性の高いエアブリッジ配線を具備した半導体装置及びその製造方法を提供すること。

【解決手段】第1の配線と、第1の配線から空間によって隔てられた状態で、前記第1の配線の上を横切る第2の配線と、前記第1及び第2の配線に接続された半導体素子を具備し、前記第2の配線は、下から順に、タンタル層、タンタルナイトライド層、及び金層が積層されて形成されていること。

(もっと読む)

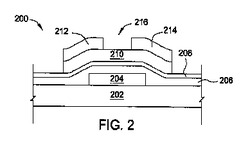

薄膜トランジスタ用のハイブリッド誘電体材料

有機ケイ酸塩ガラス(OSG)を絶縁体材料として用いて薄層トランジスタが製造される。有機ケイ酸塩ガラスは、シロキサンと酸素からプラズマ化学気相成長法によって被着されたSiO2−シリコーンハイブリッド材料であってよい。これらのハイブリッド材料は、ゲート誘電体として、サビング層としておよび/またはバックチャネル不動態化層として利用されてよい。トランジスタは、従来のあらゆるTFT幾何形状で製造されてよい。  (もっと読む)

(もっと読む)

高性能金属酸化物及び金属酸窒化物薄膜トランジスタを作るためのゲート誘電体の処理

本発明の実施形態は、概して、TFT及びそれらを製造するための方法を含む。TFTのゲート誘電体層は、TFTの閾値電圧に影響を与えることができる。アクティブチャネル材料を堆積する前にゲート誘電体層を処理することによって、閾値電圧を改善することができる。ゲート誘電体を処理する1つの方法は、N2Oガスにゲート誘電体層を曝露することを含む。ゲート誘電体を処理する別の方法は、N2Oプラズマにゲート誘電体層を曝露することを含む。シリコンベースのTFT用にはゲート誘電体として実用的ではないが、酸化珪素も金属酸化物TFTで使用すると、閾値電圧を改善することができる。ゲート誘電体を処理する、及び/又は、酸化珪素を使用することによって、TFTの閾値電圧を改善することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置表面に堆積された犠牲層を短時間に除去することができ、製造歩留りの向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート電極1、ドレイン電極2およびソース電極3を有する電界効果トランジスタ4と、ゲート電極1、ドレイン電極2およびソース電極3を被覆し、半導体基板4A上に設けられた中空保護膜5とを備え、中空保護膜5は、第1のキャップ層7と、第1のキャップ層7上に配置された第2のキャップ層10と、ドレイン電極2およびソース電極3の上方の第1のキャップ層7の位置に形成された複数の開口部12と、開口部12を第2のキャップ層10により封止する封止部12Aとを有し、開口部12を介して酸素プラズマを供給して犠牲層6をアッシング除去する半導体装置およびその製造方法。

(もっと読む)

DMOSトランジスタ

【課題】DMOSトランジスタのオン抵抗を低減するとともに、静電破壊強度の劣化を防止する。

【解決手段】DMOSトランジスタのソース層5の端部は、ゲート電極7の内側のコーナー部7Aから後退して配置されている。また、ソース層5上のシリサイド層11をソース層5の端部から外に延在させないようにした。即ち、ソース層5の表面にはシリサイド層11を形成するが、ソース層5とゲート電極7の内側のコーナー部7Aの間に露出したボディ層4の表面については、シリサイド層11を形成していない。これにより、電流集中が無くなり、電流はDMOSトランジスタの全体にほぼ均一に流れるようになるため、静電破壊強度を向上させることができる。

(もっと読む)

高ストレス薄膜の成膜方法及び半導体集積回路装置の製造方法

【課題】プロセス条件で与えられるストレス以上に大きなストレスを薄膜に与えることが可能な高ストレス薄膜の成膜方法を提供すること。

【解決手段】水素を含む成膜原料ガスをチャンバー内に供給し、水素が取り込まれた薄膜を半導体基板上に成膜する工程(ステップ1)と、薄膜から水素を離脱させる物質を含む水素離脱ガスを前記チャンバーにパルス的に供給しながら薄膜から水素を離脱させる工程(ステップ2、ステップ11及び12)と、を具備する。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜にHfを含むMOSトランジスタの特性のばらつきを抑制するために、Hf密度の面内ばらつきを少なくすることが必要である。

【解決手段】 半導体基板上に、熱酸化により酸化シリコンまたは酸窒化シリコンを含む絶縁膜(40)を形成する。絶縁膜の上にHfを含むガス(45)を供給して、絶縁膜の上にHf原子(41)を堆積させる。Hf原子が堆積している絶縁膜を、酸素雰囲気中(46)で熱処理する。酸素雰囲気中で熱処理した後、絶縁膜の上に、ゲート電極(50P,50N)を形成する。ゲート電極の両側に、ソース領域及びドレイン領域(52P,52N)を形成する。

(もっと読む)

トランジスタ、半導体装置、半導体装置の製造方法

【課題】 占有面積を拡大することなく特性バラツキの抑制を可能にする半導体装置及びその製造方法を提供する。

【解決手段】 低濃度P型の半導体基板1の上層にゲート酸化膜3を形成した後、ゲート酸化膜3上層にP型のゲート電極4を形成する。その後、ゲート酸化膜3及びゲート電極4をマスクとしてN型の不純物イオンを注入することで、N型のソース・ドレイン拡散領域6を複数離間形成する。その後、半導体基板1及びゲート電極4の上層に層間絶縁膜7を形成した後、各ソース・ドレイン拡散領域6及びゲート電極4夫々との電気的接続を確保する複数のコンタクトプラグ8を形成する。その後、所望の閾値電圧となるよう、コンタクトプラグ8を介してソース・ドレイン拡散領域6とゲート電極4の間に所定の高電圧を印加してゲート酸化膜3内に正電荷を注入する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型MOSFETの特性を劣化させることなく、pチャネル型MOSFETの閾値電圧を低減した相補型半導体装置する。

【解決手段】相補型半導体装置の製造方法が、シリコン基板を準備する工程と、ゲート絶縁膜を形成する工程と、ゲート絶縁膜を覆うようにAl含有膜を形成する工程と、nチャネル型MOSFET形成領域の上のAl含有膜を、過酸化水素水を用いて選択的に除去する工程と、シリコン基板の上にゲート導電層を形成する工程と、ゲート絶縁膜、Al含有膜、およびゲート導電層をエッチングして、ゲート絶縁膜、Al含有膜、およびゲート導電層を含むpチャネル型MOSFETのゲート電極と、ゲート絶縁膜、およびゲート導電層を含むnチャネル型MOSFETのゲート電極とを形成する工程と、pチャネル型MOSFETのゲート電極において、Al含有膜のAl元素をゲート絶縁膜中に拡散させる工程とを含む。

(もっと読む)

ショットキーバリアダイオードおよびその製造方法

【課題】フィールドプレート構造により逆方向耐電圧の向上したショットキーバリアダイオードを提供する。

【解決手段】このショットキーバリアダイオード1は、GaN自立基板2の表面2a上に形成された、GaNエピタキシャル層3を備える。また、GaNエピタキシャル層3の表面3a上に形成され、開口部が形成されている絶縁層4を備える。絶縁層4中の水素濃度は、3.8×1022cm-3未満である。また、電極5を備える。電極5は、開口部の内部に、GaNエピタキシャル層3に接触するように形成されたショットキー電極と、ショットキー電極に接続するとともに、絶縁層4に重なるように形成された、フィールドプレート電極とによって、構成されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明の課題は、電極や配線の周囲に空間部を形成するに際し、電極材料や配線材料が耐フッ酸性がない材料であっても適用でき、かつ有機汚染の心配のない半導体装置の製造方法を提供することである。

【解決手段】本発明の半導体装置の製造方法は、ゲート電極21aの周囲を昇華性を有する材料としての塩化アルミニウム膜22aからなる犠牲膜で被覆し、その犠牲膜の周囲を外殻層としてのSiN膜23で被覆し、外殻層に設けた開口部24を通して犠牲膜をその昇華温度以上に加熱し除去して、ゲート電極21aの周囲に空間部25を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法およびそれにより得られた半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

【解決手段】本発明は、半導体材料と金属の合金から形成され、合金の仕事関数を変調させる仕事関数変調元素を含む完全にシリサイド化されたゲート電極(4)と、完全にシリサイド化されたゲート電極(4)に接触した誘電体(3)とを含む半導体装置(1)を提供する。完全にシリサイド化された電極と直接接触する誘電体(3)の少なくとも一部は、仕事関数変調元素が誘電体(3)中に注入され、および/または誘電体(3)に向かって拡散するのを実質的に防止するストップ金属を含む。本発明は、また、そのような半導体装置(1)を形成する方法を提供する。

(もっと読む)

41 - 60 / 71

[ Back to top ]