Fターム[4M104EE20]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | その他 (71)

Fターム[4M104EE20]に分類される特許

21 - 40 / 71

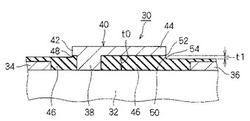

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

有機誘電体を有する有機電界効果トランジスタ

【課題】有機トランジスタの大電流および高速スイッチングを達成するために、ゲート絶縁体材料とその製造方法を提供する。

【解決手段】基板1上に、溶液から有機半導体層3を堆積させる工程、および溶液から低誘電率絶縁材料の層を堆積させて、その低誘電率絶縁材料が有機半導体層3と接触するようにゲート絶縁体2の少なくとも一部を形成する工程を含む有機トランジスタを形成する。低誘電率絶縁材料の比誘電率が1.1から3.0未満までである。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】基板の表面粗度によらず膜表面が平坦であり、信頼性が高く、製造コストを低減させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】可撓性のプラスチック基板10上に、ゲート電極11、ゲート絶縁層12、半導体活性層13、ソース電極14、及びドレイン電極15を順次形成するボトムゲート型薄膜トランジスタ1の製造方法である。ゲート絶縁層12は、プラスチック基板10上に下部層12aと該下部層12a上に積層された少なくとも一層以上の上部層12bとがこの順で形成されてなり、下部層12aは、炭素含有酸化シリコンを含む材料からなり、下部層12aの炭素濃度が、15atm%以上40atm%以下となるように真空紫外光CVD法により形成される。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】絶縁性が高く、かつ均一な膜厚を有するゲート絶縁膜を効率よく形成することができる電界効果型トランジスタの製造方法、及び該電界効果型トランジスタの製造方法により製造され、安定した特性を有する高性能な電界効果型トランジスタの提供。

【解決手段】前記第一の基材上にゲート電極を形成するゲート電極形成工程と、第二の基材上にゲート絶縁膜形成用樹脂溶液を塗布し、ゲート絶縁膜を形成する塗布工程と、前記ゲート絶縁膜表面の流動性が消失するまで乾燥する乾燥工程と、前記ゲート電極と、前記ゲート絶縁膜表面とを接触させて接触体を形成する接触工程と、前記接触体に対し、ゲート絶縁膜形成用樹脂のガラス転移温度以上の熱を加える加熱工程と、前記接触体から前記第二の基材を剥離し、第一の基材上にゲート絶縁膜を形成する剥離工程とを少なくとも含む電界効果型トランジスタの製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

ショットキーダイオードと製造方法と製造装置

【課題】不純物高濃度層2と不純物低濃度層4が積層されており、不純物低濃度層4内に欠陥6a,6b等が形成されている半導体基板5から、リーク電流が流れにくいショットキーダイオード15を製造する。

【解決手段】 不純物低濃度層4に欠陥6a,6bが存在する部位にのみ、絶縁層8a,8bを形成し、その上にショットキー電極12を形成する。欠陥6a,6bを除去しないことから簡単な製造工程を採用できる。絶縁層8a,8bで絶縁することから、欠陥6a,6bがあってもリーク電流が流れない。特性のすぐれたショットキーダイオード15を安価に製造することが可能となる。

(もっと読む)

PMOSデバイスのゲートスタックのしきい値電圧を調整する方法

【課題】本発明は、半導体基板上にゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法であって、ゲートスタックのVT値を容易に調整することができる方法を提供する。

【解決手段】ゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法は、第1の電気陰性度を有する金属酸化物または半金属酸化物であるゲート誘電体層を半導体基板上に形成するステップと、第2の電気陰性度を有する金属酸化物または半金属酸化物である誘電体VT調整層を形成するステップと、ゲート誘電体層およびVT調整層の上にゲート電極を形成するステップと、を含み、前記ゲートスタックの実効仕事関数が、誘電体VT調整層の厚さおよび組成を調整することによって所望の値に調整され、第2の電気陰性度が、第1の電気陰性度およびAl2O3のいずれよりも高い。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

積層体、その製造方法、積層体を備える薄膜トランジスタ、および積層体を備えるプリント配線基板

【課題】基板とめっき層との密着性に優れた積層体、その製造方法、積層体を備える薄膜トランジスタ、積層体を備えるプリント配線基板を提供する。

【解決手段】

積層体1では、基板2上にシリカ層3および有機層4を介し、めっき層5が形成されている。シリカ層3はポリシラザンを前駆体として形成されているので、基板2との密着性が良好で、上面に無数の微細な凹凸が存在するシリカ層3が形成される。有機層4は、シリカ層3の上面の凹凸によって発現するアンカー効果により、シリカ層3と強固に結合する。また、有機層4の上面には、シリカ層3の上面の無数の微細な凹凸を反映して凹凸が形成されるので、めっき層5と有機層4とは、化学的もしくは電気的な結合に加え、アンカー効果により強固に結合される。よって、シリカ層3および有機層4を介して基板2上に形成されるめっき層5の基板2に対する密着性を向上できる。

(もっと読む)

半導体装置の製造方法。

【課題】 金属膜やHigh−k膜の膜質の劣化を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 第1の薄膜2上に、第1の薄膜2とは異なる第2の薄膜3を形成し、第2の薄膜3上に、第2の薄膜3とは異なる膜からなる犠牲膜5を形成し、犠牲膜5をエッチングにより所望の間隔を持つパターンに加工し、犠牲膜パターンを形成し、シリコン含有プリカーサー、酸素含有ガスを基板上に間欠的に供給して、犠牲膜パターンにシリコン酸化膜6を被覆し、シリコン酸化膜6をエッチングにより犠牲膜5の側壁上に側壁スペーサー6aを形成し、犠牲膜5を除去し、側壁スペーサー6aをマスクとして用いて第1の薄膜2および第2の薄膜3を加工する。

(もっと読む)

絶縁膜の形成方法、半導体装置の製造方法および半導体装置の製造装置

【課題】半導体を高濃度の硝酸の蒸気および/または溶液に接触させる処理で、短時間に、前記半導体表面に高品質の二酸化シリコン膜の生成を実現する。

【解決手段】被処理用シリコンを濃度70wt%の硝酸の加熱溶液から発生させた蒸気中で数秒、および/またはその加熱硝酸溶液で10分程度接触させて、前記シリコンの表面に膜厚約1.39nmの酸化膜を形成した。この被膜は、リーク電流性能が(1V印加時)0.6A/cm2であり、同膜厚換算のオキシナイトライド膜の以下のレベルを実現できた。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(110,114又は122)のゲート誘電体層(500,566又は700)は、垂直濃度分布を有する窒素を含有している。

【解決手段】 該垂直濃度分布は、上側に位置しているゲート電極(502,568又は702)内のボロンが該ゲート誘電体層を介して下側のチャンネルゾーン(484,554又は684)内に著しく浸透することを防止し同時に該ゲート誘電体層から下側に存在する半導体ボディ内への窒素の移動を回避するために特別に調整されている。該チャンネルゾーン内の不所望のボロンから及び該半導体ボディにおける不所望の窒素から発生する場合がある損傷は実質的に回避される。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の厚さが異なるトランジスタを有する半導体装置の製造歩留まりを向上させる。

【解決手段】シリコン基板1上に高耐圧絶縁膜IH1を形成した後、高耐圧絶縁膜IH1の表面を削って膜厚を薄くし、高耐圧絶縁膜IH1と隣接するようにして中耐圧絶縁膜IM1を形成する。高耐圧絶縁膜IH1は、熱酸化法によって、シリコン基板1の主面より内側から外側に至るようにして形成し、中耐圧絶縁膜IM1は高耐圧絶縁膜IH1より薄くなるようにして形成する。高耐圧絶縁膜IH1は高耐圧MISトランジスタのゲート絶縁膜として、中耐圧絶縁膜IM1は中耐圧MISトランジスタのゲート絶縁膜として形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧に対応しつつ小型化を容易に行い、昇圧及び降圧回路等の種々の用途に使用することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板に形成された第1のウエル及び第2のウエルと、第1のウエルに形成された複数の高耐圧MOSトランジスタと、第2のウエルに形成された低耐圧MOSトランジスタと、を有し、複数の高耐圧MOSトランジスタが、低耐圧MOSトランジスタのゲート絶縁膜の膜厚よりも厚いゲート絶縁膜を備える第1の高耐圧MOSトランジスタと、第1の高耐圧MOSトランジスタのゲート絶縁膜の膜厚よりも薄いゲート絶縁膜を備える第2の高耐圧MOSトランジスタと、からなること。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程によりアモルファス化される半導体基板表面が、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を著しく低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に緩衝膜を設けることで、高濃度不純物のイオン注入を行っても、この領域の半導体基板表面がアモルファス化することを防ぐことができる。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】優れた電気伝導特性を安定して示すカーボンナノチューブ電界効果トランジスタを再現性よく製造することができる方法を提供すること。

【解決手段】まず、LOCOS法によりシリコン基板のコンタクト領域に酸化シリコン膜を形成する。次いで、シリコン基板のチャネル領域に、コンタクト領域の酸化シリコン膜よりも薄い絶縁膜を形成する。次いで、シリコン基板上にチャネルとなるカーボンナノチューブを配置した後、カーボンナノチューブを保護膜で被覆する。最後に、ソース電極およびドレイン電極をそれぞれ形成して、ソース電極およびドレイン電極をそれぞれカーボンナノチューブに電気的に接続させる。このようにして製造された電界効果トランジスタは、チャネルとなるカーボンナノチューブが汚染されていないため、優れた電気伝導特性を安定して示す。

(もっと読む)

半導体装置及びその製造方法

【課題】容易に製造することができ、トランジスタの性能を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2及びゲート電極3が形成されている。半導体基板1の表面の、平面視でゲート電極3を挟む位置に2個の不純物拡散層4が形成されている。2個の不純物拡散層4の表面に、ゲート絶縁膜2と半導体基板1との界面より低くなった掘り込み部6が設けられている。更に、半導体基板1のゲート絶縁膜2下の領域(チャネル)に応力を付加する応力付加膜が、少なくとも掘り込み部6内に位置している。

(もっと読む)

21 - 40 / 71

[ Back to top ]